– 2 –

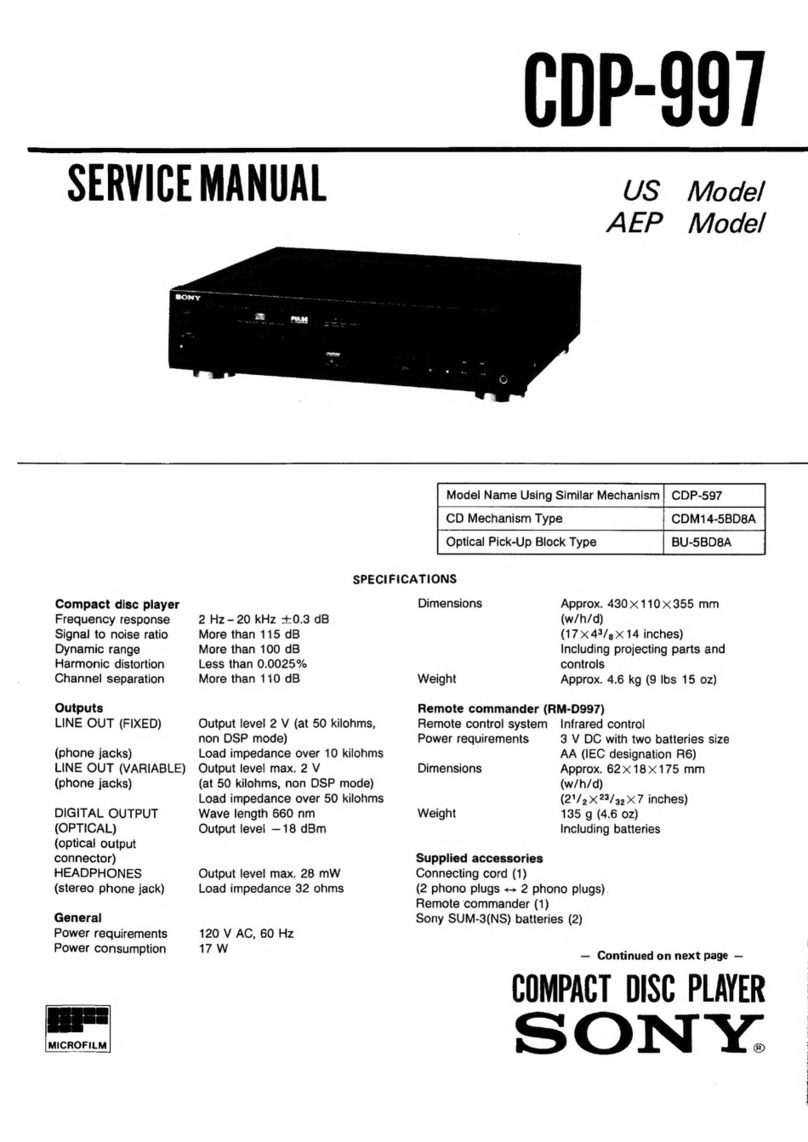

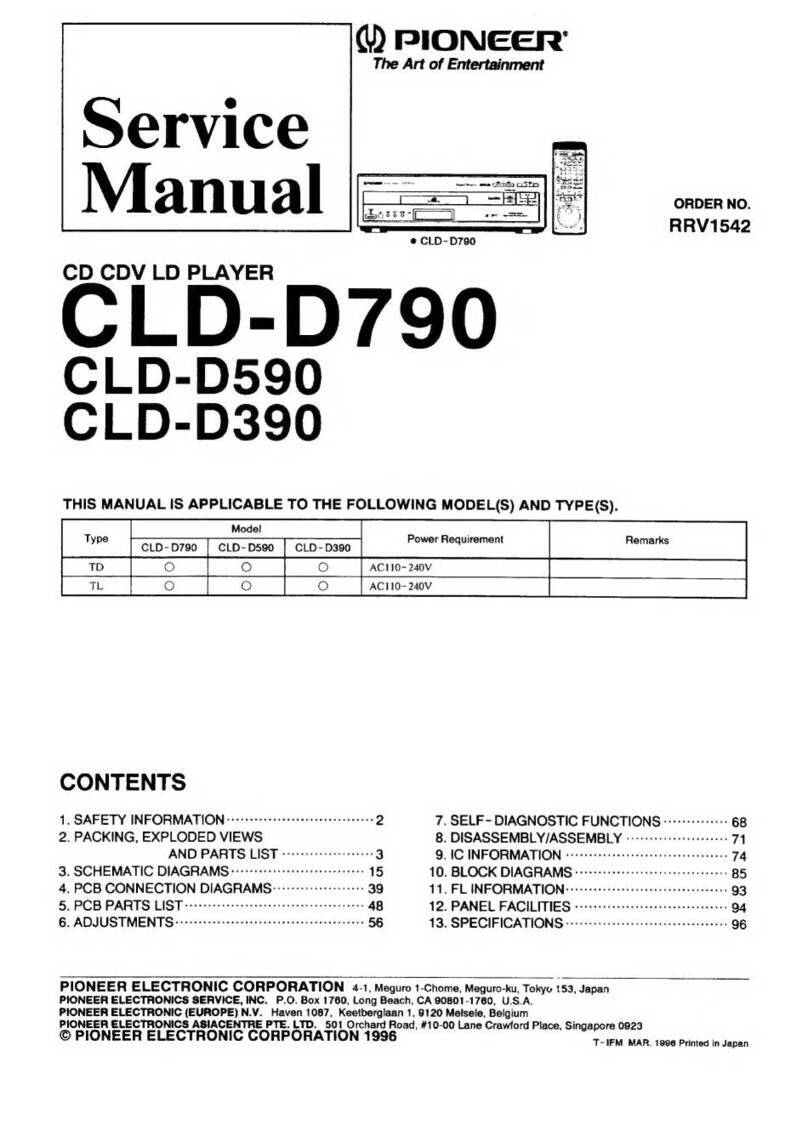

Specifications ........................................................................... 1

1. SERVICING NOTE....................................................... 3

2. GENERAL

Location and Function of Controls .................................... 4

3. DISASSEMBLY

3-1. Cabinet (Lower) Sub ASSY ....................................... 6

3-2. Lid Sub ASSY, Switch Unit ........................................ 6

3-3. MPEG Board .............................................................. 7

3-4. MD ASSY, IR Board .................................................. 7

3-5. Main Board ................................................................. 8

3-6.Turn Table Motor ASSY (Spindle) (M902),

Optical Pick-up (DAX-01A2),

Sled Motor ASSY (M901) .......................................... 8

4. SERVICE MODE (TEST MODE)

4-1. How to Enter the Test Mode ....................................... 9

4-2. How to Release the Test Mode ................................... 9

4-3. Each Key Function in Test Mode ............................... 9

5. ELECTRICAL ADJUSTMENTS

5-1. Precautions for Adjustment ...................................... 10

5-2. Before Beginning Adjustment .................................. 10

5-3. Tracking Balance Check ........................................... 10

5-4. Focus Bias Check ......................................................11

6. DIAGRAMS

6-1. Explanation of IC Terminals..................................... 12

6-2. Block Diagram.......................................................... 19

6-3. Printed Wiring Boards (Main Section) ..................... 23

6-4. Schematic Diagram (Main Section) ......................... 27

6-5. Schematic Diagram (MPEG Section)....................... 34

6-6. Printed Wiring Boards (MPEG Section) .................. 37

7. EXPLODED VIEWS

7-1. Cabinet (Upper) Section ........................................... 42

7-2. Cabinet (Lower) Section........................................... 43

7-3. Optical Pick-up Section (CDM-2901ABA) ............. 44

8. ELECTRICAL PARTS LIST ................................45

SAFETY-RELATED COMPONENT WARNING!!

COMPONENTS IDENTIFIED BY MARK !OR DOTTED LINEWITH

MARK !ON THE SCHEMATIC DIAGRAMS AND INTHE PARTS

LIST ARE CRITICALTO SAFE OPERATION.

REPLACE THESE COMPONENTS WITH SONY PARTS WHOSE

PART NUMBERS APPEAR AS SHOWN INTHIS MANUAL OR IN

SUPPLEMENTS PUBLISHED BY SONY.

Flexible Circuit Board Repairing

• Keep the temperature of the soldering iron around 270°C during

repairing.

• Do not touch the soldering iron on the same conductor of the

circuit board (within 3 times).

• Be careful not to apply force on the conductor when soldering or

unsoldering.

Notes on chip component replacement

• Never reuse a disconnected chip component.

• Notice that the minus side of a tantalum capacitor may be dam-

aged by heat.

TABLE OF CONTENTS

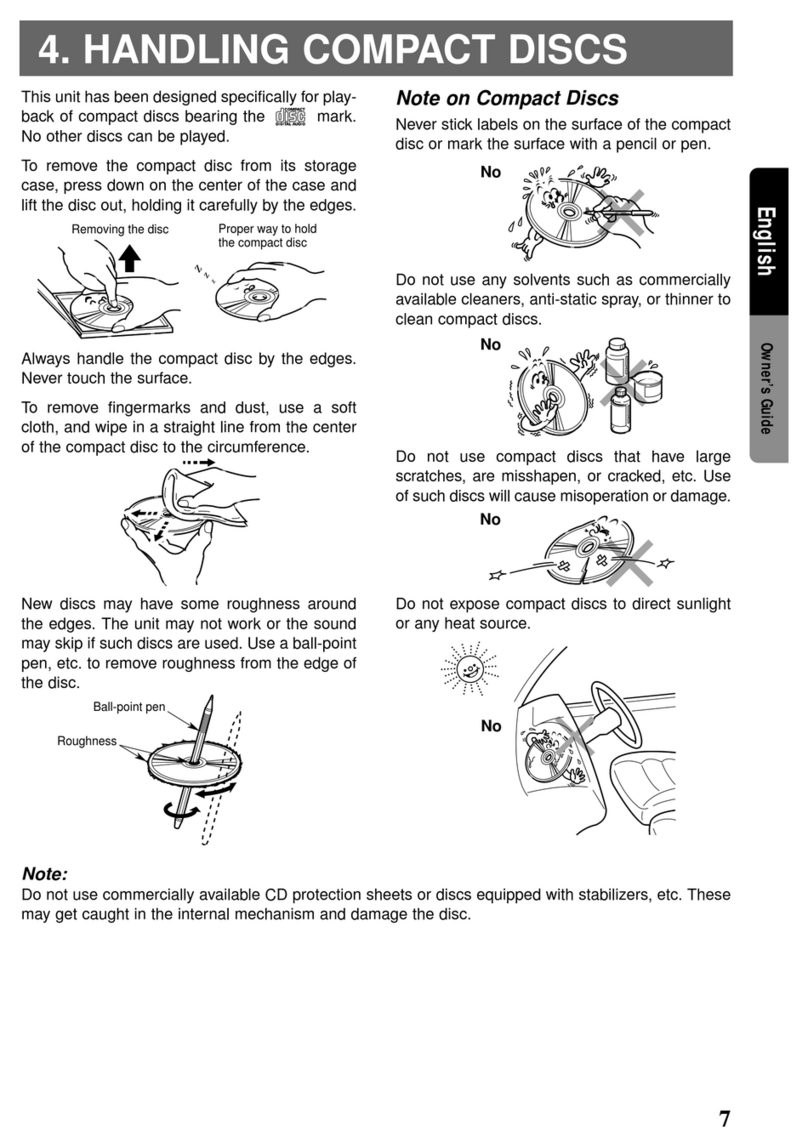

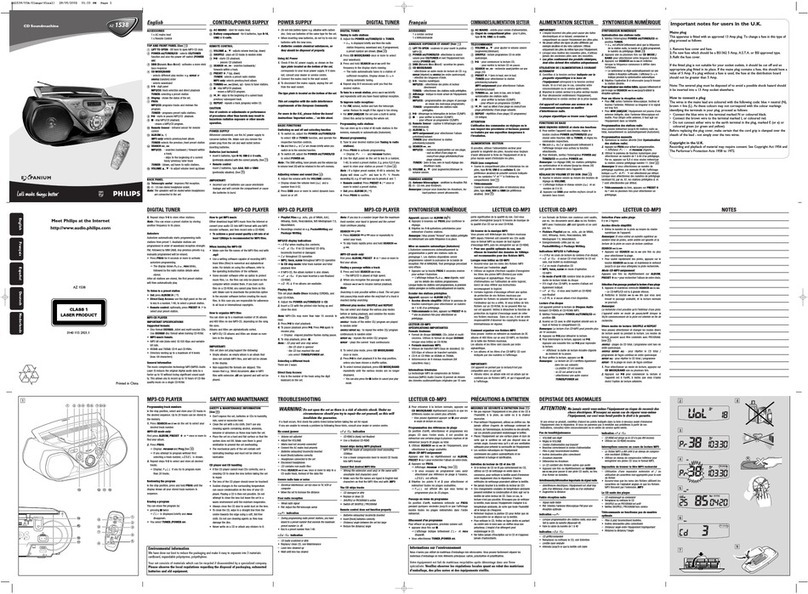

This Compact Disc player is

classified as a CLASS 1 LASER

product.

The CLASS 1 LASER

PRODUCT label is located on the

bottom exterior.

CAUTION

Use of controls or adjustments or performance of procedures other than

those specified herein may result in hazardous radiation exposure.

DANGER

Invisible laser radiation when open and interlock failed or defeated.

Avoid direct exposure to beam.