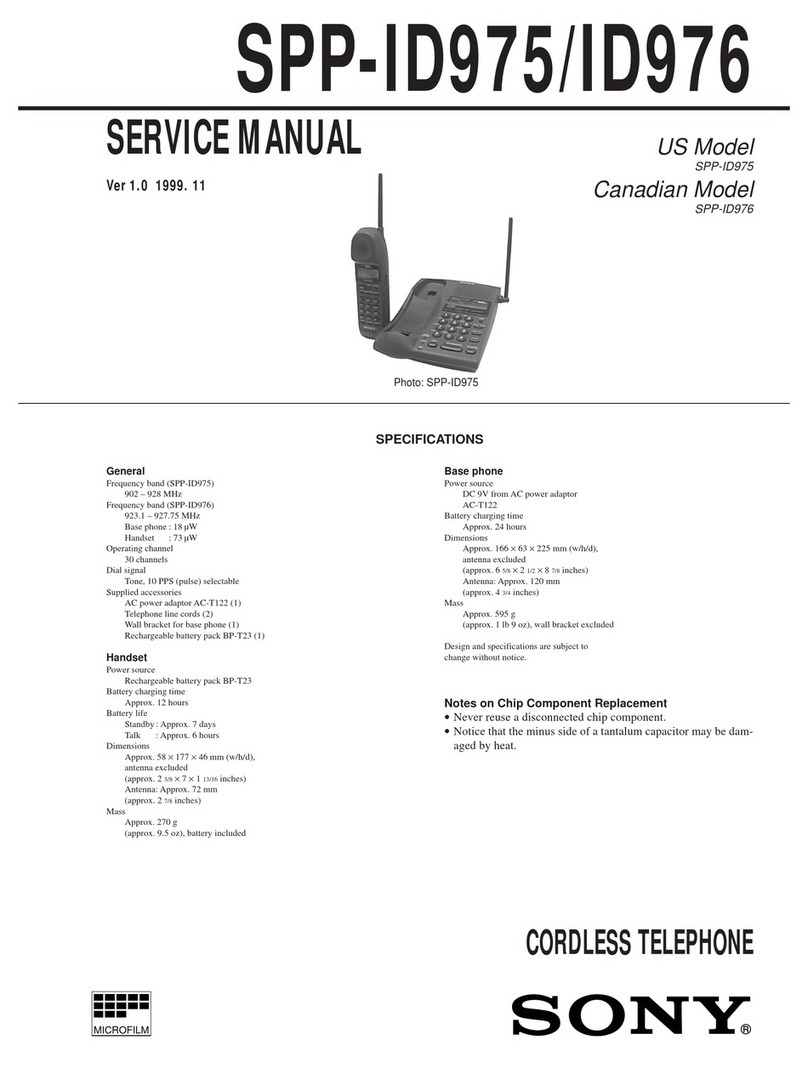

Vcc

VO1

BIAS

CIRCUIT

2

1

RLO1

TLO1

TLI1

RLI1

CPR

GND

RXO

RXI

RLI2

RLO2

TLO2

TLI2

CPT

VB

FI

4

VCC

3

CD

FO

+

–

+

–

59

8

7

6

HTI

TXO

TXI

HTO+

HTO–

10 12

11 14

13

27

28 2526 24 20

21

22

23 19 17

18 15

16

MUT

MCO

MCI

CT

VLC

VR

VCC

HYBRID

AMP 2 HYBRID

AMP 1

MIC

AMP

VREF

+

–

VR

FILTER

AMP

COMPARATOR

AGC

BACKGROUND

NOISE

DETECTOR

VR

LEVEL

DETECTOR

LEVEL

DETECTOR COMPARATOR

ATTENUATOR

CONTROL BLOCK

BACKGROUND

NOISE

DETECTOR

DIAL

TONE

DETECTOR

LEVEL

DETECTOR

LEVEL

DETECTOR

RX

ATTEN-

UATOR

TX

ATTENUATOR

12 3 45 6 7 8

9

10

16

15

14

13

12

11

MODULATOR

& FILTER

CONTROL

REGISTOR

16 BIT

REGISTOR

16 BIT

REGISTOR MODULATOR

& FILTER

1719 182021222324

28

29

30

27

26

25

31

32

VOXRNT

VOXSND

AVDD

LINE-IN

AVSS

MICIN

RBIAS

NC

REFCNTL

XCLKO

NC

ICLK

FRAM

SPKPO

SPKMO

LINEO

RESETB

MCLK

DVSS

DATAI

DATAO

DVDD

NC

NC

NC

NC

NC

NC

NC

AGND

VREF

MICBIAS

8

VCC

7

TEST INPUT

6

SCL

5

SDA

1

NC

2

NC

3

NC

4

VSS

START

STOP

LOGIC

CONTROL

LOGIC

START CYCLE H.V. GENERATION

TIMING

& CONTROL

E PROM

32 x 32

2

32

XDEC

INC

LOAD

5

R/W

PIN

2

8D

OUT

CK

32

WORD

ADDRESS

COUNTER

YDEC

D

OUT

ACK

DATA REGISTER

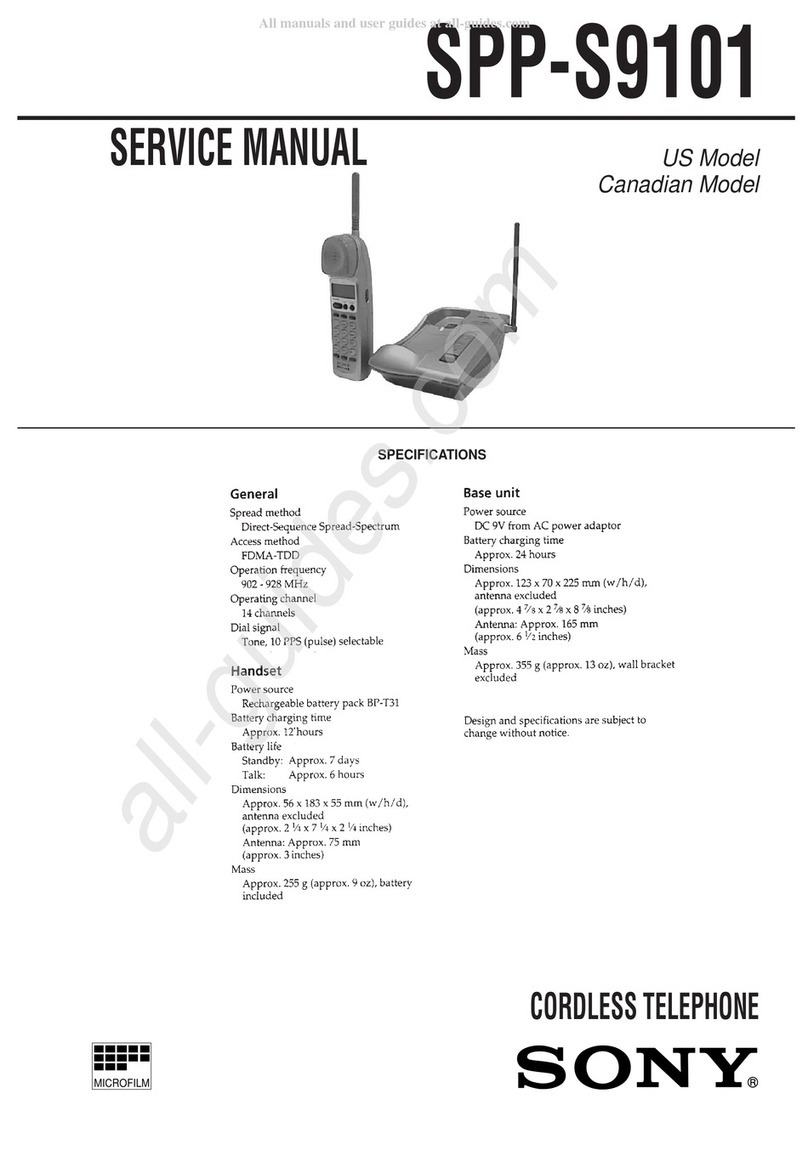

•HAND MAIN BOARD IC501 M7012-11 (ASIC)

Pin No. Pin Name I/O Function

1 KEYPADB5 O Key output terminal Not used (open)

2D0I

Selection input of the model Fixed at “L” in this set

3, 4 D1, D2 I/O Not used (open)

5D3I

Selection input of the test mode Not used (open)

6 to 9 D4 to D7 O Serial data output to the liquid crystal display unit (LCD501)

10 to 15 KEYPADI0 to

KEYPADI5 IKey return signal input from the key matrix “L” input when key pressing

16 VSSC — Ground terminal (for core)

17 VDDC — Power supply terminal (+5V) (for core)

18 VDDP — Power supply terminal (+5V) (for pad)

19 VSSC — Ground terminal (for core)

20 OSCI I Sub system clock input terminal (32.768 kHz) Not used (open)

21 OSCO O Sub system clock output terminal (32.768 kHz) Not used (open)

22 KEYPADB3 OKey send signal output to the key matrix

23 KEYPADB4 OKey output terminal Not used (open)

24 CDCDATAI I Transmit data input from the CODEC (IC401)

25 CDCDATAO O Receive data output to the CODEC (IC401)

26 CDCMCLK O Master clock signal output to the CODEC (IC401)

27 RESETO O Reset signal output to the CODEC (IC401) “L”: reset

28 CDCICLK O Interface clock signal output to the CODEC (IC401)

29 VDDP — Power supply terminal (+5V) (for pad)

30 VSSP — Ground terminal (for pad)

31 KEYPADB2 O Key send signal output to the key matrix

32 CDCFRAME O Frame output to the CODEC (IC401)

33 ARTI I ART input from the base unit

34 ARTO O ART output terminal Not used (open)

35, 36 KEYPADB1,

KEYPADB0 OKey send signal output to the key matrix

37 GPIOB7 O Not used (open)

38 VDDP — Power supply terminal (+5V) (for pad)

39 LCDCS O Chip select signal output to the liquid crystal display unit (LCD501) “L” active

40 VDDC — Power supply terminal (+5V) (for core)

41 VSSC — Ground terminal (for core)

42 TEST I Setting terminal for the test mode “L”: test mode Normally: fixed at “H”

43 LNAATN O LNA gain selection signal output to the RF unit “H”: low gain

44 RXEN O RX system enable signal output to the RF unit “H”: enable

45 VDDA — Power supply terminal (+5V) (for analog)

46 VSSA — Ground terminal (for analog)

47 VDDA — Power supply terminal (+5V) (for analog)

48 VSSA — Ground terminal (for analog)

49 TXDATA O Transmit data output to the RF unit

50 VRP O Analog reference voltage output terminal

51 RXIP I Receive data (I positive) input from the RF unit

52 RXIN I Receive data (I negative) input from the RF unit

53 RXQP I Receive data (Q positive) input from the RF unit

54 RXQN I Receive data (Q negative) input from the RF unit

55 NC — Not used (open)

7-13. IC PIN FUNCTION DESCRIPTION