Step Technica MKY44 Series User manual

---22/1egaP---

DS_MKY44IO32A_V1.7E

CUnet Family

MKY44-IO32A DATA SHEET

https://www.steptechnica.com/

MKY44 Series CUnet-Compliant Intelligent Slave ICs

16 bits PWM 2ch 24 bits UP/DOWN Counter 2ch

8 bits DI 8 bits DO

Model : MKY44-IO32A

[DIO mode]

DIO : 32 bits (I/O can be set in units of 8 bits)

:

• Sampling interval : 100 µs to 1 s (Default value: 100 µs)

• Filtration degree : 1 layer, 2 layers, 4 layers, 8 layers, or 10 layers

(Default setting: 10 layers)

Power voltage : 3.3 V

Power consumption : 20 mA

Temperature range : -40 to +85 °C

Package : 64-pin TQFP (0.5 mm pitch 10 mm ×10 mm)

ST44SW : Required

[PWM and Up/Down counter mode]

16-bit PWM : 2ch (PWM frequency can be changed)

24-bit Up/Down counter input

: 2ch

DIO : 8 bits

:

• Sampling interval : 100µs to 1 s (Default value: 100 µs)

• Filtration degree : 1 layer, 2 layers, 4 layers, 8 layers, or 10 layers

(Default setting: 10 layers)

DO : 8 bits

Power voltage : 3.3 V

Power consumption : 20 mA

Temperature range : -40 to +85 °C

Package : 64-pin TQFP (0.5 mm pitch 10 mm ×10 mm)

ST44SW : Required

Applications

Industrial devices Medical devices Measurement devices

Power wire monitoring Process control

Overview

The MKY44-IO32A is a CUnet station IC with intelligent DIO control function. The MKY44-IO32A has the two modes of DIO

mode and PWM & Up/Down counter mode. Switching between the modes is achieved through hardware pin settings. Because a

The DOSA

(Data Output Station Address) pin of the ST44SW connected to the MKY44-IO32A is used to specify the network address of the

Furthermore, this control data is automatically copied to all CUnet ICs through CUnet communication (memory sharing). Input

data (DI) is automatically input to the MKY44-IO32A's own memory and automatically copied to all CUnet ICs through CUnet

communication (memory sharing). Existing users of CUnet can ge t to

their networks in DIO mode. In addition, PWM, Up/Down counter mode provides an easy method for counter input and PWM output

control. New users have the opportunity for easy, intelligent DIO control without load on the CPU.

--- Page 2 / 22 ---

CUnet Family MKY44-IO32A

■Digital Filter (Common to DIO Mode, PWM and Up/Down Counter Mode)

<RXFDQVHWWKHLQSXWRIWKH0.<,2$WRJRWKURXJKXSWRGLJLWDO¿OWHUVE\WXUQLQJ³21´WKH')RQELWRI',36:

7KHIDFWRU\GHIDXOWVDPSOHLQWHUYDORIWKH0.<,2$LVȝV7KXVVLJQDOVZLWKVPDOOFKDQJHVWKDWDUHZLWKLQPVZLOOEH

UHPRYHG

--- Page 3 / 22 ---

CUnet Family MKY44-IO32A

■DIO Mode General-Purpose I/O Pin Setting List

6HWWKH,2RIJHQHUDOSXUSRVH,2SLQVLQ',2PRGHXVLQJSLQV,26,26DQG,26:$37KH0.<,2$UHDGVWKHVHVHWWLQJ

VWDWHVZKHQUHWXUQLQJIURPDKDUGZDUHUHVHW

Pin name Setting level (IOSWAP = High: Normal) Pin name Setting level (IOSWAP = Low)

,26 +LJK +LJK /RZ /RZ ,26 +LJK +LJK /RZ /RZ

,26 +LJK /RZ +LJK /RZ ,26 +LJK /RZ +LJK /RZ

Pin name I/O Pin name I/O

,R 'L 'L 'L 'L ,R 'R 'R 'R 'R

,R 'L 'L 'L 'L ,R 'R 'R 'R 'R

,R Di2 Di2 Di2 Di2 ,R Do2 Do2 Do2 Do2

,R Di3 Di3 Di3 Di3 ,R Do3 Do3 Do3 Do3

,R Di4 Di4 Di4 Di4 ,R Do4 Do4 Do4 Do4

,R 'L 'L 'L 'L ,R 'R 'R 'R 'R

,R 'L 'L 'L 'L ,R 'R 'R 'R 'R

,R 'L 'L 'L 'L ,R 'R 'R 'R 'R

,R Do8 Di8 Di8 Di8 ,R Di8 Do8 Do8 Do8

,R Do9 Di9 Di9 Di9 ,R Di9 Do9 Do9 Do9

,R 'R 'L 'L 'L ,R 'L 'R 'R 'R

,R 'R 'L 'L 'L ,R 'L 'R 'R 'R

,R 'R 'L 'L 'L ,R 'L 'R 'R 'R

,R 'R 'L 'L 'L ,R 'L 'R 'R 'R

,R 'R 'L 'L 'L ,R 'L 'R 'R 'R

,R 'R 'L 'L 'L ,R 'L 'R 'R 'R

,R 'R 'R 'L 'L ,R 'L 'L 'R 'R

,R 'R 'R 'L 'L ,R 'L 'L 'R 'R

Io22 'R 'R 'L 'L Io22 'L 'L 'R 'R

Io23 'R 'R 'L 'L Io23 'L 'L 'R 'R

Io24 'R 'R 'L 'L Io24 'L 'L 'R 'R

,R 'R 'R 'L 'L ,R 'L 'L 'R 'R

,R Do22 Do22 Di22 Di22 ,R Di22 Di22 Do22 Do22

,R Do23 Do23 Di23 Di23 ,R Di23 Di23 Do23 Do23

,R Do24 Do24 Do24 Di24 ,R Di24 Di24 Di24 Do24

,R 'R 'R 'R 'L ,R 'L 'L 'L 'R

Io32 'R 'R 'R 'L Io32 'L 'L 'L 'R

Io33 'R 'R 'R 'L Io33 'L 'L 'L 'R

Io34 Do28 Do28 Do28 Di28 Io34 Di28 Di28 Di28 Do28

,R Do29 Do29 Do29 Di29 ,R Di29 Di29 Di29 Do29

,R 'R 'R 'R 'L ,R 'L 'L 'L 'R

,R 'R 'R 'R 'L ,R 'L 'L 'L 'R

--- Page 4 / 22 ---

CUnet Family MKY44-IO32A

■DIP-SW Settings in the DIO mode

0.<,2$UHDGVRXWWKHELWVRIKDUGZDUHVHWWLQJGDWDDVVHULDOGDWDIURPWKH676:DGHGLFDWHG/6,ZKHQUHWXUQLQJIURP

KDUGZDUHUHVHW,WLVUHFRPPHQGHGWRFRQQHFWWZRELWW\SH',36:VWRDQ676:VSHFL¿HGIRUKH[DGHFLPDO

7KHSLQVWRFRQQHFWD',36:WRWKH676:DUHSXOOHGXSLQWHUQDOO\ZKHQUHDGLQJIURPWKH',36:7KHVHELWVUHFRJQL]HWKH21

VWDWH/RZOHYHODV³´7KHIROORZLQJVKRZVWKHGH¿QLWLRQVRIWKH',36:ELWVIRUVHWWLQJLQWKH',2PRGHRIWKH0.<,2$

Pin Name DIP-SW No. Signal Function/Description

3

DIP•SW•DOSA

8')RQ 6HWVWKH212))VWDWHRIWKHGLJLWDO¿OWHUIRUWKHLQSXWVLJQDO

:KHQWKH',36:LVLQWKH21VWDWHWKHGLJLWDO¿OWHULV21

32 3 DOHL

'2+/VHWWLQJWRVHOHFWWKHRXWSXWGDWDWRWKHRXWSXWSLQ7KH

ORZHUELWVLQWKHPHPRU\EORFNDUHVHOHFWHGZKHQWKH',36:

LVLQWKH2))VWDWH7KHXSSHUELWVLQWKHPHPRU\EORFNDUH

VHOHFWHGZKHQ',36:LVLQWKH21VWDWH

3

DOSA

'26$

6HW'26$YDOXHLQKH[DGHFLPDOWUHDWLQJWKH21VWDWHDV³´

3 DOSA4

29 3 4 DOSA3

28 3 3 DOSA2

3 2'26$

3 '26$

3

DIP•SW•SA

8

%36

%36 6HWWKHWUDQVIHUUDWHRI&8QHW

%36%36 2))2)) 0ESV

%36%36 2))21 0ESV

%36%36 212)) 0ESV

%36%36 21217KLVVHWWLQJLVGLVDEOHG

3 %36

3

SA

6$

6HW6$YDOXHLQKH[DGHFLPDOWUHDWLQJWKH21VWDWHDV³´

3 SA4

3 4 SA3

3 3 SA2

3 26$

3 6$

7KH676:KDVDIXQFWLRQWKDWFDQVHW6$DQG'26$LQGHFLPDO)RUGHWDLOVRQVHWWLQJLQGHFLPDOUHIHUWRWKH8VHU¶V0DQXDORI

676:

5HJDUGLQJVHWWLQJWKHGLJLWDO¿OWHUGHJUHH)'DQGWKHGLJLWDO¿OWHUVDPSOHLQWHUYDO),)LOWHU,QWHUYDOVHH“Support for the

CUnet Mail Function (Common to DIO Mode, PWM and Up/Down Counter Mode)”RQSDJH

---22/5egaP---

CUnet Family MKY44-IO32A

The DIO mode of the MKY44-IO32A occupies the MB (Memory Block) of the SA value that is set by SA0 to SA5 of the ST44SW.

The status of the general-purpose I/O pins (Io00 to Io07, Io10 to Io17, Io20 to Io27, Io30 to Io 37) is stored in bits 0 to 31 of the MB

occupied by the DIO mode of the MKY44-IO32A. Among the statuses of the general-purpose I/O pins stored in bits 0 to 31, the

, the latest value loaded in each

Bit 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Content

Io17 Io16 Io15 Io14 Io13 Io12 Io11 Io10 Io7 Io6 Io5 Io4 Io3 Io2 Io1 Io0

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Content

Io37 Io36 Io35 Io34 Io33 Io32 Io31 Io30 Io27 Io26 Io25 Io24 Io23 Io22 Io21 Io20

Bit 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

Content

DFon

DOSA5 DOSA4 DOSA3 DOSA2 DOSA1 DOSA0

DOHL FD3 FD2 FD1 FD0 “0”

IOSWAP

IOS1 IOS0

Bit 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48

Content

“0” FI9FI13 FI12 FI11 FI10 FI8 FI7 FI6 FI5 FI4 FI3 FI2 FI1 FI0

Setting values are stored in bits 32 to 63. These bits show the following settings, loaded when returning from a hardware reset.

Bit Content Description

47 DFon (DIP-SW1: 8) “1” when it is ON

46 to 41 DOSA5 to DOSA0 (DIP-SW1: 6 to 1) DOSA value

40 DOHL (DIP-SW1: 7) “1” when it is ON

34 IOSWAP pin

“1” when the pin is High-level33 IOS1 pin

32 IOS0 pin

7KLVYDOXHLVKH[DGHFLPDOE\WHVLQXQLWVRIȝV

The valid range is 0x0001 to 0x2710 (1 to 10,000). The settings of FD and FI can be changed using the CUnet mail function. For

how to change them, see the section “Support for the CUnet Mail Function”.

FI13, bits 48 to 61,

Selecting the Output Data to the Output Pins in DIO Mode

In the DIO mode of the MKY44-IO32A, the data of the lower or upper 32 bits in the MB (Memory Block) for the DOSA value set by

DOSA0 to DOSA5 of the ST44SW is selected as the data to output. The selection of lower or upper 32 bits is based on the DOHL

setting.

get pins

with positive logic.

of pin STB1.

--- Page 6 / 22 ---

CUnet Family MKY44-IO32A

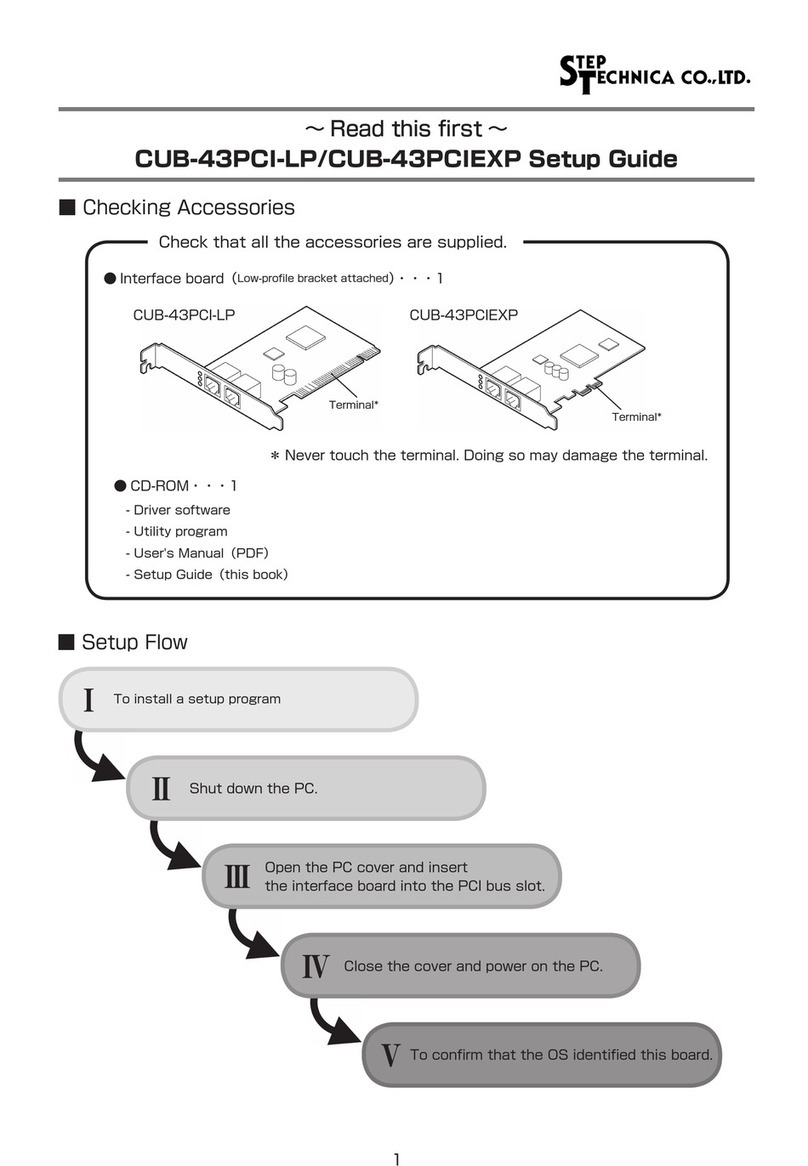

■DIO Mode Connection Overview

7KHIROORZLQJVKRZVDQRYHUYLHZRIWKHFRQQHFWLRQVLQWKH',2PRGHRIWKH0.<,2$7KH',2PRGHRIWKH0.<,2$

VHWVWKH,2VHOHFWLRQVIRUWKHJHQHUDOSXUSRVH,2SLQVXVLQJSLQV,26,26DQG,26:$ 3

7KHXVHRIWKH0.<,2$UHTXLUHVWKH676:DGHGLFDWHG/6,WRORDGWKH',36:VHWWLQJV7KH0.<,2$RSHUDWHVE\

UHDGLQJYLDWKH676:WKHVHWWLQJVRIVWDWLRQDGGUHVV6$WRWUDQVIHUUDWH%36%36GDWDVHOHFWLRQIRURXWSXWSLQV'26$

WR'2+/DQGGLJLWDO¿OWHUDSSOLFDWLRQWRLQSXWVLJQDOV')RQ

---22/7egaP---

CUnet Family MKY44-IO32A

Pin Functions of the DIO mode

Pin name Pin number Logic I/O Function

DEC1UF 3 -- --

Connect a capacitor whose effective capacitance is at least 1 μF and a 0.1 μF ceramic capacitor

for high frequency bypass in parallel between this pin and VSS. Or connect a laminated ceramic

capacitor of around 2.2 μF with the property that capacitance reduction is about 20% even in

DC bias.

#Reset 6 Negative I/O The hardware reset input pin of MKY44-IO32A. Right after power is turned on or when the

user intentionally resets the hardware, Low should be retained for at least 200 μs.

IOSWAP 7 Positive I

Input pin for the setting that inverts the “input” or “output” status of the 32 general-purpose I/

O pins determined by the settings of IOS0 and IOS1. If the Low-level is set when this pin is

High-level, “input” will be inverted to “output,” and vice versa. The setting status of this pin is

read when returning from a hardware reset.

XTAL4i

XTAL4o 10,11 -- -- Pins to connect a crystal oscillator. Connect a 4 MHz crystal oscillator between these pins.

Connect 20 pF ceramic capacitors between these pins and VSS. Connect them near the pins.

DIP_ON 15 Positive O Connect this pin with pin DIP_ON of the ST44SW. For more information about the ST44SW,

refer to the ST44SW User’s Manual.

DIP_RX 17 Positive I Connect this pin with pin DIP_TX of the ST44SW. For more information about the ST44SW,

refer to the ST44SW User’s Manual.

Io30 to Io37

16

18 to 22

24, 25

Positive I/O Pins corresponding to bits 24 to 31 among the 32 bits of general-purpose I/O pins.

Leave this pin open when not in use.

Io00 to Io07 27 to 34 Positive I/O Pins corresponding to bits 0 to 7 among the 32 bits of general-purpose I/O pins.

Leave this pin open when not in use.

Io10 to Io17 35 to 42 Positive I/O Pins corresponding to bits 8 to 15 among the 32 bits of general-purpose I/O pins.

Leave this pin open when not in use.

Io20 to Io27 43 to 46

59 to 62 Positive I/O Pins corresponding to bits 16 to 23 among the 32 bits of general-purpose I/O pins.

Leave this pin open when not in use.

ChipMode 26 Positive I Pin to set the mode of the MKY44-IO32A. To use it as described in this data sheet, be sure to

retain the High-level by connecting to Vdd.

DONA 47 Positive O This pin retains the High-level during the DONA (DO Not Arrival) state.

It is at Low-level at other times.

STB2 48 Positive O Outputs a High-level pulse when reading in the status of the general-purpose input pins.

The MKY44-IO32A reads in the status of the general-purpose input pins while this pin is High.

STB1 50 Positive O Outputs aHigh-level pulse when updating the status of the general-purposeoutputpins.

The MKY44-IO32Aupdates the status of the general-purposeoutputpins while this pin in High.

IOS0 51

Positive I

Pins to set the “input” or “output” status of the 32 general-purpose I/O pins. Using a

combination of High-level and Low-level input to this pin, “input” or “output” is set for the 32

general-purpose I/O pins. The setting status of these two pins (IOS0 and IOS1) is read when

returning from a hardware reset.

IOS1 52

#MCARE 53 Negative O

A pin to output the MCARE signal, which is a standard function of CUnet. This pin outputs the

Low-level for about 50 ms, when the MCARE signal occurs and when it returns from hardware

reset.

#LCARE 54 Negative O

A pin to output the LCARE signal, which is a standard function of CUnet. This pin outputs the

Low-level for about 50 ms, when the LCARE signal occurs and when it returns from hardware

reset.

It is recommended to connect orange color LED indicating a gentle warning to this pin.

#MON 55 Negative O

A pin to output the MON signal, which is a standard function of CUnet. This pin retains Low-

level while a link has been established with another CUnet devices for at least 3 consecutive

cycles.

It is recommended to connect green color LED indicating a stable operation to this pin.

CU_TXD 56 Positive O Output pin to send CUnet packets.

Connect this pin to a drive input pin such as of a driver.

CU_TXE 57 Positive O A pin to output the High-level while CUnet packets are output.

Connect this pin to the enable input pin of the driver.

CU_RXD 58 Positive I A pin to input CUnet packets.

Connect this pin to the output pin of the receiver.

Vdd 1, 2, 4, 23 -- -- Power pin. Supply 3.3 V.

Vss 5, 9, 12 -- -- Power pin. Connected to 0 V.

N.C. 8, 13, 14,

49, 63, 64 -- -- Do not connect to other signals; keep them open.

--- Page 8 / 22 ---

CUnet Family MKY44-IO32A

■DIO mode Pin Assignment

■Electrical Ratings (Common to DIO mode, PWM and Up/Down counter mode)

(TA &9SS 9

Parameter 6\PERO Conditions Min. 7\S Max. Unit

6WRUDJHWHPSHUDWXUH 7VWJ --- --- &

2SHUDWLQJWHPSHUDWXUH 7RSU --- --- &

3LQYROWDJHDEVROXWHPD[LPXPUDWLQJ VI--- --- 9DD 9

2SHUDWLQJSRZHUVXSSO\YROWDJH 9DD --- 9

0HDQRSHUDWLQJFXUUHQW 9DDA9L 9DDRU9SS, RXWSXWRSHQ

;7$/ 0+] --- mA

,2SLQFDSDFLWDQFH Ci/o 9DD 9L 9

7D C--- --- S)

5LVHIDOOWLPHRILQSXWVLJQDO TICLK :KHQLQSXWWLQJJHQHUDWHGFORFN

RI;7$/LSLQ --- --- ns

5LVHIDOOWLPHRILQSXWVLJQDO TIRF 6FKPLWWWULJJHULQSXW --- --- ms

---22/9egaP---

CUnet Family MKY44-IO32A

DIO mode Pin Ratings

No I/O Name Type No I/O Name Type No I/O Name Type No I/O Name Type

1 -- VDD -- 17 I DIP_RX A 33 I/O Io06 A/B 49 -- N.C. --

2 -- VDD -- 18 I/O Io31 A/B 34 I/O Io07 A/B 50 O STB1 B

3 -- DEC1uF -- 19 I/O Io32 A/B 35 I/O Io10 A/B 51 I IOS0 A

4 -- VDD -- 20 I/O Io33 A/B 36 I/O Io11 A/B 52 I IOS1 A

5 -- VSS -- 21 I/O Io34 A/B 37 I/O Io12 A/B 53 O #MCARE B

6 I #Reset C 22 I/O Io35 A/B 38 I/O Io13 A/B 54 O #LCARE B

7 I IOSWAP A 23 -- Vdd -- 39 I/O Io14 A/B 55 O #MON B

8 -- N.C. -- 24 I/O Io36 A/B 40 I/O Io15 A/B 56 O CU_TXD B

9 -- VSS -- 25 I/O Io37 A/B 41 I/O Io16 A/B 57 O CU_TXE B

10 -- XTAL4i -- 26 I ChipMode A 42 I/O Io17 A/B 58 I CU_RXD A

11 -- XTAL4o -- 27 I/O Io00 A/B 43 I/O Io20 A/B 59 I/O Io24 A/B

12 -- VSS -- 28 I/O Io01 A/B 44 I/O Io21 A/B 60 I/O Io25 A/B

13 -- N.C. -- 29 I/O Io02 A/B 45 I/O Io22 A/B 61 I/O Io26 A/B

14 -- N.C. -- 30 I/O Io03 A/B 46 I/O Io23 A/B 62 I/O Io27 A/B

15 O DIP_ON B 31 I/O Io04 A/B 47 O DONA B 63 -- N.C. --

16 I/O Io30 A/B 32 I/O Io05 A/B 48 O STB2 B 64 -- N.C. --

Vt+ max =

Vt- min =

Vt min =

0.8 x VDD

0.2 x VDD

0.6 V

Vt+ max =

Vt- min =

Vt min =

0.8 x VDD

0.2 x VDD

0.6 V

3.0 V

--- Page 10 / 22 ---

CUnet Family MKY44-IO32A

■)XQFWLRQ%ORFNVRI3:0DQG8S'RZQ&RXQWHU0RGH

7KHIROORZLQJVKRZVWKHIXQFWLRQEORFNVLQWKH3:0DQG8S'RZQFRXQWHUPRGHRIWKH0.<,2$

--- Page 11 / 22 ---

CUnet Family MKY44-IO32A

■DIP-SW Setting in PWM and Up/Down Counter Mode

0.<,2$UHDGVRXWWKHELWVRIKDUGZDUHVHWWLQJGDWDDVVHULDOGDWDIURPWKH676:DGHGLFDWHG/6,ZKHQUHWXUQLQJIURP

KDUGZDUHUHVHW,WLVUHFRPPHQGHGWRFRQQHFWWZRELWW\SH',36:VWRDQ676:VSHFL¿HGIRUKH[DGHFLPDO

7KHSLQVWRFRQQHFWD',36:WRWKH676:DUHSXOOHGXSLQWHUQDOO\ZKHQUHDGLQJIURPWKH',36:7KHVHELWVUHFRJQL]HWKH

21VWDWH/RZOHYHODV³´7KHIROORZLQJVKRZVWKHGH¿QLWLRQVRIWKH',36:ELWVIRUVHWWLQJLQWKH3:0DQG8S'RZQFRXQWHU

PRGHRIWKH0.<,2$

Pin Name DIP-SW No. Signal Function/Description

3

DIP•SW•DOSA

8')RQ 6HWVWKH212))VWDWHRIWKHGLJLWDO¿OWHUIRUWKHLQSXWVLJQDO

:KHQWKH',36:LVLQWKH21VWDWHWKHGLJLWDO¿OWHULV21

32 3 GF 'RQ¶W&DUH7KHVHWWLQJRIWKLVVZLWFKGRHVQRWPDWWHULQ3:0

DQG8S'RZQFRXQWHUPRGH

3

DOSA

'26$

6HW'26$YDOXHLQKH[DGHFLPDOWUHDWLQJWKH21VWDWHDV³´

3 DOSA4

29 3 4 DOSA3

28 3 3 DOSA2

3 2'26$

3 '26$

3

DIP•SW•SA

8

%36

%36 6HWWKHWUDQVIHUUDWHRI&8QHW

%36%36 2))2)) 0ESV

%36%36 2))21 0ESV

%36%36 212)) 0ESV

%36%36 21217KLVVHWWLQJLVGLVDEOHG

3 %36

3

SA

6$

6HW6$YDOXHLQKH[DGHFLPDOWUHDWLQJWKH21VWDWHDV³´

3 SA4

3 4 SA3

3 3 SA2

3 26$

3 6$

7KH676:KDVDIXQFWLRQWKDWFDQVHW6$DQG'26$LQGHFLPDO)RUGHWDLOVRQVHWWLQJLQGHFLPDOUHIHUWRWKH8VHU¶V0DQXDORI

676:

5HJDUGLQJVHWWLQJWKHGLJLWDO¿OWHUGHJUHH)'DQGWKHGLJLWDO¿OWHUVDPSOHLQWHUYDO),)LOWHU,QWHUYDOVHH“Support for the

CUnet Mail Function (Common to DIO Mode, PWM and Up/Down Counter Mode)”RQSDJH

---22/21egaP---

CUnet Family MKY44-IO32A

Occupied Memory Block

The PWM and Up/Down counter mode of the MKY44-IO32A occupies the MB (Memory Block) of the SA value that is set by SA0

to SA5 of the ST44SW.

In bits 0 to 23 of the MB occupied by the PWM and Up/Down counter mode of the MKY44-IO32A, the value of Counter-0 is stored.

In bits 24 to 31, the status of the general-purpose input pins (Di0 to Di7) is stored. In bits 32 to 55, the value of Counter-1 is stored.

In bits 56 to 63, the status of the general-purpose output pins (Do0 toDo7) is stored.

OFF, the latest value loaded in each CUnet cycle

Bit 63 to 56 55 to 32 31 to 24 23 to 0

Content

EDo7 to EDo0 Counter-1 Di7 to 0 Counter-0

Bit 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Content

CUT0

15

CUT0

14

CUT0

13

CUT0

12

CUT0

11

CUT0

10

CUT0

9

CUT0

8

CUT0

7

CUT0

6

CUT0

5

CUT0

4

CUT0

3

CUT0

2

CUT0

1

CUT0

0

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Content

Di7 Di6 Di5 Di4 Di3 Di2 Di1 Di0 CUT0

23

CUT0

22

CUT0

21

CUT0

20

CUT0

19

CUT0

18

CUT0

17

CUT0

16

Bit 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

Content

CUT1

15

CUT1

14

CUT1

13

CUT1

12

CUT1

11

CUT1

10

CUT1

9

CUT1

8

CUT1

7

CUT1

6

CUT1

5

CUT1

4

CUT1

3

CUT1

2

CUT1

1

CUT1

0

Bit 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48

Content

EDo7 EDo6 EDo5 EDo4 EDo3 EDo2 EDo1 EDo0 CUT1

23

CUT1

22

CUT1

21

CUT1

20

CUT1

19

CUT1

18

CUT1

17

CUT1

16

For the status of the general-purpose input pins

The values read out from Counter-0 and Counter-1 are as follows.

Range of values : 0x000000 to 0xFFFFFF

Initial value : 0x000000 (Right after power-on, hardware reset, and CLR(#CLR0 or #CLR1) signal input)

Overflow operation : MKY44-IO32A continues counting.

Up counter mode : 0xFFFFFF is reset to start recount from 0x000000.

Down counter mode : 0x000000 is reset to start recount from 0xFFFFFF.

Note : You cannot set any values as the initial value of the counter.

Note : When you read the Counter-0 and Counter-1 values using CUnet master, use the hazard protection function of CUnet master.

the digital filter will be stored.

--- Page 13 / 22 ---

CUnet Family MKY44-IO32A

■Selection of Output Data in PWM and Up/Down Counter Mode

,QWKH3:0DQG8S'RZQFRXQWHUPRGHRIWKH0.<,2$WKH0%0HPRU\%ORFNRIWKH'26$YDOXHVSHFL¿HGE\'26$

WR'26$RIWKH676:LVVHOHFWHGDVWKHGDWDWRRXWSXW7KHYDOXHVHWLQELWVWRRIWKLV0%ZLOOEHDSSOLHGWRWKH+LJKOHYHO

RXWSXWZLGWKRI3:07KHYDOXHVHWLQELWVWRZLOOEHDSSOLHGWRWKH+LJKOHYHORXWSXWZLGWKRI3:07KHYDOXHVHWLQ

ELWVWRZLOOEHDSSOLHGWRWKHIUHTXHQF\ZLGWKWKDWLVFRPPRQWR3:0DQG3:0

%LW WR WR WR WR WR

Content

'RWR'R GF 3:0%$6(ZLGWK 3:0ZLGWK 3:0ZLGWK

%LW 98432

Content

3:0

3:0

3:0

3:0

3:0

3:0

3:0

9

3:0

8

3:0

3:0

3:0

3:0

4

3:0

3

3:0

2

3:0

3:0

%LW 29 28 24 23 22

Content

3:0

3:0

3:0

3:0

3:0

3:0

3:0

9

3:0

8

3:0

3:0

3:0

3:0

4

3:0

3

3:0

2

3:0

3:0

%LW 44 43 42 39 38 34 33 32

Content 3:0%

3:0%

3:0%

3:0%

3:0%

3:0%

3:0%

9

3:0%

8

3:0%

3:0%

3:0%

3:0%

4

3:0%

3

3:0%

2

3:0%

3:0%

%LW 49 48

Content

'R 'R 'R Do4 Do3 Do2 'R 'R GF

7KHYDOXHLQ³GRQ¶WFDUHGF´ZLOOQRWDIIHFWWKHRSHUDWLRQRIWKH0.<,2$

,QWKHH[DPSOHRI³JHQHUDWLRQRI3:0RXWSXWZKHQWKH%DVH&RXQW3:0%$6(LVµ[$%&'¶DQG+L/HYHO&RXQW3:0LV

µ[¶´DVGHVFULEHGLQWKHVHFWLRQ“Function Blocks of PWM and Up/Down counter mode”WKHZLGWKRI+LJKOHYHOVLJQDOWKDW

LVRXWSXWIURPSLQ3:0LV>[[$%&' §@7KH%DVH&ORFNRI3:0RXWSXWLQWKH0.<

,2$LV0+],QWKLVH[DPSOHWKH30:RXWSXWIUHTXHQF\LV>[$%&' §+]@6LPLODUO\

WKH30:RXWSXWIUHTXHQF\LQWKLVH[DPSOHLV>ȝVî[$%&' ȝVî§PV@

,IWKH%DVH&RXQWYDOXHGHWHUPLQHGE\3:0%$6(LV³´LWZLOOEHWUHDWHGDVQRWH[HFXWLQJ3:0RXWSXW,QWKLVFDVHWKHRXWSXW

RIWKH3:0RXWSXWSLQLVPDLQWDLQLQJWKH/RZOHYHO

7KH+L/HYHO&RXQWYDOXHGHWHUPLQHGLQ3:0DQG3:0PXVWQRWEHJUHDWHUWKDQWKHYDOXHRI%DVH&RXQWWKDWLVFRPPRQWR

3:0DQG3:0,IWKHVHWWLQJKDVDQHUURULWLVWUHDWHGDV>+LJKOHYHORXWSXWZLGWK YDOXHRIIUHTXHQF\ZLGWK@LQWKH3:0DQG

8S'RZQFRXQWHUPRGHRIWKH0.<,2$,QWKLVFDVHWKHRXWSXWRI3:0RXWSXWSLQLVPDLQWDLQLQJWKH+LJKOHYHO

--- Page 14 / 22 ---

CUnet Family MKY44-IO32A

■PWM and Up/Down Counter Mode Connection Overview

7KHIROORZLQJVKRZVDQRYHUYLHZRIWKHFRQQHFWLRQVLQWKH3:0DQG8S'RZQFRXQWHUPRGHRIWKH0.<,2$

7KHXVHRIWKH0.<,2$UHTXLUHVWKH676:DGHGLFDWHG/6,WRORDGWKH',36:VHWWLQJV7KH0.<,2$RSHUDWHVE\

UHDGLQJYLDWKH676:WKHVHWWLQJVRIVWDWLRQDGGUHVV6$WRWUDQVIHUUDWH%36%36GDWDVHOHFWLRQIRURXWSXWSLQV'26$

WRDQGGLJLWDO¿OWHUDSSOLFDWLRQWRLQSXWVLJQDOV')RQ

---22/51egaP---

CUnet Family MKY44-IO32A

Pin Functions of the PWM and Up/Down Counter Mode

Pin name Pin number Logic I/O Function

DEC1UF 3 -- --

Connect a capacitor whose effective capacitance is at least 1 μF and a 0.1 μF ceramic capacitor for

high frequency bypass in parallel between this pin and VSS. Or connect a laminated ceramic capacitor

of around 2.2 μF with the property that capacitance reduction is about 20% even in DCbias.

#Reset 6 Negative I/O The hardware reset input pin of MKY44-IO32A. Right after power is turned on or when the user

intentionally resets the hardware, Low should be retained for at least 200 μs.

XTAL4i

XTAL4o 10, 11 -- -- Pins to connect a crystal oscillator. Connect a 4 MHz crystal oscillator between these pins.

Connect 20 pF ceramic capacitors between these pins and VSS. Connect them near the pins.

DIP_ON 15 Positive O Connect this pin with pin DIP_ON of the ST44SW. For more information about the ST44SW,

refer to the ST44SW User’s Manual.

DIP_RX 17 Positive I Connect this pin with pin DIP_TX of the ST44SW. For more information about the ST44SW,

refer to the ST44SW User’s Manual.

Do0 to Do7

16

18 to 22

24,25

Positive O 8-bit general-purpose output pin. Leave this pin open when not in use.

ChipMode 26 Positive I Pin to set the mode of the MKY44-IO32A. To use it in PWM and Up/Down counter mode, be

sure to retain the Low-level by connecting to Vss.

Di0 to Di7 27 to 34 Positive I 8-bit general-purpose input pin. Leave this pin open when not in use.

#UP0 35 Negative I Count-up input pin of counter 0. When the signal of this pin transits from High-level to Low-

level, “1” is added to the value of counter 0. Leave this pin open when not in use.

#DOWN0 36 Negative I Count-down input pin of counter 0. When the signal of this pin transits from High-level to Low-

level, “1” will is subtracted from the value of counter 0. Leave this pin open when not in use.

#CLR0 37 Negative I Input pin where the value of counter 0 is “0”. If Low-level is input to this pin, “0” will be set in

the value of counter 0. Leave this pin open when not in use.

#UP1 38 Negative I Count-up input pin of counter 1. When the signal of this pin transits from High-level to Low-

level, “1” is added to the value of counter 1. Leave this pin open when not in use.

#DOWN1 39 Negative I Count-down input pin of counter 1. When the signal of this pin transits from High-level to Low-

level, “1” will is subtracted from the value of counter 1. Leave this pin open when not in use.

#CLR1 40 Negative I Input pin where the value of counter 1 is “0”. If Low-level is input to this pin, “0” will be set in

the value of counter 1. Leave this pin open when not in use.

PWM0 41 Positive O Output pin of the PWM0 function. Leave this pin open when not in use.

PWM1 42 Positive O Output pin of the PWM1 function. Leave this pin open when not in use.

DONA 47 Positive O This pin retains the High-level during the DONA (DO Not Arrival) state. It is at Low-level at

other times.

#PING 50 Negative O Pin to output the PING signal, a standard feature of CUnet.

This pin transits to Low-level when the PING signal is generated.

#CYCT 51 Negative O Pin to output the CYCT signal, a standard feature of CUnet.

This pin transits to Low-level when the CYCT signal is generated.

#MCARE 53 Negative O

A pin to output the MCARE signal, which is a standard function of CUnet. This pin outputs the

Low-level for about 50 ms, when the MCARE signal occurs and when it returns from hardware

#LCARE 54 Negative O

A pin to output the LCARE signal, which is a standard function of CUnet. This pin outputs the

Low-level for about 50 ms, when the LCARE signal occurs and when it returns from hardware

reset. It is recommended to connect orange color LED indicating a gentle warning to this pin.

#MON 55 Negative O

A pin to output the MON signal, which is a standard function of CUnet. This pin retains Low-

level while a link has been established with another CUnet devices for at least 3 consecutive

cycles. It is recommended to connect green color LED indicating a stable operation to this pin.

CU_TXD 56 Positive O Output pin to send CUnet packets. Connect this pin to a drive input pin such as of a driver.

CU_TXE 57 Positive O A pin to output the High-level while CUnet packets are output.

Connect this pin to the enable input pin of the driver.

CU_RXD 58 Positive I A pin to input CUnet packets. Connect this pin to the output pin of the receiver.

Vdd 1, 2, 4

23 -- -- Power pin. Supply 3.3 V.

Vss 5, 9, 12 -- -- Power pin. Connected to 0 V.

N.C.

7, 8, 13, 14

43 to 46

48, 49, 52

59 to 64

Do not connect to other signals; keep them open.

--- Page 16 / 22 ---

CUnet Family MKY44-IO32A

■PWM and Up/Down Counter Mode Pin Assignment

■Electrical Ratings (Common to DIO mode, PWM and Up/Down counter mode)

(TA &9SS 9

Parameter 6\PERO Conditions Min. 7\S Max. Unit

6WRUDJHWHPSHUDWXUH 7VWJ --- --- &

2SHUDWLQJWHPSHUDWXUH 7RSU --- --- &

3LQYROWDJHDEVROXWHPD[LPXPUDWLQJ VI--- --- 9DD 9

2SHUDWLQJSRZHUVXSSO\YROWDJH 9DD --- 9

0HDQRSHUDWLQJFXUUHQW 9DDA9L 9DDRU9SS, RXWSXWRSHQ

;7$/ 0+] --- mA

,2SLQFDSDFLWDQFH Ci/o 9DD 9L 9

7D C--- --- S)

5LVHIDOOWLPHRILQSXWVLJQDO TICLK :KHQLQSXWWLQJJHQHUDWHGFORFN

RI;7$/LSLQ --- --- ns

5LVHIDOOWLPHRILQSXWVLJQDO TIRF 6FKPLWWWULJJHULQSXW --- --- ms

---22/71egaP---

CUnet Family MKY44-IO32A

PWM and Up/Down Counter Mode Pin Ratings

No I/O Name Type No I/O Name Type No I/O Name Type No I/O Name Type

1 -- VDD -- 17 I DIP_RX A 33 I Di6 A 49 -- N.C. --

2 -- VDD -- 18 O Do1 B 34 I Di7 A 50 O #PING B

3 -- DEC1uF -- 19 O Do2 B 35 I #UP0 A 51 O #CYCT B

4 -- VDD -- 20 O Do3 B 36 I #DOWN0 A 52 -- N.C. --

5 -- VSS -- 21 O Do4 B 37 I #CLR0 A 53 O #MCARE B

6 I #Reset C 22 O Do5 B 38 I #UP1 A 54 O #LCARE B

7 -- N.C. -- 23 -- VDD -- 39 I #DOWN1 A 55 O #MON B

8 -- N.C. -- 24 O Do6 B 40 I #CLR1 A 56 O CU_TXD B

9 -- VSS -- 25 O Do7 B 41 O PWM0 B 57 O CU_TXE B

10 -- XTAL4i -- 26 I ChipMode A 42 O PWM1 B 58 I CU_RXD A

11 -- XTAL4o -- 27 I Di0 A 43 -- N.C. -- 59 -- N.C. --

12 -- VSS -- 28 I Di1 A 44 -- N.C. -- 60 -- N.C. --

13 -- N.C. -- 29 I Di2 A 45 -- N.C. -- 61 -- N.C. --

14 -- N.C. -- 30 I Di3 A 46 -- N.C. -- 62 -- N.C. --

15 O DIP_ON B 31 I Di4 A 47 O DONA B 63 -- N.C. --

16 O Do0 B 32 I Di5 A 48 -- N.C. -- 64 -- N.C. --

Vt+ max =

Vt- min =

Vt min =

0.8 x VDD

0.2 x VDD

0.6 V

Vt+ max =

Vt- min =

Vt min =

0.8 x VDD

0.2 x VDD

0.6 V

3.0 V

--- Page 18 / 22 ---

CUnet Family MKY44-IO32A

■Monitor functions of CUnet (Common to DIO mode, PWM and Up/Down counter mode)

0.<,2$¶VSLQV021/&$5(0&$5(DQG'21$RXWSXWDFFRUGLQJWR&8QHWVWDQGDUGIXQFWLRQ,QWKH3:0DQG

XSGRZQFRXQWHUPRGHWKH&8QHWVWDQGDUGIXQFWLRQVRIWKHSLQV&<&7DQG3,1*DUHDOVRDYDLODEOH7KHIROORZLQJVKRZVWKH

IXQFWLRQVRIWKHVHSLQV

Pin Function

3,1*

7KLVSLQQRUPDOO\PDLQWDLQV+LJKOHYHO,WWUDQVLWLRQVWR/RZOHYHOZKHQWKH3,1*LQVWUXFWLRQLVUHFHLYHGIURPDQRWKHU&8QHW

VWDWLRQDQGODWHULWWUDQVLWLRQVWR+LJKOHYHOZKHQDSDFNHWZLWKQR3,1*LQVWUXFWLRQWR0.<,2$LVQRWSODFHGLVUHFHLYHG

IURPDQRWKHU&8QHWVWDWLRQ

#CYCT 7KLVSLQQRUPDOO\PDLQWDLQV+LJKOHYHODQGRXWSXWV/RZSXOVHIRU³î7ESV´WLPHDWWKHOHDGWLPLQJRIWKH&8QHWF\FOH

021 7KLVSLQRXWSXWVWKH021VLJQDOZKLFKLVDVWDQGDUGIXQFWLRQRI&8QHW7KLVSLQUHWDLQV/RZOHYHOZKLOHDOLQNKDVEHHQ

HVWDEOLVKHGZLWKDQRWKHU&8QHWGHYLFHIRUDWOHDVWFRQVHFXWLYHF\FOHV

/&$5(

7KLVSLQRXWSXWVWKH/&$5(VLJQDOZKLFKLVDVWDQGDUGIXQFWLRQRI&8QHW7KLVSLQRXWSXWVWKH/RZOHYHOIRUPVZKHQWKH

/&$5(VLJQDOLVJHQHUDWHGDQGXSRQUHWXUQIURPKDUGZDUHUHVHW$VDXQLTXHIXQFWLRQRIWKH0.<,2$WKH/RZOHYHO

RXWSXWRIWKLVSLQLVDOVRXVHGWRGLVSOD\KDUGZDUHHUURUVLQFOXGLQJVHWWLQJHUURUV

0&$5(

7KLVSLQRXWSXWVWKH0&$5(VLJQDOZKLFKLVDVWDQGDUGIXQFWLRQRI&8QHW7KLVSLQRXWSXWVWKH/RZOHYHOIRUPVZKHQWKH

0&$5(VLJQDOLVJHQHUDWHGDQGXSRQUHWXUQIURPKDUGZDUHUHVHW$VDXQLTXHIXQFWLRQRIWKH0.<,2$WKH/RZOHYHO

RXWSXWRIWKLVSLQLVDOVRXVHGWRGLVSOD\KDUGZDUHHUURUVLQFOXGLQJVHWWLQJHUURUV

'21$ 7KLVSLQRXWSXWVWKH/RZOHYHOZKHQLWFDQFRQ¿UPWKHSUHVHQFHRIDQRWKHUSDUW\LVVXLQJRSHUDWLRQFRPPDQGVWRWKH0.<

,2$:KHQLWFDQQRWFRQ¿UPWKHSUHVHQFHRIDQRWKHUSDUW\LWRXWSXWVWKH+LJKOHYHO

■&RQQHFWLRQRI/('VDQG'LVSOD\6WDWXV&RPPRQWR',2PRGH3:0DQG8S'RZQFRXQWHUPRGH

/('FRQQHFWLRQLVUHFRPPHQGHGIRUWKH021/&$5(0&$5('21$SLQVRI0.<,2$,WLVUHFRPPHQGHGWR

FRQQHFWJUHHQFRORU/('SDUWLQGLFDWLQJDVWDEOHRSHUDWLRQWR021SLQDQG'21$SLQ7R/&$5(SLQLWLVUHFRPPHQGHGWR

FRQQHFWRUDQJHFRORU/('SDUWLQGLFDWLQJDJHQWOHZDUQLQJ7R0&$5(SLQLWLVUHFRPPHQGHGWRFRQQHFWUHGFRORU/('SDUW

LQGLFDWLQJDGH¿QLWHZDUQLQJ7KHVHSLQVKDYHrP$FXUUHQWGULYHFDSDELOLW\&RQQHFWWKHPLQVXFKDZD\WKDWWKH/('VZLOOOLJKW

XSDW/RZOHYHO

7KH/('VGLVSOD\WKHVWDWXVRI0.<,2$7KHVWDWHLQZKLFK021DQG'21$DUHOLWLVZKHQQRUPDORSHUDWLRQLVSRVVLEOH

1RWH7KHIROORZLQJWDEOHGRHVQRWFRYHUWKHSLQQDPH³´WKDWVKRZVQHJDWLYHORJLFVLQFHLWLVEDVHGRQVLJQDOQDPHV

DONA MON LCARE MCARE State

--- --- --- --- ,QGLFDWHVWKHVWDWHRISRZHURIIWKHVWDWHZKHQWKH5HVHWSLQLVDFWLYHRUWKHVWDWHZKHQQR

&8QHWGHYLFHVLVOLQNHGDIWHUUHWXUQLQJIURPKDUGZDUHUHVHW

--- --- --- $OWKRXJKDOLQNLVVXFFHVVIXOO\HVWDEOLVKHGZLWKDWOHDVWRQH&8QHWGHYLFHWKHVWDWLRQDGGUHVV

GHYLFHWKHRWKHUSDUW\WKDWZULWHVWKH'RGDWDWRWKH0.<,2$VHWE\'26$LVPLVVLQJ

--- --- 7KHFRQQHFWLRQRIWKH&8QHWQHWZRUNLVQRUPDO

--- --- --- 7KHVHWWLQJYDOXHVRI6$DQG'26$RI',36:DUHLQDSSURSULDWH

--- --- --- :KHQLWEHFRPHVFOHDUWKDWDWOHDVWRQH&8QHWOLQNLVQRWHVWDEOLVKHGWKH/('ÀDVKHVIRU

DSSUR[LPDWHO\PV

--- --- --- :KHQLWEHFRPHVFOHDUWKDWDWOHDVWRQH&8QHWOLQNKDVQRWEHHQHVWDEOLVKHGGXULQJWKHODVW

FRQVHFXWLYHVFDQVWKH/('ÀDVKHVIRUDSSUR[LPDWHO\PV

--- ---

:KHQLWEHFRPHVFOHDUWKDWDWOHDVWRQH&8QHWOLQNKDVEHHQGLVFRQQHFWHGGXULQJWKHODVW

FRQVHFXWLYHVFDQVDQGZKHQKDUGZDUHUHVHWLVH[HFXWHGWKH/('ÀDVKHVIRUDSSUR[LPDWHO\

PV

--- ---

7KHIROORZLQJLQWHUQDOKDUGZDUHRI0.<,2$LVDEQRUPDO

%OLQNDOWHUQDWHO\HYHU\VHFRQG ',36:UHDGKDUGZDUHLQFOXGLQJ676:

%OLQNDOWHUQDWHO\HYHU\WZRVHFRQGV 0.<,2$LQWHUQDOKDUGZDUH

3OHDVHSHUIRUPPDLQWHQDQFHVXFKDVUHSODFHPHQW

&RQWLQXRXVOLJKWLQJ )ODVKOLJKWLQJIRUDERXWPV $OWHUQDWLQJOLWDQGXQOLWHYHU\IHZVHFRQGV

8QLTXHWR0.<,2$GLVSOD\WKHVWDWXVLQZKLFKRQO\0&$5(VWD\VOLWPHDQVWKDWWKHVHWWLQJVRI6$DQG'26$RI',36:DUH

LQDSSURSULDWHO\LGHQWLFDORURYHUODSSLQJYDOXHV,I/&$5(DQG0&$5(NHHSEOLQNLQJHYHU\IHZVHFRQGVLWPHDQVDIDLOXUHFDXVHG

E\DFUDVKLQ0.<,2$

7KHRWKHUVLJQDOWUDQVLWLRQVRI021/&$5(DQG0&$5(DUHVWDQGDUG&8QHWRSHUDWLRQ)RUPRUHLQIRUPDWLRQDERXWWKHVHVLJQDOV

UHIHUWRWKHVHFWLRQ“Quality Control and Indication of Network”DQGRWKHUVLQWKH8VHU¶V0DQXDORIWKH&8QHWGHGLFDWHG/6,WKDWLV

LQVWDOOHGLQWKHGHYLFHWRUHIHUWRWKH0.<,2$GDWD

--- Page 19 / 22 ---

CUnet Family MKY44-IO32A

■Support for the CUnet Mail Function (Common to DIO mode, PWM and Up/Down counter mode)

7KH0.<,2$FDQH[HFXWH³SURGXFWLQTXLU\´DQG³VHWWLQJFKDQJH´XVLQJWKH&8QHWPDLOIXQFWLRQ

●3URGXFW,QTXLU\8VLQJWKH0DLO

8SRQUHFHLYLQJDPHVVDJHLQSURGXFWLQTXLU\IRUPDWXVLQJWKH³&8QHW"´FKDUDFWHUVWULQJWKH0.<,2$UHSOLHVWRWKHVHQGHU

XVLQJWKHEDVLFIRUPDWRIWKH0.<,2$<RXFDQPDNHDSURGXFWLQTXLU\IURPDQ\QRGHRIWKH&8QHW

◆3URGXFW,QTXLU\)RUPDW

$GGUHVV [ [ [ [ [ [ [ [

Ascii C U n e t [sp] ? [¥r]

+H[ [ [ [( [ [ [ [) ['

◆%DVLF)RUPDWRIWKH0.<,2$

$GGUHVV [ [ [ [ [ [ [ [

Ascii I O 3 2 A [sp] *VN *Vn

+H[ [ [) [ [ [ [ ❋ ❋

$GGUHVV [ [ [$ [% [& [' [( [)

Ascii

M❋❋❋❋❋❋❋

+H[ [' [ SA DOSA Status )' ),

◆'HVFULSWLRQRIWKH%DVLF)RUPDW

6\PERO Name Description Valid range

919Q 9HUVLRQ

1XPEHU

6KRZVWKHYHUVLRQQXPEHURIWKH0.<,2$LQWZR$6&,,FKDUDFWHUV

7KHYHUVLRQQXPEHUVVWDUWIURP³´91UHSUHVHQWVWKHWHQVSODFHDQG

9QUHSUHVHQWVWKHRQHVSODFH

WR

(in ASCII)

SA ',36: 7KHGDWDRI',36:LVVKRZQLQRQHKH[DGHFLPDOE\WH [WR[))

DOSA ',36: 7KHGDWDRI',36:LVVKRZQLQRQHKH[DGHFLPDOE\WH [WR[))

Status Status

DIO mode

ELW ³´

[WR[

ELWWR ³´

bit2 ,26:$3SLQ+LJKOHYHO ³´

ELW ,26SLQ+LJKOHYHO ³´

ELW ,26SLQ+LJKOHYHO ³´

3:0DQG8S

'RZQFRXQWHU

mode

6KRZV³´LQELWVWR [

)' )LOWHU

'HJUHH 6KRZVWKHGLJLWDO¿OWHUGHJUHHWKDWLQÀXHQFHVWKHLQSXWVLJQDORISLQ'L [[[

[[$

), )LOWHU

,QWHUYDO

7KHVDPSOHLQWHUYDORIWKHGLJLWDO¿OWHUWKDWLQÀXHQFHVWKHLQSXWVLJQDORI

SLQ'LLVVKRZQLQWZRKH[DGHFLPDOE\WHVȝVXQLWZKHUHE\WH[(LV

WKH/6%

[WR[

WR

7KHVWDWXVRISLQV,26:$3,26DQG,26VKRZQLQ³6WDWXV´LVWKHYDOXHORDGHGZKHQWKH0.<,2$UHWXUQVIURPD

KDUGZDUHUHVHW

--- Page 20 / 22 ---

CUnet Family MKY44-IO32A

●Setting Change Using the Mail Function

7KH0.<,2$FDQFKDQJHVHWWLQJVXVLQJWKH&8QHWPDLOIXQFWLRQ7KHVHWWLQJVWKDWFDQEHFKDQJHGDUH)')LOWHU'HJUHHDQG

),)LOWHU,QWHUYDOLQWKHEDVLFIRUPDW

7KHPDLOIRUPDWXVHGLQFKDQJLQJVHWWLQJVLVGLIIHUHQWIURPWKHEDVLFIRUPDWRI

WKH0.<,2$E\RQHOHWWHU7KHGLIIHUHQFHLV³:´LQE\WH[LQVWHDG

RI³0´7KHUHIRUHLWLVUHFRPPHQGHGWRFKDQJHWKHVHWWLQJVE\WKHIROORZLQJ

RSHUDWLRQSURFHGXUH

)LUVWH[HFXWH³SURGXFWLQTXLU\´DQGFRS\WKHFRQWHQWVHQWIURPWKH

0.<,2$WRWKHPDLOVHQGEXIIHU7KHQFKDQJH³0´WR³:´LQ

E\WH[

$PRQJ)'DQG),LQWKHPDLOVHQGEXIIHUUHZULWHWKHLWHPVWRFKDQJH

6HQGDPHVVDJHWRWKH0.<,2$

:KHQWKHVHWWLQJVDUHVXFFHVVIXOO\FKDQJHGXVLQJWKHPDLOIXQFWLRQWKH0.<,2$VHQGVDPHVVDJHLQ$&.IRUPDWLQ

ZKLFKE\WH[RIWKHEDVLFIRUPDWLV³$´7KHFKDQJHGYDOXHVDUHVWRUHGLQ)'DQG),LQWKH$&.IRUPDW

,IWKHVHWWLQJFKDQJHE\PDLOLVVXFFHVVIXOO\FRPSOHWHGWKH0.<,2$ZLOOVWRUHWKHYDOXHLQWKHÀDVK520LQWKH

0.<,2$DQGUHERRWLWVHOI7KXVWKH0.<,2$ZLOOVWDUWRSHUDWLRQXVLQJWKHFKDQJHGYDOXHV6LPLODUO\LIWKH

SRZHURIWKH0.<,2$LVWXUQHG2))RUDKDUGZDUHUHVHWLVH[HFXWHGWKH0.<,2$ZLOOVWDUWRSHUDWLRQDFFRUGLQJ

WRWKHYDOXHVVWRUHGLQWKHÀDVK520

,IWKH0.<,2$FRXOGQRWFKDQJHWKHVHWWLQJVXFFHVVIXOO\XVLQJWKHPDLOIXQFWLRQLWZLOOUHWXUQD1$.FRGHPHVVDJHLQ

ZKLFKE\WH[RIWKHEDVLFIRUPDWLV³1´,QWKLVFDVHWKHUHDVRQIRUWKH1$.ZLOOEHVKRZQLQE\WH[

6HWWLQJFKDQJHRI0.<,2$XVLQJWKHPDLO

IXQFWLRQLVDFFHSWHGRQO\ZKHQWKHPHVVDJHLV

VHQWIURPWKHQRGHVHWWR'26$,IWKHVHWWLQJ

FKDQJHPHVVDJHLVUHFHLYHGIURPDQRGHZKLFK

LVQRWVHWWR'26$LWZLOOUHWXUQWKH1$.FRGH

PHVVDJHDQGWKHVHWWLQJZLOOQRWEHFKDQJHG

$OVRLIWKHPHVVDJHGRHVQRWPDWFKZLWKWKH

IRUPDWRUWKHYDOXHWRFKDQJHLVQRWLQWKHYDOLG

UDQJHWKH0.<,2$ZLOOUHWXUQ1$.FRGH

PHVVDJHDQGZLOOQRWFKDQJHWKHVHWWLQJ

,IDPHVVDJHLQZKLFKE\WH[RIWKHEDVLFIRUPDWLV³5´LVVHQWWRWKH0.<,2$\RXFDQUHFHLYH$&.IRUPDWZKHUHE\WH

[LV³$´7KLVZLOOHQDEOHUHFRQ¿UPDWLRQRIWKHFKDQJHGVHWWLQJV

%\WH[ 'H¿QLWLRQ

Ascii Hex

M[' 0DVWHU&RGH

W[ :ULWH

A[ $&.$&.QRZOHGJHPHQW

1 [( 1$.1HJDWLYH$F.QRZOHGJHPHQW

R[ Read

%\WH[ 'H¿QLWLRQ

[ &DQQRWDFFHSW:ULWHFRPPDQGIURPDQRGHZKLFKGRHVQRWPDWFK

'26$

[ 7KHUHFHLYHGE\WH[0&0HVVDJH&RGHLVQRW³[´

[ 7KHVSHFL¿HG)')LOWHU'HJUHHLVRXWRIWKHYDOLGUDQJH

[ 7KHVSHFL¿HG),)LOWHU,QWHUYDOLVRXWRIWKHYDOLGUDQJH

[( 7KH¿UVWE\WHVDUHLUUHJXODU

[( 7KHIRUPDWLVLUUHJXODU

[( 7KHPDLOGDWDVL]HLVLUUHJXODU

This manual suits for next models

3

Table of contents

Other Step Technica PCI Card manuals

Popular PCI Card manuals by other brands

Exar

Exar Stretch VRC7000 Series Installer's guide

Softing

Softing CANpro PC/104plus Hardware user manual

Datapath

Datapath VisionSC-HD4+ user manual

SWEEX

SWEEX PU202 - QUICK_START_GUIDE manual

Lucent Technologies

Lucent Technologies WaveLAN/ISA Card user manual

StarTech.com

StarTech.com PEXUSB3S22 instruction manual