Terasic THDB-SUM User manual

Terasic THDB-SUM

T

TT

THDB

HDBHDB

HDB-

--

-SUM

SUMSUM

SUM

Terasic HSMC to Santa Cruz Daughter Board

User Manual

Document Version 1.3 JULY. 29, 2009 by Terasic

Introduction

ii

Page Index

INTRODUCTION................................................................................................................................................................................. 1

1.1

F

EATURES

........................................................................................................................................................................... 1

1.2

G

ETTING

H

ELP

.................................................................................................................................................................... 2

ARCHITECTURE................................................................................................................................................................................ 3

2.1

L

AYOUTAND

C

OMPONETS

.................................................................................................................................................. 3

2.2

B

LOCK

D

IAGRAM

................................................................................................................................................................. 5

BOARD COMPONENTS................................................................................................................................................................... 6

3.1

T

HE

HSMC

C

ONNECTOR

................................................................................................................................................... 6

3.2

S

ANTA

C

RUZ

C

ONNECTOR

............................................................................................................................................... 10

3.3

USB

O

N

-T

HE

-G

O TRANSCEIVER

..................................................................................................................................... 14

3.4

M

ICTOR

C

ONNECTOR

....................................................................................................................................................... 16

3.5

SD

C

ARD

I

NTERFACE

....................................................................................................................................................... 18

3.6

SMA

C

ONNECTOR

............................................................................................................................................................ 19

3.7

I2C

S

ERIAL

EEPROM ..................................................................................................................................................... 20

3.8

P

OWER

S

UPPLY

................................................................................................................................................................ 21

DEMONSTRATION .......................................................................................................................................................................... 22

4.1

C

ONNECTING

THDB-SUM

B

OARD TO

C

YCLONE

III

S

TART

B

OARD

............................................................................... 22

APPENDIX......................................................................................................................................................................................... 24

5.1

R

EVISION

H

ISTORY

........................................................................................................................................................... 24

5.2

A

LWAYS

V

ISIT

THDB-SUM

W

EBPAGE FOR

N

EW

M

AIN BOARD

...................................................................................... 24

Introduction

1

1

11

1

Introduction

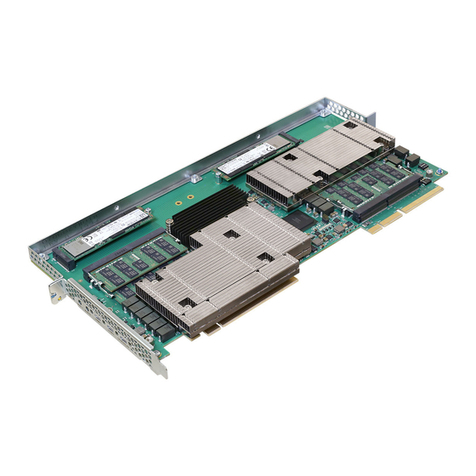

THDB-SUM (HSMC to Santa Cruz / USB / Mictor Daughter Board) is an adapter board to convert High Speed

Mezzanine Connector (HSMC) interface to Santa Cruz (SC), USB, Mictor, and SD Card interface. It allows

users to use these interface on a host board with a HSMC connector.

Because of limited I/O numbers of the HSMC interface, the SC interface and USB port have to share the same

I/O pins. Users can choose which interface to be enabled by jumper selection.

Finally, the source signals from the HSMC interface to the SC header on the THDB-SUM board will be passed

through level shifters to adjust the logic level difference between the HSMC and SC interface board.

1.1Features

Figure 1.1 shows the photo of the THDB-SUM board. The important features are listed below:

•One HSMC connector for interface conversion

•One Santa Cruz interface

•Adjustable logic levels between HSMC and SC interface signals

•One Hi-Speed USB On-The-Go transceiver

•One Mictor Connector

•One SMA Connector for external clock input

•One SD Card Socket

Figure 1.1. The THDB-SUM board

Introduction

2

1.2Getting Help

Here are some places to get help if you encounter any problem:

Email to support@terasic.com

Taiwan & China: +886-3-550-8800

Korea : +82-2-512-7661

Japan: +81-428-77-7000

Architecture

3

2

Architecture

This chapter describes the architecture of the THDB-SUM board including its PCB and block diagram.

2.1 Layout and Componets

The picture of the TDRB-SUM board is shown in Figure 2.1 and Figure 2.2. It depicts the layout of the board

and indicates the location of the connectors and key components.

Mictor Connector (J2)

SMA Connector (J6)

JTAG TDI/TDO

Loopback Header (JP0)

HSMC Logical Level

Configuration Header (JP3)

USB/SC Function Select

Header (JP1)

SC Connector Logical Level

Configuration Header (JP3)

Level Shifters (U7~U8)

USB Host/Peripheral Mode

Configuration Header(JP2)

Santa Cruz Connector (J5)

Santa Cruz Connector (J4)

Santa Cruz Connector (J3)

Level Shifters (U3~U6)

Bus Switch (U1~U2)

Mini USB AB type

receptacle connector (J8)

USB On-The-Go transceiver (U11)

EEPROM(U10)

Figure 2.1. The THDB-SUM PCB and component diagram

Architecture

4

SD Card Socket (J7)

HSMC Connector (J1)

Figure 2.2. The THDB-SUM Back side – HSMC connector view

The following components are provided on the THDB-SUM board :

•HSMC expansion connector (J1)

•Santa Cruz Headers(J3,J4,J5)

•Mictor connector (J2)

•SMA connector (J6)

•Hi-Speed USB On-The-Go transceiver (U11)

oFully compliant with Universal Serial Bus Specification Rev. 2.0

oSupplement to the USB 2.0 Specification Rev. 1.3

oSupplement UTMI+ Low Pin Interface (ULPI) Specification Rev. 1.1

•Mini USB AB type receptacle connector(J8)

•Logic level configuration headers (JP3,JP4)

•SD Card socket(J7)

•I2C serial EEPROM (U10)

•Level translator (U3~U9)

•Bus Switches (U1~U2)

Architecture

5

2.2 Block Diagram

Figure 2.3 shows the block diagram of the THDB-SUM board

HSMC

Connector

SD Card Interface

Mictor Connector Interface

External Clock Input

I2C Interface

SC Interface

THDB-SUM

USB Interface

USB

Transceiver

Mictor

Connector

Bus

Switch

Santa Cru

Connector

SD Card

Socket

SMA

Connector

Level

Shift

Level

Shift

I2C Serial

EEPROM

To

HSMC Interface

Host Board

Figure 2.3. The block diagram of the THDB-SUM board

Board Components

6

3

33

3

Board Components

This section will describe the detailed information of the components, connector interfaces, and the pin

mapping tables of the THDB-SUM board

3.1 The HSMC Connector

This section describes the HSMC connector on the THDB-SUM board

THDB-SUM board contains an Altera standard HSMC connector. All the other connector interfaces on the

THDB-SUM board are connected to the HSMC connector. Figure 3.1, Figure 3.2, and Figure 3.3 show the

pin-outs of the HSMC connector. Also, the JTAG interface of the HSMC connector is shown in the Figure 3.4. If

users don’t need to use the JTAG interface on the THDB-SUM board, please short the header JP0 to loopback

the TDI and TDO signals on the HSMC connector.

Board Components

7

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

HSMC_SCL

HSMC_TMS

HSMC_TDI

SD Wpn

NC

NC

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

2

4

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

HSMC_SDA

HSMC_TCK

HSMC_TDO

SD DAT1

NC

NC

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

1

3

Figure 3.1. The pin-outs of Bank 1 on the HSMC connector

Board Components

8

SD DAT3

SD DAT2

HSPROTO_RESET

HSPROTO_IO0

HSPROTO_IO1

HSPROTO_IO2

HSPROTO_IO3

HSPROTO_IO4

HSPROTO_IO5

HSPROTO_IO6

HSPROTO_IO7

HSPROTO_IO8

HSPROTO_IO9

HSPROTO_IO10

HSPROTO_IO11

HSPROTO_IO12

HSPROTO_IO13

HSPROTO_IO14

EXT_CLK

CLK2

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

SD_DAT0

SD_CLK

SD_CMD

HSPROTO_IO40

HSPROTO_IO29

HSPROTO_IO30

HSPROTO_IO31

HSPROTO_IO33

HSPROTO_IO32

HSPROTO_IO35

HSPROTO_IO34

HSPROTO_IO37

HSPROTO_IO36

HSPROTO_IO39

HSPROTO_IO38

HSPROTO_IO15

HSPROTO_IO16

HSPROTO_IO17

OSC

CLK1

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

Figure 3.2. The pin-outs of Bank 2 of the HSMC connector.

Board Components

9

MICTOR_D14

MICTOR_D15

12V

MICTOR_D16

MICTOR_D17

12V

MICTOR_D18

MICTOR_D19

12V

MICTOR_D20

MICTOR_D21

12V

MICTOR_D22

MICTOR_D23

12V

MICTOR_D24

HSPROTO_IO23

12V

HSPROTO_IO24

HSPROTO_IO25

12V

HSPROTO_IO26

HSPROTO_IO27

12V

HSPROTO_CARDSEL

HSPROTO_IO28

12V

MICTOR_CLK

DEV_SEL_R5 0

GND

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

MICTOR_D0

MICTOR_D1

VCC33

MICTOR_D4

MICTOR_D5

VCC33

MICTOR_D2

MICTOR_D3

VCC33

MICTOR_D6

MICTOR_D13

VCC33

MICTOR_D12

MICTOR_D11

VCC33

MICTOR_D10

MICTOR_D9

VCC33

MICTOR_D8

MICTOR_D7

VCC33

HSPROTO_IO18

HSPROTO_IO19

VCC33

HSPROTO_IO20

HSPROTO_IO21

VCC33

HSPROTO_IO22

TR_CLK

VCC33

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

Figure 3.3. The pin-outs of Bank 3 of the HSMC connector

JP0

Open : JTAG Chain

Close : JTAG Pass

NM:No Mount

HSMC_TDI R1

R2

R3

R4

0

0

0

0

21

HSMC_TDO

HSMC_TDI HSMC_TDI

MICTOR_TDI

MICTOR_TDO

NM

NM

Figure 3.4. The JTAG interface setting of the HSMC connector.

Board Components

10

3.2 Santa Cruz Connector

This section describes the Santa Cruz connector on the THDB-SUM board

The THDB-SUM board comes with Santa Cruz connectors (J3, J4 and J5) to connect to a daughter board with

Santa Cruz interface. On the THDB-SUM, the pin of SC connector not directly connects with HSMC connector.

Owing to the limitation of number of HSMC connector I/O pins, SC connector and USB transceiver share some

I/O pins together, Please refer to Figure 3.5, those I/O pass through a Bus Switch chip first and then connect with

HSMC connector. Therefore users can only choose one function between SC connector and USB transceiver.

Users can refer to Table3.1 and use JP2 to choose a function

In addition, from the Figure 3.6, there are several level shift chips between HSMC and SC. Theses level shift

chips convert the logic levels of the signals between the HSMC and Santa Cruz connectors according to the

configurations of the headers (JP3, JP4). With this feature, users can use different I/O standards between the

HSMC host board and SC interface daughter board. Table 3.2 and Table 3.3 list the configurations of the voltage

level of the HSPROTO_IO BUS and the PROTO_IO BUS, respectively.

BUS

Switches

(U1~U2)

Santa Cruz

Connectors

(J3~J5)

Level

Shifters

(U3~U8)

USB OTG

Transceiver

(U11)

HSPROTO_IO[14..0]

HSPROTO_IO[40..15]

SWPROTO_IO[14..0]

PROTO_IO[40..0]

HSPROTO_RESET

SWPROTO_RESET

16

USB_D[7..0]

USB_CS_n

USB_CLKOUT

USB_NXT

USB_STP

USB_DIR

USB_RESET_n

14

16

27

HSPROTO_CARDSEL PROTO_CARDSEL

43

PROTO_RESET

HSMC Connector (J1)

JP1

DEV_SEL Open : USB

Close : Santa Cruz

Figure 3.5. The I/O distribution of the HSMC, Santa Cruz, and USB transceiver interface.

Table 3.1 The configuration of the Enable function on bus switch chip

JP1 setting Enable Function

Open USB OTC Transceiver

Close Santa Cruz conenctor

Board Components

11

HSMC Connector (J1)

Level

Shifters

(U3~U8)

VCCA VCCB

JP3 JP4

Santa Cruz

Connectors

(J3~J5)

PROTO_IO[40..0]

PROTO_CARDSEL

43

PROTO_RESET

43

HSPROTO_IO[40..0]

HSPROTO_CARDSEL

HSPROTO_RESET

Open : 2.5V

Close : 3.3V Open : 3.3V

Close : 5V

Figure 3.6 The diagram of the logic level transform block

Table 3.2 The configuration of the logic level on the HSPROTO_IO

BUS

JP3 setting Logic level of the HSPROTO_IO BUS

Open 2.5V

Close 3.3V

Table 3.3 The configuration of the logic level on the PROTO_IO BUS

JP4 setting Logic level of the PROTO_IO BUS

Open 3.3V

Close 5V

Finally, Figure 3.5 shows the pin-outs of the Santa Cruz connector. Detailed pin mappings between J3, J4, and

J5 to the HSMC connector is listed in Table 3.4, Table 3.5, and Table 3.6, respectively.

Note:

Because of the characteristic of the level translators, the data rate of the HSPROTO_IO and PROTO_IO

bus should be under 100 Mbps.

Board Components

12

Figure 3.7 Santa Cruz connector pin-outs

Table 3.4 The pin assignments of the Santa Cruz connector J3

SC Pin Number

SC Signal Name HSMC Pin

Number HSMC Signal Name HSMC Pin Name

3 PROTO_IO40

49 HSPROTO_IO40 HSMC_TX_N0

4 PROTO_IO29

53 HSPROTO_IO29 HSMC_TX_P1

5 PROTO_IO30

55 HSPROTO_IO30 HSMC_TX_N1

6 PROTO_IO31

59 HSPROTO_IO31 HSMC_TX_P2

7 PROTO_IO32

65 HSPROTO_IO32 HSMC_TX_P3

8 PROTO_IO33

61 HSPROTO_IO33 HSMC_TX_N2

9 PROTO_IO34

71 HSPROTO_IO34 HSMC_TX_P4

10 PROTO_IO35

67 HSPROTO_IO35 HSMC_TX_N3

11 PROTO_IO36

77 HSPROTO_IO36 HSMC_TX_P5

12 PROTO_IO37

73 HSPROTO_IO37 HSMC_TX_N4

13 PROTO_IO38

83 HSPROTO_IO38 HSMC_TX_P6

14 PROTO_IO39

79 HSPROTO_IO39 HSMC_TX_N5

Table 3.5 The pin assignments of the Santa Cruz connector J4

SC Pin Number

SC Signal Name HSMC Pin

Number HSMC Signal Name HSMC Pin Name

9 OSC 95 OSC HSMC_CLKOUT_P1

11 CLK1 97 CLK1 HSMC_CLKOUT_N1

13 CLK2 98 CLK2 HSMC_CLKIN_N1

Board Components

13

Table 3.6 The pin assignments of the Santa Cruz connector J5

SC Pin Number

SC Signal Name HSMC Pin

Number HSMC Signal Name HSMC Pin Name

1 PROTO_RESET 48 HSPROTO_RESET HSMC_RX_P0

3 PROTO_IO0 50 HSPROTO_IO0 HSMC_RX_N0

4 PROTO_IO1 54 HSPROTO_IO1 HSMC_RX_P1

5 PROTO_IO2 56 HSPROTO_IO2 HSMC_RX_N1

6 PROTO_IO3 60 HSPROTO_IO3 HSMC_RX_P2

7 PROTO_IO4 62 HSPROTO_IO4 HSMC_RX_N2

8 PROTO_IO5 66 HSPROTO_IO5 HSMC_RX_P3

9 PROTO_IO6 68 HSPROTO_IO6 HSMC_RX_N3

10 PROTO_IO7 72 HSPROTO_IO7 HSMC_RX_P4

11 PROTO_IO8 74 HSPROTO_IO8 HSMC_RX_N4

12 PROTO_IO9 78 HSPROTO_IO9 HSMC_RX_P5

13 PROTO_IO10 80 HSPROTO_IO10 HSMC_RX_N5

14 PROTO_IO11 84 HSPROTO_IO11 HSMC_RX_P6

15 PROTO_IO12 86 HSPROTO_IO12 HSMC_RX_N6

16 PROTO_IO13 90 HSPROTO_IO13 HSMC_RX_P7

17 PROTO_IO14 92 HSPROTO_IO14 HSMC_RX_N7

18 PROTO_IO15 85 HSPROTO_IO15 HSMC_TX_N6

21 PROTO_IO16 89 HSPROTO_IO16 HSMC_TX_P7

23 PROTO_IO17 91 HSPROTO_IO17 HSMC_TX_N7

25 PROTO_IO18 143 HSPROTO_IO18 HSMC_TX_P15

27 PROTO_IO19 145 HSPROTO_IO19 HSMC_TX_N15

28 PROTO_IO20 149 HSPROTO_IO20 HSMC_TX_P16

29 PROTO_IO21 151 HSPROTO_IO21 HSMC_TX_N16

31 PROTO_IO22

155 HSPROTO_IO22

HSMC_CLKOUT_P2

32 PROTO_IO23

134 HSPROTO_IO23

HSMC_RX_N13

33 PROTO_IO24

138 HSPROTO_IO24

HSMC_RX_P14

35 PROTO_IO25

140 HSPROTO_IO25

HSMC_RX_N14

36 PROTO_IO26

144 HSPROTO_IO26

HSMC_RX_P15

37 PROTO_IO27

146 HSPROTO_IO27

HSMC_RX_N15

38 PROTO_CARDSEL

150 HSPROTO_CARDSEL

HSMC_RX_P16

39 PROTO_IO28

152 HSPROTO_IO28

HSMC_RX_N16

Board Components

14

3.3 USB On-The-Go transceiver

This section describes the USB On-The-Go transceiver on the THDB-SUM board

The THDB-SUM is equipped with a NXP ISP1504C USB On-The-Go transceiver (U11) and Mini USB AB type

receptacle connector (J8) to provide USB interface to the HSMC interface host board. The ISP1504 is a

Universal Serial Bus (USB) On-The-Go (OTG) transceiver that is fully compliant with Universal Serial Bus

Specification Rev. 2.0, On-The-Go Supplement to the USB 2.0 Specification Rev. 1.3 and UTMI+ Low Pin

Interface (ULPI) Specification Rev. 1.1.

The pervious section, Santa Cruz Connector, has mentioned that USB transceiver and Santa Cruz connector

share the I/Os which connect to HSMC connector, which means users can only choose o

ne function between

USB and Satan Cruz interface, If users would like to choose the function of USB transceiver, please turn on

JP2. For more detailed information about this transceiver, please refer to the datasheet which can be found in

the NXP’s website.

In addition, for OTG implementations, a 2-pin header named JP1 is connected with ID (identification) pin of

the USB OTG transceiver and micro-USB receptacle. As shown in Figure 3.8, The logic level of the ID pin on

the USB OTG transceiver can be configured to logic high or low via JP1. As defined in On-The-Go supplement

to the USB 2.0 specification Rev. 1.3, the ID pin dictates the initial role of the link. If ID is detected as HIGH,

the link must assume the role of a peripheral. If ID is detected as LOW, the link must assume a

host role. Table 3.7 shows the JP1 configuration setting for the ID.

Finally, the detailed pin mappings between the USB On-The-Go transceiver and the HSMC connector are

shown in Table3.8.

Table 3.7 The configuration of the ID pin

JP2 setting Host or peripheral role

Open Peripheral

Close Host

Board Components

15

NXP

ISP1504C

(U11)

DM

DP

ID

Jack-Mini- USB-AB

(J8)

JP2 Close = Host

Open = Peripheral

DATA[7..0]

CS

RESET

DIR

STP

NXT

XTAL1

USB_DIR

USB_STP

USB_NXT

XTAL1

USB _D[7..0]

USB_CS_n

USB_RESET_n

XTAL2 XTAL2

USB_CLKOUT CLOCK

26MHZ

X1

HSMC Connector

(J1)

VBUS

USB

Bus

Switch

(U1,U2)

HSPROTO_IO

JP1 Open

Figure 3.8 The block diagram of the USB OTG transceiver and HSMC connector

Table 3.8 The pin assignments of the USB OTG Transceiver U11

USB Pin

Number USB Signal Name HSMC Pin

Number HSMC Signal Name

HSMC Pin

Name

1 USB_D0 48 HSPROTO_RESET HSMC_RX_P0

17 USB_RESET_n 86 HSPROTO_IO12 HSMC_RX_N6

19 USB_DIR 84 HSPROTO_IO11 HSMC_RX_P6

20 USB_STP 80 HSPROTO_IO10 HSMC_RX_N5

21 USB_NXT 78 HSPROTO_IO9 HSMC_RX_P5

23 USB_D7 74 HSPROTO_IO8 HSMC_RX_N4

24 USB_D6 72 HSPROTO_IO7 HSMC_RX_P4

25 USB_D5 68 HSPROTO_IO6 HSMC_RX_N3

26 USB_D4 66 HSPROTO_IO5 HSMC_RX_P3

27 USB_CLKOUT 62 HSPROTO_IO4 HSMC_RX_N2

28 USB_D3 60 HSPROTO_IO3 HSMC_RX_P2

29 USB_CS_n 56 HSPROTO_IO2 HSMC_RX_N1

31 USB_D2 54 HSPROTO_IO1 HSMC_RX_P1

32 USB_D1 50 HSPROTO_IO0 HSMC_RX_N0

Board Components

16

3.4 Mictor Connector

This section describes how to use the Mictor connector on the THDB-SUM board

The Mictor connector (J2) can be used for logic analysis on the HSMC-interfaced host board by connecting an

external scope or a logic analyzer to it. Figure 3.9 shows the pin-outs of the Mictor connector. Table 3.9 shows

the detailed pin mappings between the Mictor connector and the HSMC connector.

Figure 3.9 Mictor connector pin-outs

Table 3.9 The pin assignments of the Mictor connector J2

Mictor

Connector

Pin Number

Mictor Connector

Signal Name

HSMC Pin

Number HSMC Signal Name

HSMC Pin Name

5 MICTOR_CLK 156 MICTOR_CLK HSMC_CLKIN_P2

6 TR_CLK 157 TR_CLK HSMC_CLKOUT_N2

7 MICTOR_D24 132 MICTOR_D24 HSMC_RX_P13

8 MICTOR_D13 121 MICTOR_D13 HSMC_TX_N11

9 MICTOR_D23 128 MICTOR_D23 HSMC_RX_N12

10 MICTOR_D12 125 MICTOR_D12 HSMC_TX_P12

13 MICTOR_D22 126 MICTOR_D22 HSMC_RX_P12

16 MICTOR_D11 127 MICTOR_D11 HSMC_TX_N12

18 MICTOR_D10 131 MICTOR_D10 HSMC_TX_P13

20 MICTOR_D9 133 MICTOR_D9 HSMC_TX_N13

22 MICTOR_D8 137 MICTOR_D8 HSMC_TX_P14

23 MICTOR_D21 122 MICTOR_D21 HSMC_RX_N11

Board Components

17

24 MICTOR_D7 139 MICTOR_D7 HSMC_TX_N14

25 MICTOR_D20 120 MICTOR_D20 HSMC_RX_P11

26 MICTOR_D6 119 MICTOR_D6 HSMC_TX_P11

27 MICTOR_D19 116 MICTOR_D19 HSMC_RX_N10

28 MICTOR_D5 109 MICTOR_D5 HSMC_TX_N9

29 MICTOR_D18 114 MICTOR_D18 HSMC_RX_P10

30 MICTOR_D4 107 MICTOR_D4 HSMC_TX_P9

31 MICTOR_D17 110 MICTOR_D17 HSMC_RX_N9

32 MICTOR_D3 115 MICTOR_D3 HSMC_TX_N10

33 MICTOR_D16 108 MICTOR_D16 HSMC_RX_P9

34 MICTOR_D2 113 MICTOR_D2 HSMC_TX_P10

35 MICTOR_D15 104 MICTOR_D15 HSMC_RX_N8

36 MICTOR_D1 103 MICTOR_D1 HSMC_TX_N8

37 MICTOR_D14 102 MICTOR_D14 HSMC_RX_P8

38 MICTOR_D0 101 MICTOR_D0 HSMC_TX_P8

11 MICTOR_TDO 37 HSMC_TDO HSMC_TDO

15 MICTOR_TCK 35 HSMC_TCK HSMC_TCK

17 MICTOR_TMS 36 HSMC_TMS HSMC_TMS

19 MICTOR_TDI 38 HSMC_TDI HSMC_TDI

To use this interface, user needs to configure the JTAG interface on the HSMC interface host board. For

example, the steps of controlling the Cyclone III start board using Mictor interface is shown below:

1. Connecting the THDB-SUM board to the Cyclone III Start Board.

2. Removing the jumpers of JP1 and JP2 of the Cyclone III Start Board to connect the JTAG interface

between Cyclone III FPGA and the THDB-SUM board.

3. Short the TDI and TDO pins of the JTAG connector(J4), as shown in Figure 3.10

4. Disable the built-in USB blaster by shorting JP8 on the Cyclone III Starter Board

The above FOUR steps will make a closed JTAG chain as shown in Figure 3.11

Board Components

18

J4 Short

Close JP8

With jumper

Short TDI and TDO

pin of the J4

Open JP1 nad JP2

Figure 3.10 The configuration of the Cyclone III start board for controlling the JTAG chain using the Mictor

connector

Cyclone III

JTAG_TDO

LF_TDO

ADG3304

CII_TDO

OPEN

LF_TDI

LF_TDO

HSMC

HSMC_TDO

HSMC_TDI

JP1

HSMC_TDI

HSMC_TDO

TDOTDI

J4

TDI

TDO

JP2

VCC25

MAX 3128

Built-in

Blaster

ADG3308

TDI

TDO

TDI

TDO

JP8

USB3V

Cyclone III Start BoardTHDB-SUM Board

SHORT

Mictor connector

J2

MICOTR_TDI

MICOTR_TDO

MICOTR_TDI

MICOTR_TDO

OPEN

CLOSE

Figure 3.11 The JTAG chain between the THDB-SUM board and Cyclone III Start Board

3.5 SD Card Interface

This section describes the SD Card Interface on the THDB-SUM board

The THDB-SUM has a SD card socket and can be accessed as optional external memory in both SPI and

1-bit SD mode. Table X shows the pinout of the SD card socket with HSMC connector. Figure 3.12 and Table

3.10 shows the pin connection and pin-out between the Mictor connector and HSMC connector, respectively.

This manual suits for next models

1

Table of contents

Other Terasic PCI Card manuals

Popular PCI Card manuals by other brands

Moxa Technologies

Moxa Technologies CP-104JU V2 Quick installation guide

National Instruments Corporation

National Instruments Corporation IMAQ PCI-1408 Getting started

IOGear

IOGear GIC250U user manual

Linksys

Linksys WM821-M user manual

HOLT

HOLT ADK-6130PCIe user guide

StarTech.com

StarTech.com PCI1394_2 instruction manual

Conrad

Conrad 1000182 operating instructions

Kontron

Kontron CP605 manual

SMART Embedded Computing

SMART Embedded Computing PCIE-7217 Installation and use

Kofax

Kofax KF-4100 Installation and configuration guide

Teltonika

Teltonika TMP-102 user manual

ADLINK Technology

ADLINK Technology PCIe-FIW Series user manual