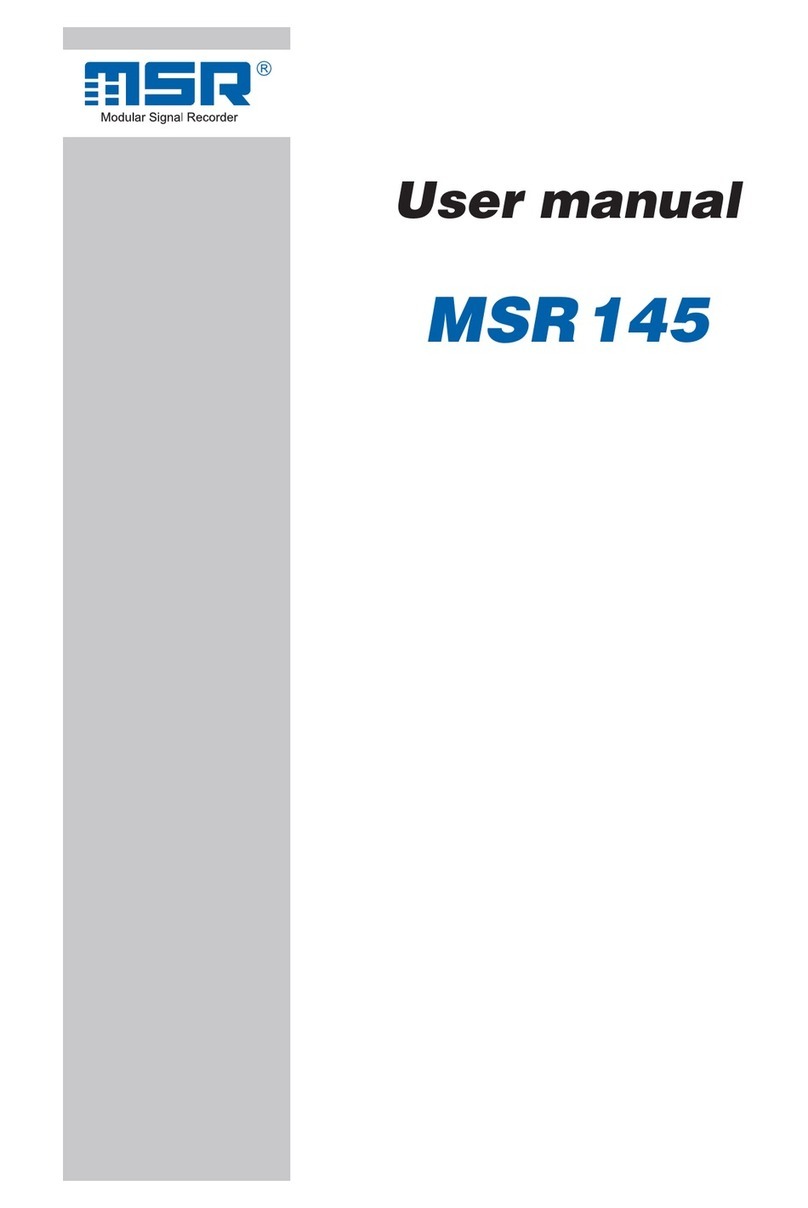

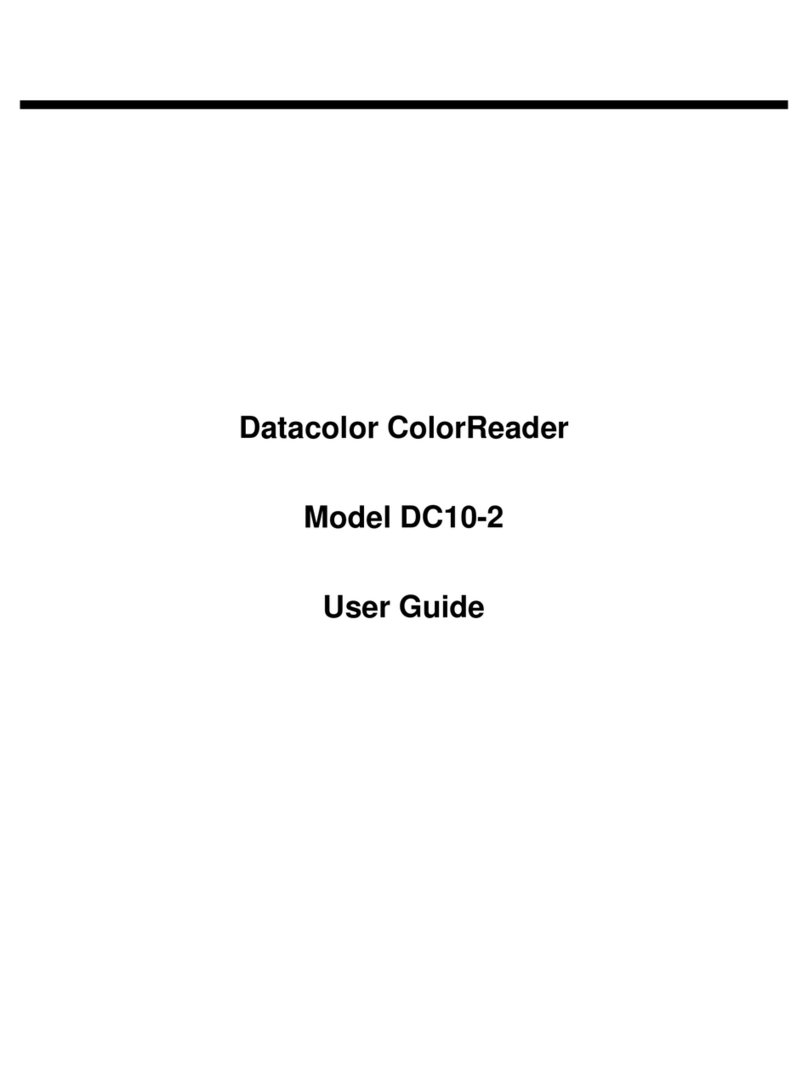

VIT+(OV) Accuracy (%)

Frequency (%)

-0.4 -0.3 -0.2 -0.1 0 0.1 0.2 0.3 0.4

0

5

10

15

20

25

30

35

D004

RESET

VDD

SENSE MR

CT

GND

RESET

VCORE

Processor

OV Threshold

UV Threshold

Optional

TPS3703

1

Monitor Voltage

10k

2

34

5

6

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

TPS3703

SBVS249A –MAY 2020–REVISED JUNE 2020

TPS3703 High Accuracy Overvoltage and Undervoltage Reset IC With Time Delay and

Manual Reset

1

1 Features

1• Input voltage range: 1.7 V to 5.5 V

• Undervoltage lockout (UVLO): 1.7 V

• Low quiescent current: 7 µA (Max)

• High threshold accuracy:

– ± 0.25% (typical)

– ± 0.7% (–40°C to +125°C)

• Fixed window threshold levels

– 50-mV steps from 500 mV to 1.3 V

– 1.5 V, 1.8 V, 2.5 V, 2.8 V, 2.9 V 3.3 V, 5 V

– Available in UV threshold only

– Window tolerance available from ±3% to ±7%

• User adjustable voltage threshold levels

• Internal glitch immunity and hysteresis

• Fixed time delay options: 50 µs, 1 ms, 5 ms, 10

ms, 20 ms, 100 ms, 200 ms

• Programmable time delay option with a single

external capacitor

• Open-drain active low UV and OV monitor

• RESET voltage latching output mode

2 Applications

•Motor drives

•Factory automation and control

•Home theater and entertainment

•Grid infrastructure

•Data center and enterprise computing

Integrated Overvoltage and Undervoltage

Detection

3 Description

The TPS3703 device is an integrated overvoltage

(OV) and undervoltage (UV) monitor or reset IC in

industry’s smallest 6-pin DSE package. This highly

accurate voltage supervisor is ideal for systems that

operate on low-voltage supply rails and have narrow

margin supply tolerances. Low threshold hysteresis

prevent false reset signals when the monitored

voltage supply is in its normal range of operation.

Internal glitch immunity and noise filters further

eliminate false resets resulting from erroneous

signals.

The TPS3703 does not require any external resistors

for setting overvoltage and undervoltage reset

thresholds, which further optimizes overall accuracy,

cost, solution size, and improves reliability for safety

systems. The Capacitor Time (CT) pin is used to

select between the two available reset time delays

designed into each device and also to adjust the

reset time delay by connecting a capacitor. A

separate SENSE input pin and VDD pin allow for the

redundancy sought by high-reliability systems.

This device has a low typical quiescent current

specification of 4.5 µA (typical). The TPS3703 is

suitable for industrial applications and applications

that require accurate undervoltage and overvoltage

monitoring.

Device Information(1)

PART NUMBER PACKAGE BODY SIZE (NOM)

TPS3703 WSON (6) 1.50 mm × 1.50 mm

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

Typical Overvoltage Accuracy Distribution