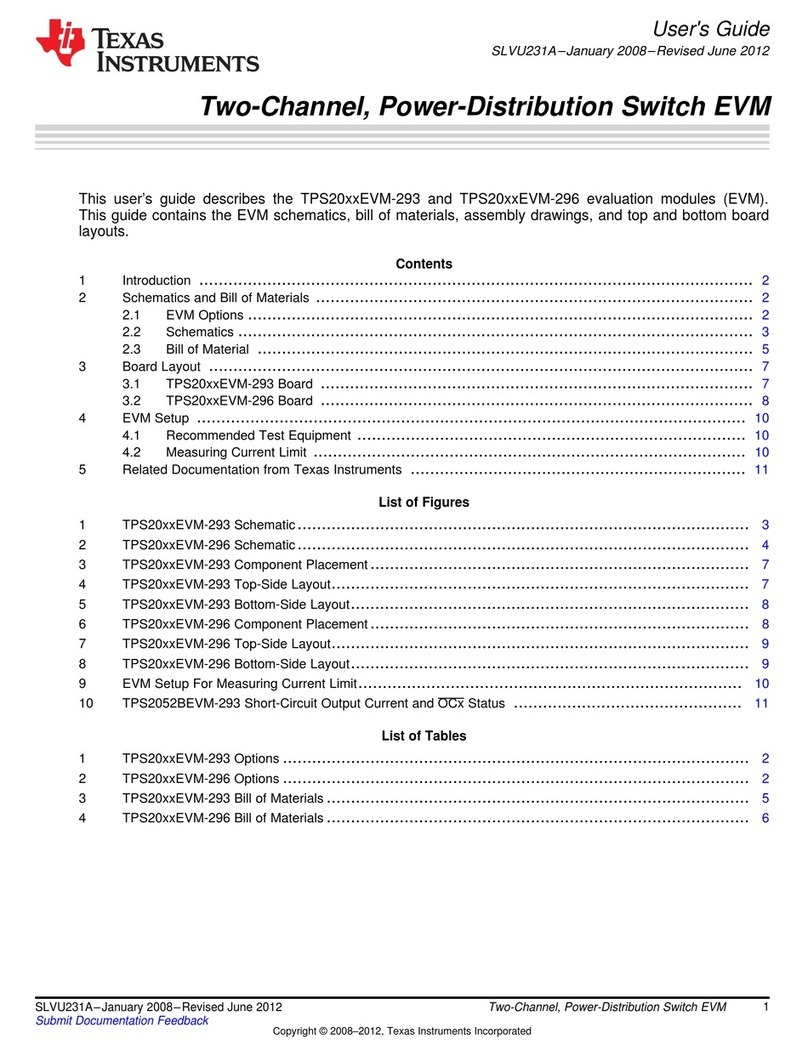

User's Guide

SLUU826–January 2012

Using the TPS53310EVM-755, A 3-A Eco-mode™

Integrated Switcher With Master-Slave

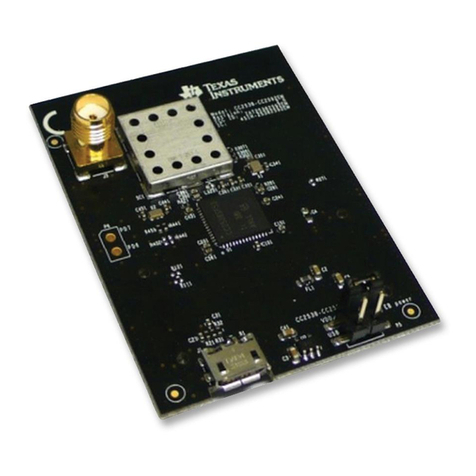

The TPS53310EVM-755 evaluation module (EVM) is a high-efficiency evaluation platform with two

TPS53310 3-A, integrated FET, step-down converters working in a Master-Slave synchronization scheme.

The two outputs are 1.5 V/3 A (master) and 1.2 V/3 A (slave) from a 3.3-V or 5-V input bus. The EVM

uses the TPS53310 synchronous buck controller with integrated switcher.

Contents

1 Description ................................................................................................................... 3

1.1 Typical Applications ................................................................................................ 3

1.2 Features ............................................................................................................. 3

2 Electrical Performance Specifications .................................................................................... 3

3 Schematic .................................................................................................................... 5

4 Test Setup ................................................................................................................... 6

4.1 Test Equipment ..................................................................................................... 6

4.2 Recommended Test Setup ....................................................................................... 7

5 Configuration ................................................................................................................ 8

5.1 5Vin Option (J1: 5Vin Option) .................................................................................... 8

5.2 Mode Selection (J2: MST Mode) ................................................................................. 8

5.3 Mode Selection (J7: SLV Mode) ................................................................................. 8

5.4 Synchronization (J5: SYNC) ...................................................................................... 8

5.5 Master Enable (J4: EN_MST) .................................................................................... 9

5.6 Slave Enable (J9: EN_SLV) ...................................................................................... 9

6 Test Procedure .............................................................................................................. 9

6.1 Line/Load Regulation and Efficiency Measurement Procedure .............................................. 9

6.2 Loop Gain/Phase Measurement ................................................................................. 9

6.3 List of Test Points ................................................................................................ 10

6.4 Equipment Shutdown ............................................................................................ 10

7 Performance Data and Typical Characteristic Curves ................................................................ 10

7.1 Efficiency .......................................................................................................... 11

7.2 Load Regulation .................................................................................................. 11

7.3 Line Regulation ................................................................................................... 12

7.4 1.5-V Output Ripple .............................................................................................. 12

7.5 1.5-V Switching Node at Full Load ............................................................................. 13

7.6 1.5-V Switching Node at No Load .............................................................................. 13

7.7 Master-Slave 180°Synchronization ............................................................................ 14

7.8 1.5-V Master Turnoff During Master-Slave Synchronization ................................................ 14

7.9 1.5-V Output Transient ........................................................................................... 15

7.10 1.5-V Turnon Waveform ......................................................................................... 15

7.11 1.5-V Turnoff Waveform ......................................................................................... 16

7.12 1.5-V Hiccup OCP Waveform ................................................................................... 16

7.13 1.5-V Bode Plot ................................................................................................... 17

7.14 EVM Top Board Thermal Image ................................................................................ 17

8 EVM Assembly Drawings and PCB Layout ............................................................................ 18

9 Bill of Materials ............................................................................................................. 22

Eco-mode is a trademark of Texas Instruments.

1

SLUU826–January 2012 Using the TPS53310EVM-755, A 3-A Eco-mode™Integrated Switcher With

Master-Slave

Submit Documentation Feedback Copyright ©2012, Texas Instruments Incorporated