bdi

RDI

JTAG interface for RDI Debuggers, BDI1000 User Manual 2

© Copyright 1999-2003 by ABATRON AG V 1.10

1 Introduction .................................................................................................................................3

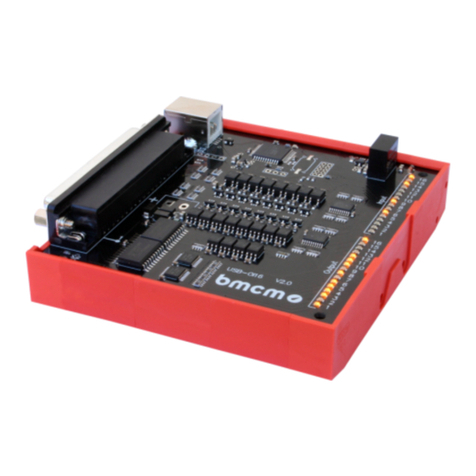

1.1 BDI1000.................................................................................................................................3

2 Installation ...................................................................................................................................4

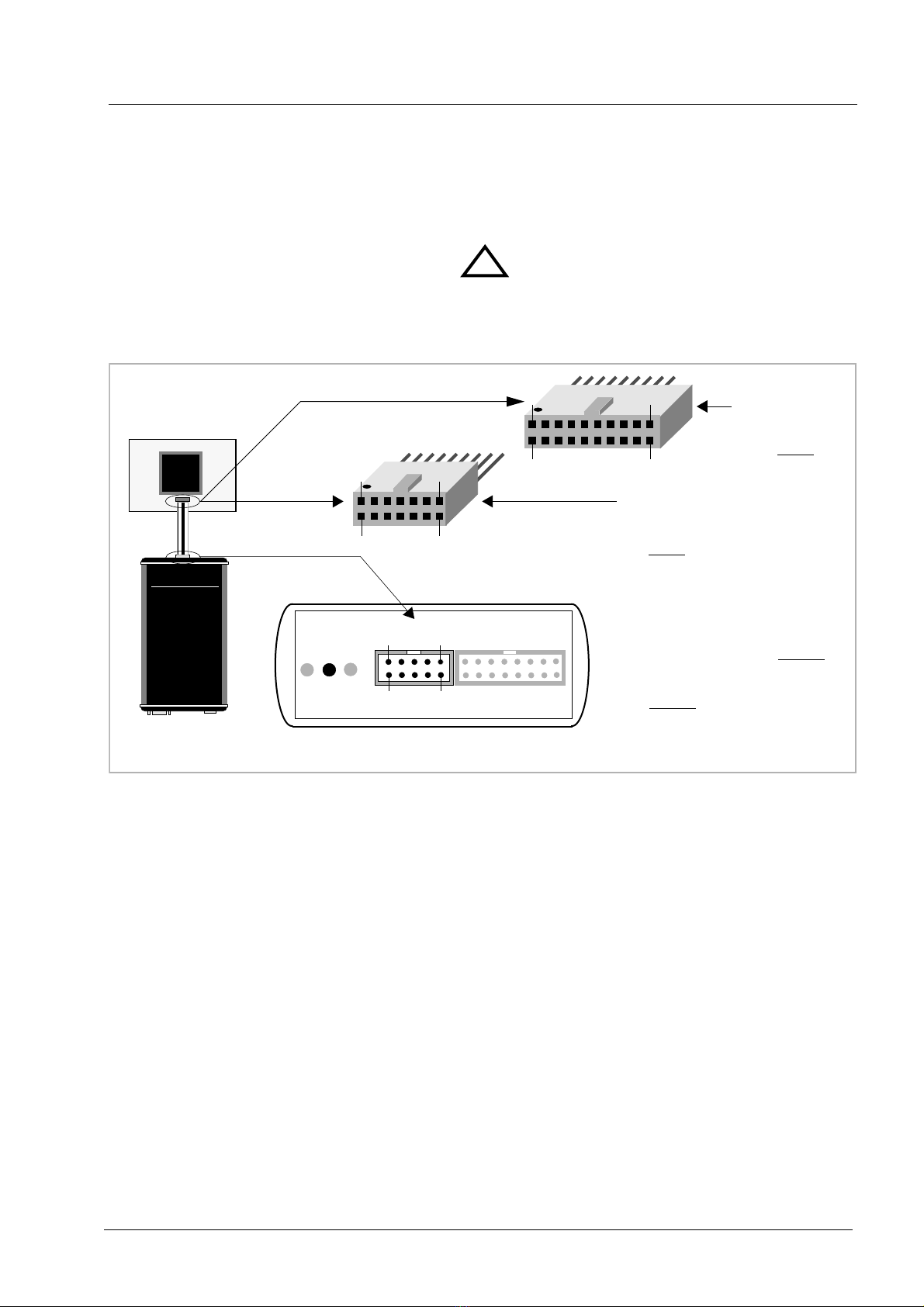

2.1 Connecting the BDI1000 to Target.........................................................................................4

2.1.1 Changing Target Processor Type .................................................................................6

2.1.2 Adaptive Clocking.........................................................................................................7

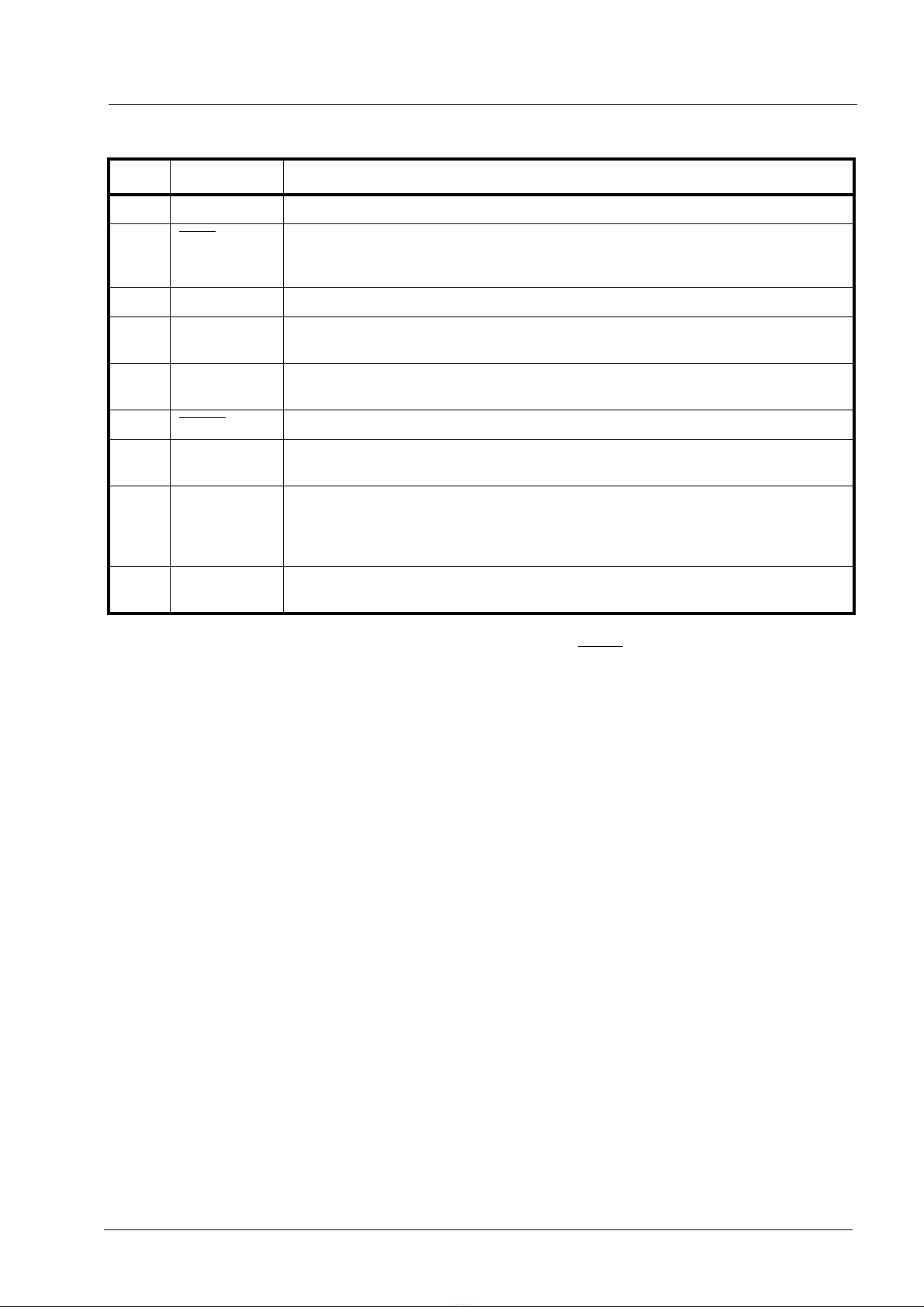

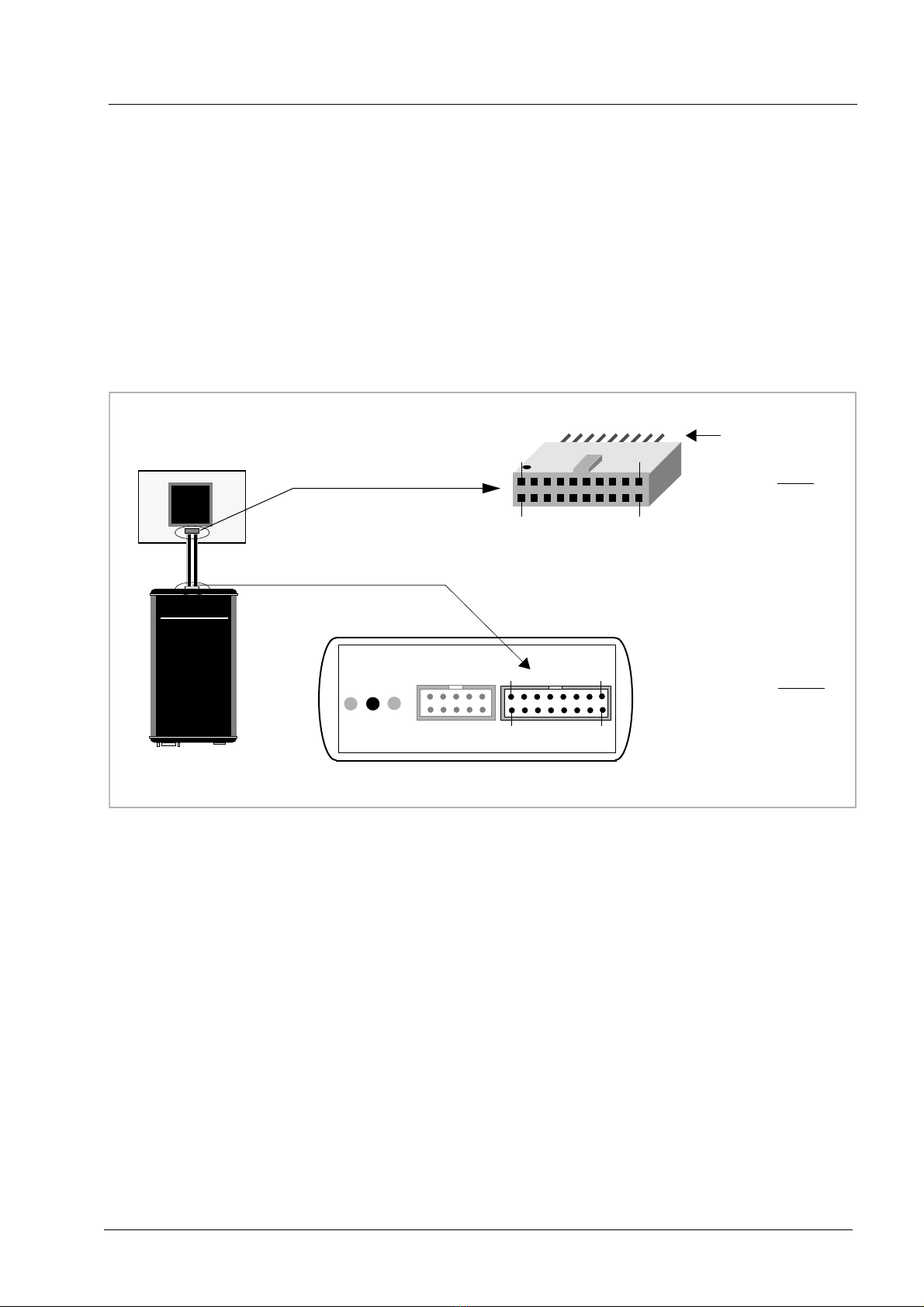

2.2 Connecting the BDI1000 to Power Supply.............................................................................9

2.2.1 External Power Supply.................................................................................................9

2.2.2 Power Supply from Target System.............................................................................10

2.3 Status LED «MODE»...........................................................................................................11

2.4 Connecting the BDI1000 to Host.........................................................................................12

2.4.1 Serial line communication..........................................................................................12

2.4.2 Ethernet communication ............................................................................................13

2.5 Installation of the Configuration Software............................................................................14

2.6 Configuration .......................................................................................................................15

2.6.1 BDI1000 Setup/Update..............................................................................................15

3 Init List........................................................................................................................................17

3.1 Init CP15 Registers..............................................................................................................19

4 BDI working modes...................................................................................................................21

4.1 Startup Mode.......................................................................................................................23

4.1.1 Startup mode RESET ................................................................................................23

4.1.2 Startup Mode STOP...................................................................................................23

4.1.3 Startup mode RUN.....................................................................................................23

5 Working with RDI Debuggers ...................................................................................................24

5.1 ADW/AXD from ARM Ltd.....................................................................................................24

5.1.1 Configuration..............................................................................................................24

5.1.2 Implementation notes.................................................................................................25

5.2 BDI Direct Commands.........................................................................................................26

5.2.1 Target.Reset...............................................................................................................26

5.2.2 Flash.Setup................................................................................................................27

5.2.3 Flash.Erase................................................................................................................28

5.2.4 Flash.Load .................................................................................................................28

5.2.5 Flash.Idle....................................................................................................................28

5.3 Download to Flash Memory.................................................................................................29

6 Telnet Interface ..........................................................................................................................31

7 Specifications............................................................................................................................32

8 Environmental notice................................................................................................................33

9 Declaration of Conformity (CE)................................................................................................33

10 Warranty...................................................................................................................................34

Appendices

A Troubleshooting........................................................................................................................35

B Maintenance..............................................................................................................................36

C Trademarks................................................................................................................................38