&$(1

&$(1

Document type: Title: Revision date: Revision:

User's Manual (MUT) Mod. V791, ICARUS 32-channel analog board 27/05/99 2

NPO: Filename: Number of pages: Page:

00100/98:V791x.MUTx/02 V791MN4.DOC 17 7

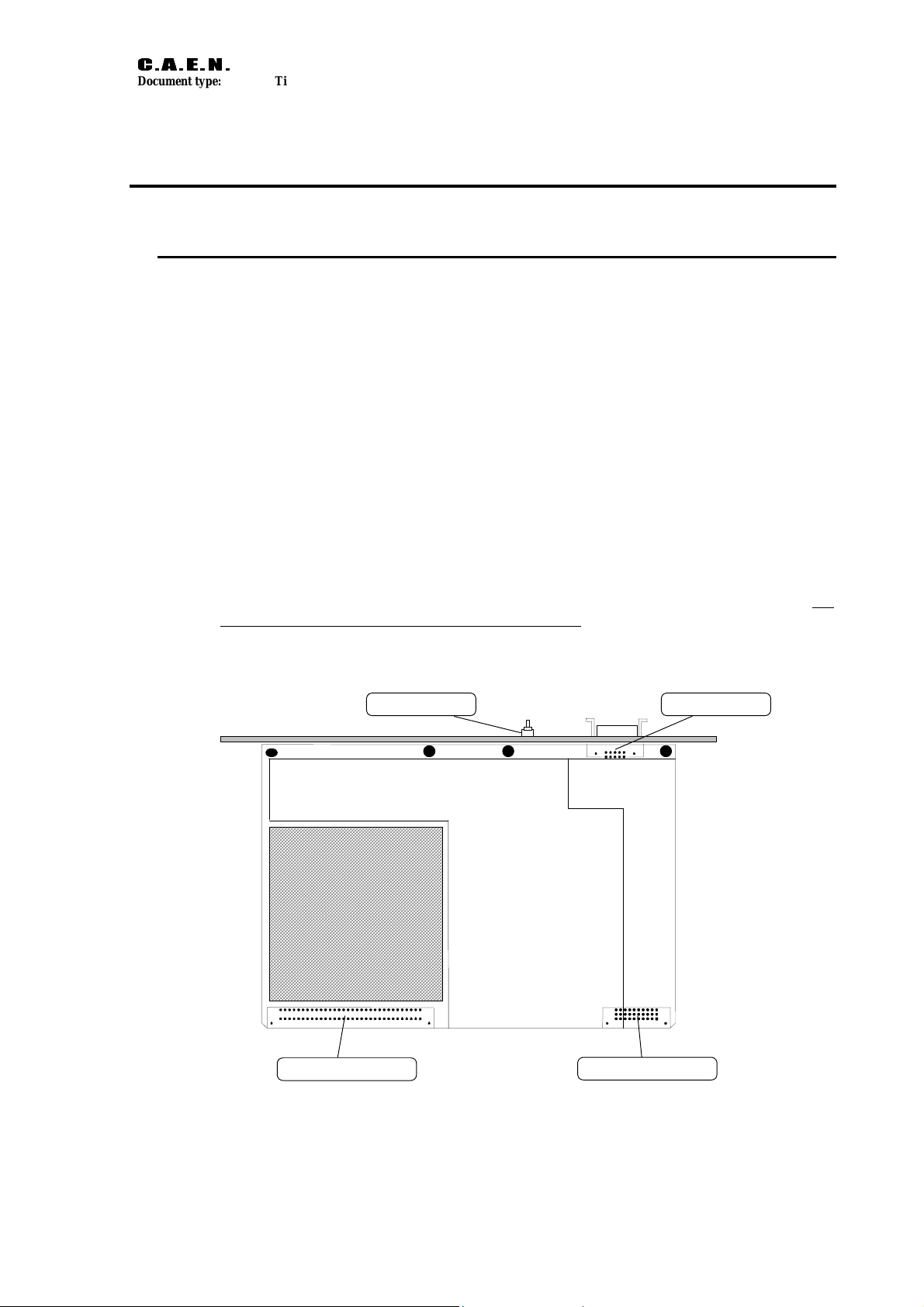

Fig. 2.1 shows a detailed block diagram of the V791 module.

The first section, constituted by the preamplifiers and the shapers, provides the

conversion from current to voltage of the input signals and their shaping. The current

signals coming from the detector are converted into voltage signals by the preamplifiers.

These are constituted by two JFET followed by an ASIC specially developed by CAEN

Microelectronics. The output voltage signals are then sent to the shapers having two

1-µsec time constants or one 0.27-µsec time constant for the Mod. V791C and

Mod. V791Q, respectively. In order to allow a check of the channel operation the

preamplifiers have a test input coupled through a 1-pF capacitor.

The signals coming out the shapers are sent to the input of the analog multiplexers in

such an order as to keep the same signal sequence of the input connector. Moreover, the

Σout output connector on the front panel provides the sum of all the shaper outputs.

The second section is constituted by four blocks, each controlling 8 channels. Each block

comprehends two analog multiplexers, a fast operational amplifier and an ADC which is

connected to the input of the digital multiplexer. The 8-channel block connected to the

input A of the digital multiplexer relates to the odd channels, while that connected to the

input B relates to the even ones.

The parallel-connected outputs of the analog multiplexer are amplified by the fast

operational amplifier which has also the function of shifting the ADC baseline by adding a

DC level. The external DAC (VDAC control signal) allows to set this baseline correctly,

according to the type of signal to be converted. The operational amplifier has as well a

capacitor which can be used for limiting the bandwidth in order to reduce the noise,

although this implies a deterioration of the cross-talk. This can be done via hardware by

soldering a capacitor on the printed board (capacitor CBL on the printed board; please

refer to Fig. 4.1).

The ADC is a 10-bit 20-MHz converter with external references.

The third section is the digital one and comprehends the digital multiplexers, the control

logic and the output link.

The control logic, hosted in a PAL device (MAX7032-15), generates the multiplexing and

digitizing signals which are sent through the digital multiplexer to the input of the 40-MHz

serial link.

The external control signals accepted by the module are VDAC, +TPULSE, -TPULSE,

TPE_EN, TPO_EN, B_CLK, /B_CLK and EN_BRD.

The VDAC control signal allows to set the baseline to be added to the input of the fast

operational amplifier, according to the type of signal to be converted.

The differential test pulse (+TPULSE and -TPULSE signals) comes from the backplane.

The signal coming from the backplane has to be attenuated by a factor 10 before being

sent to the preamplifiers.

The TPE_EN and TPO_EN signals allow to enable the test pulsing on the even and odd

channels, respectively. Since the test pulse is directly connected to the input of the

preamplifiers, when the test pulse is not used, it is necessary to connect it to ground

through a very low impedance by disabling the TPE_EN and TPO_EN signals.

The differential clock signal (B_CLK and /B_CLK) is the external clock used to

synchronise all the V791 modules in the crate. The selection of the clock, external or

internal, can be made by means of a soldering (soldering pad S2 on the printed board;

please refer to Fig. 4.1). The external clock is the default setting.

The EN_BRD logic signal is used to force the control logic in the reset state and,

consequently, to stop the digitization of the signals.

All these control signals are sent to the board via the relevant pins of the power supply

connector.