PRELIMINARY

Document type: Title: Revision date: Revision:

User's Manual (MUT) Mod. V1729 4 Channel 12 Bit Sampling ADC 22/06/2005 3

NPO: Filename: Number of pages: Page:

00109/04:V1729.MUTx/03 V1729_REV3.DOC 38 3

TABLE OF CONTENTS

1. GENERAL DESCRIPTION.......................................................................................................................5

1.1 OVERVIEW .............................................................................................................................................5

1.2 SAMPLING FREQUENCY ..........................................................................................................................6

1.3 INPUT SIGNALS, DYNAMIC RANGE..........................................................................................................6

2. OPERATING MODES...............................................................................................................................7

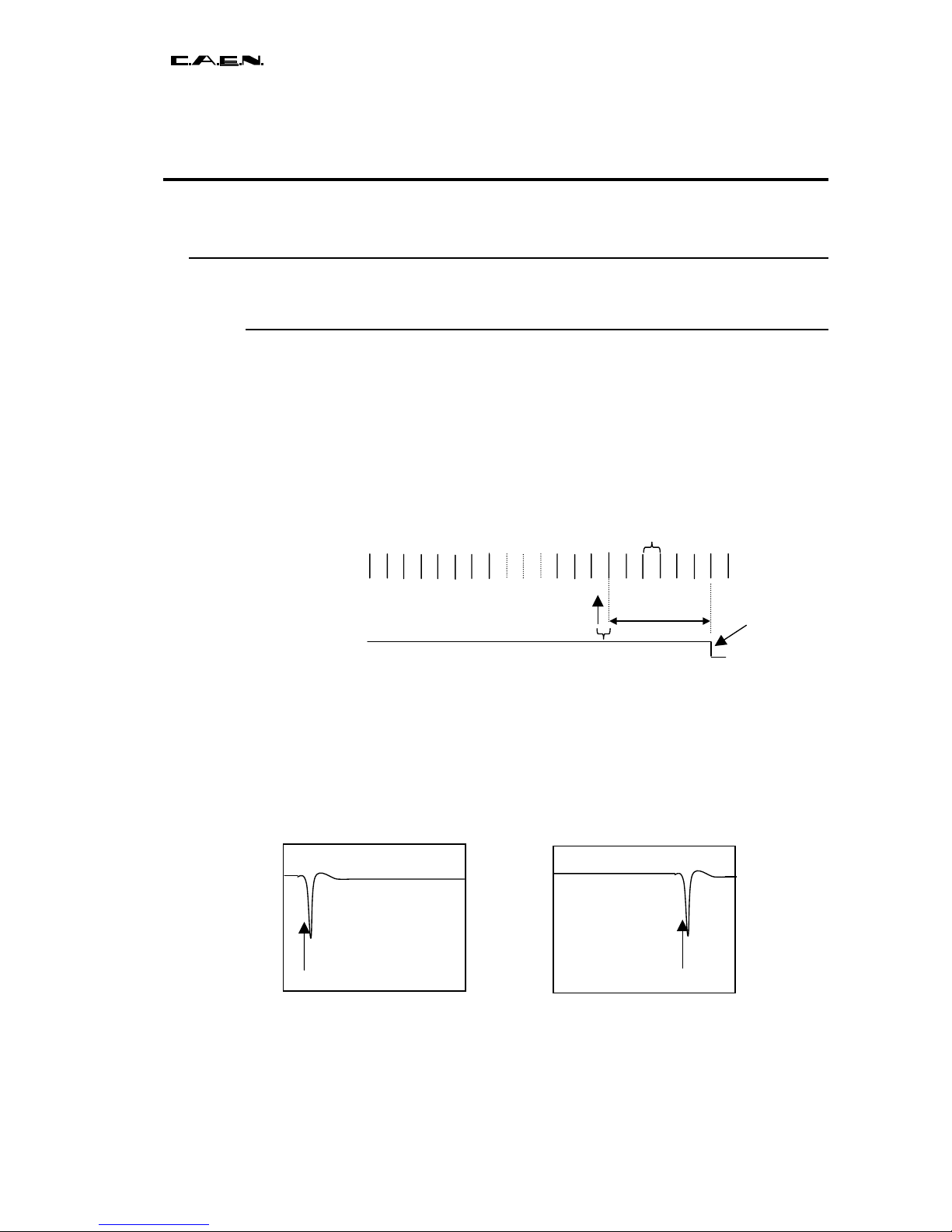

2.1 DEFINITION OF THE ACQUISITION WINDOW. TRIGGER MODES.................................................................7

2.1.1 Principle, PRETRIG, POSTTRIG..................................................................................................7

2.1.2 Trigger sources..............................................................................................................................8

2.1.3 Trigger edge ..................................................................................................................................8

2.1.4 TRIGOUT signal ...........................................................................................................................8

2.2 VALIDATION OF THE TRIGGER BY A SECOND SUBSEQUENT SIGNAL.........................................................9

2.3 DEAD TIME AT RESTARTING OF THE ACQUISITION; PRETRIG.................................................................10

2.4 STANDARD ACQUISITION SEQUENCE.....................................................................................................10

2.5 CORRECTION OF DATA..........................................................................................................................11

2.5.1 Correction of the pedestals..........................................................................................................12

2.5.2 Temporal corrections ..................................................................................................................13

3. SYNCHRONIZATIONS AND CALIBRATIONS.................................................................................16

3.1 SYNCHRONIZATION BETWEEN THE CHANNELS......................................................................................16

3.1.1 Channels from the same board....................................................................................................16

3.1.2 Channels situated on different boards........................................................................................16

3.2 SYNC_OUT AND BUSY SIGNALS ......................................................................................................16

3.3 CALIBRATIONS .....................................................................................................................................17

3.3.1 Calibration of the interpolator....................................................................................................17

3.3.2 Calibration of the pedestals.........................................................................................................20

3.3.3 Temporal calibration between different channels.......................................................................20

4. TECHNICAL SPECIFICATIONS..........................................................................................................21

4.1 PACKAGING..........................................................................................................................................21

4.2 SAMPLING FREQUENCY ........................................................................................................................21

4.3 INPUT SIGNALS, DYNAMIC RANGE........................................................................................................21

4.4 FRONT PANEL.......................................................................................................................................22

4.5 MECHANICAL AND ELECTRICAL STANDARDS........................................................................................23

4.5.1 Mechanical standard...................................................................................................................23

4.5.2 Electrical interfaces.....................................................................................................................23

4.5.3 Summary of front panel signals...................................................................................................24

4.5.4 Supplies .......................................................................................................................................25

4.5.5 Pinout of the non-standard connectors .......................................................................................25

4.5.6 Straps and resistor network sockets ............................................................................................26

4.5.7 Implementation of differential inputs ..........................................................................................26

4.5.8 Using a shifted input range .........................................................................................................27

4.6 INTERFACES .........................................................................................................................................28

4.6.1 VME interface..............................................................................................................................28

4.6.2 GPIB Interface.............................................................................................................................28

4.7 READING OF THE DATA IN THE RAM, MAPPING....................................................................................29

4.8 LIST OF THE SUB-ADDRESSES................................................................................................................31

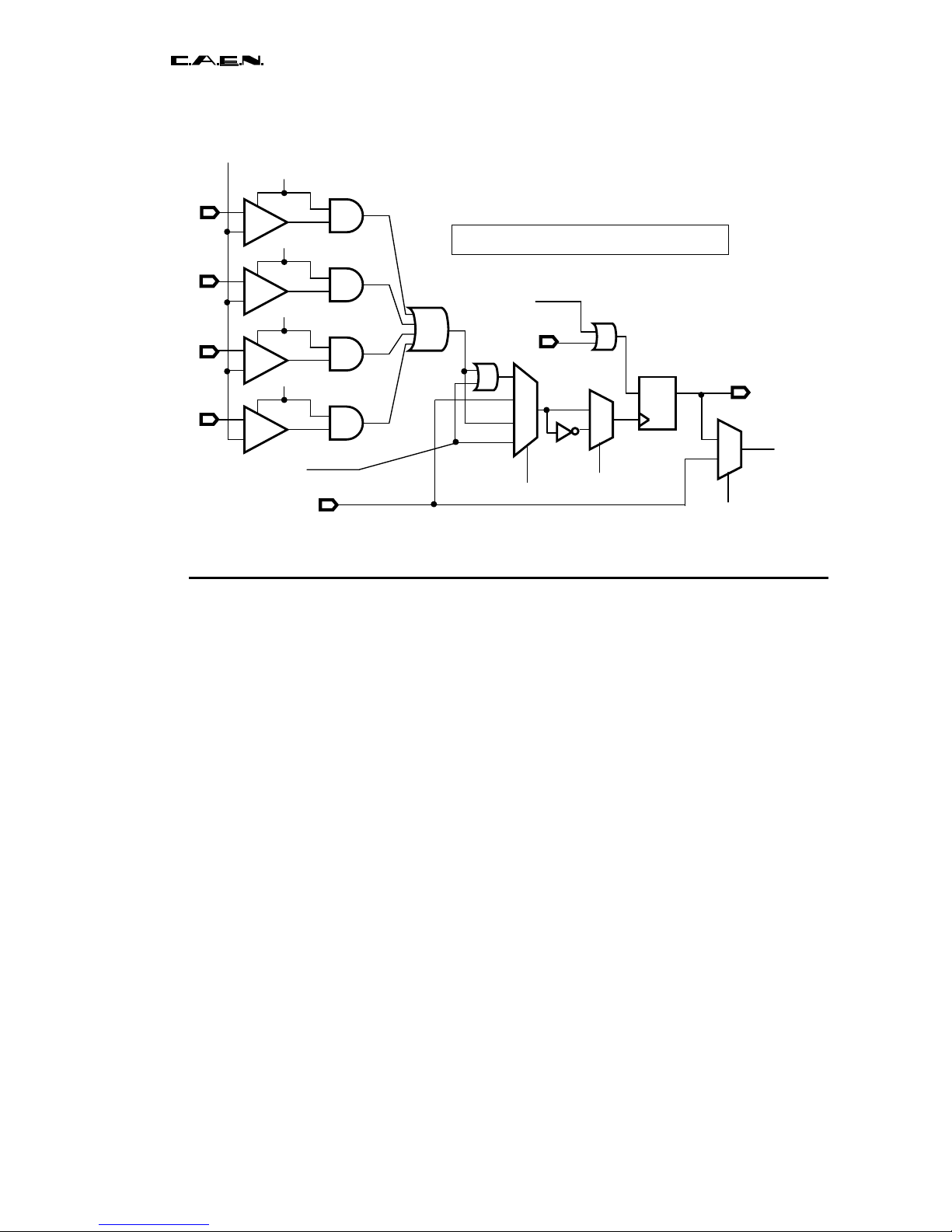

4.9 SYNOPSIS OF THE BOARD......................................................................................................................35

5. SPECIFICATIONS AND PERFORMANCES.......................................................................................37

6. BIBLIOGRAPHY .....................................................................................................................................38