Centrality Atlas Operating instructions

.

© 1999-2003 Centrality Commnications, Inc.

2520 Mission College Blvd. Suite #103, Santa Clara, CA 95054

Atlas™

Programming Guide

Preliminary Revision 0.6, April 2003

**Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

Atlas™ Programming Guide **Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

- 1-

Table of Contents

1Introduction ..........................................................................................................................................7

1.1 Documentation Conventions ........................................................................................................ 7

1.2 Referenced Documents................................................................................................................ 8

1.3 Architectural Overview.................................................................................................................. 9

1.4 Key Features .............................................................................................................................. 11

2RISC Subsystem................................................................................................................................12

2.1 Operation Overview.................................................................................................................... 12

2.2 RISC Address Mapping.............................................................................................................. 12

2.3 Boot-up Control .......................................................................................................................... 14

2.4 Wait State Control ...................................................................................................................... 15

2.5 Write Pulse Control..................................................................................................................... 16

2.6 Timeout Control .......................................................................................................................... 17

3DSP Subsystem.................................................................................................................................18

3.1 Operation Overview.................................................................................................................... 18

3.2 DSP Memory Address Mapping ................................................................................................. 19

3.3 DMA Operation........................................................................................................................... 20

3.3.1 Setting Memory Status ........................................................................................................ 20

3.3.2 Starting DMA Transfer......................................................................................................... 20

3.3.3 Endian Mode for DMA ......................................................................................................... 21

3.3.4 Byte Select Mode ................................................................................................................21

3.4 Controlling Peripherals ............................................................................................................... 23

3.5 DSP and RISC Cooperation....................................................................................................... 24

3.5.1 RISC Control DSP by Interrupt ........................................................................................... 24

3.5.2 Data exchange between the RISC and the DSP ................................................................ 26

3.6 Differences between the DSP and ADI’s ADSP2181................................................................. 27

3.6.1 Memory ............................................................................................................................... 27

3.6.2 Instructions .......................................................................................................................... 27

3.6.3 Biased-rounding mode ........................................................................................................ 27

3.6.4 Non-memory mapped registers........................................................................................... 27

3.6.5 Memory mapped registers................................................................................................... 27

3.6.6 Critical path limitation .......................................................................................................... 27

4Dynamic Memory Interface................................................................................................................29

4.1 Operation Overview.................................................................................................................... 29

4.2 Pin Sharing ................................................................................................................................. 30

4.3 Normal Operation ....................................................................................................................... 31

4.4 Wake-up Operation .................................................................................................................... 33

4.5 Clock Switching Operation ......................................................................................................... 34

4.6 Self-refresh Mode ....................................................................................................................... 35

5Static memory Interface.....................................................................................................................36

5.1 Operation Overview.................................................................................................................... 36

5.2 Instruction Access Mode ............................................................................................................ 36

5.3 Direct Access Mode.................................................................................................................... 38

5.4 DMA Access Mode ..................................................................................................................... 39

5.4.1 DMA read ............................................................................................................................ 39

5.4.2 DMA write............................................................................................................................ 40

6Clocks and Power Manager...............................................................................................................47

6.1 Operation Overview.................................................................................................................... 47

6.2 Change Clock Source................................................................................................................. 48

6.3 Change Clock Ratio.................................................................................................................... 49

6.3.1 Change the System and I/O Clock Ratio ............................................................................ 49

6.3.2 Change the External Memory Clock Ratio .......................................................................... 49

6.4 Change PLL Frequency.............................................................................................................. 51

6.5 Power Mode ............................................................................................................................... 52

**Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

Atlas™ Programming Guide **Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

- 2-

6.5.1 Normal Mode....................................................................................................................... 52

6.5.2 Turbo Mode ......................................................................................................................... 52

6.5.3 Idle Mode............................................................................................................................. 52

6.5.4 Standby Mode ..................................................................................................................... 53

6.5.5 Sleep Mode ......................................................................................................................... 53

7GPIO ..................................................................................................................................................55

7.1 Operation Overview.................................................................................................................... 55

7.2 Configure GPIO Pin Sharing ......................................................................................................56

7.3 Configure GPIO as Input ............................................................................................................ 57

7.4 Configure GPIO as Output ......................................................................................................... 58

7.5 Configure GPIO as Open-Drain ................................................................................................. 59

7.6 Configure GPIO as Wake-up Source ......................................................................................... 60

7.7 Configure GPIO to be Accessed by DSP................................................................................... 61

8Resource Sharing Controller .............................................................................................................62

8.1 Operation Overview.................................................................................................................... 62

8.2 DMA Channel Sharing................................................................................................................ 63

8.3 External Pin Multiplex................................................................................................................. 64

9DMA Controller ..................................................................................................................................66

9.1 Operation Overview.................................................................................................................... 66

9.2 Initialization................................................................................................................................. 67

9.3 DMA Interrupt Handling .............................................................................................................. 69

9.4 Single and Burst DMA ................................................................................................................ 70

9.5 1-D and 2-D DMA ....................................................................................................................... 71

9.6 Loop DMA................................................................................................................................... 73

9.7 DSP Control of DMA................................................................................................................... 76

10 PCMCIA Interface ..............................................................................................................................77

10.1 Operation Overview ................................................................................................................ 77

10.2 Pin-mux Programming ............................................................................................................ 78

10.3 M6730 Register Programming ................................................................................................ 79

10.4 Power Logic Register Programming ....................................................................................... 81

10.5 Memory Window Configuration............................................................................................... 82

10.6 I/O Window Configuration ....................................................................................................... 83

10.7 Timing Control......................................................................................................................... 84

10.8 Management Interrupt Operation............................................................................................ 84

10.9 Card Interrupt Operation ......................................................................................................... 86

10.10 Socket Initialization Sequence................................................................................................ 87

11 Extension port ....................................................................................................................................88

11.1 Operation Overview ................................................................................................................ 88

11.2 Pin-mux Programming ............................................................................................................ 89

11.3 Timing Register Programming ................................................................................................ 90

11.4 Fixed Latency Access ............................................................................................................. 91

11.5 Variable Latency Access.........................................................................................................92

11.6 DSP Access ............................................................................................................................ 93

12 Universal Serial Port ..........................................................................................................................94

12.1 Operation Overview ................................................................................................................ 94

12.2 USP Reset and Power up....................................................................................................... 95

12.3 USP Initialization..................................................................................................................... 96

12.3.1 USP Work Mode Initialization.............................................................................................. 96

12.3.2 Sample Code of USP Initialization ...................................................................................... 99

12.4 USP Transmitting Operation................................................................................................. 105

12.4.1 I/O Mode Transmit by Interrupt ......................................................................................... 105

12.4.2 I/O Mode Transmit by Polling FIFO Status ....................................................................... 105

12.4.3 DMA Transmitting Mode.................................................................................................... 105

12.5 USP Receiving Operation ..................................................................................................... 107

12.5.1 I/O Mode Receiving by Interrupt ....................................................................................... 107

**Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

Atlas™ Programming Guide **Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

- 3-

12.5.2 I/O Mode Receiving by Polling FIFO Status...................................................................... 107

12.5.3 DMA Recieving Mode........................................................................................................ 108

12.6 Interralation of Transmitting and Receiving .......................................................................... 109

12.6.1 Independent Operation for Transmitting and Receiving ................................................... 109

12.6.2 concurrent Operation for Transmitting and Receiving ...................................................... 109

12.6.3 Alternate Operation for Transmitting and Receiving ......................................................... 109

12.7 Pin I/O Mode Operations ...................................................................................................... 109

12.8 USP Reconfiguration ............................................................................................................ 111

12.9 SIB Initialization .................................................................................................................... 112

12.10 SIB Operations...................................................................................................................... 114

12.10.1 Register Writing ............................................................................................................. 114

12.10.2 Register Reading ........................................................................................................... 114

12.10.3 Audio Data Transfer....................................................................................................... 114

12.10.4 Telecom Data Transfer.................................................................................................. 115

13 Audio CODEC Interface...................................................................................................................116

13.1 Operation Overview ..............................................................................................................116

13.2 AudioCODEC Controller Initialization ................................................................................... 117

13.3 AC’97 CODEC Configuration................................................................................................ 118

13.4 I2S CODEC Configuration .................................................................................................... 122

14 Camera Interface .............................................................................................................................124

14.1 Operation Overview ..............................................................................................................124

14.2 Initialize Operations .............................................................................................................. 125

14.2.1 Initialize Camera Interface ................................................................................................ 125

14.2.2 Camera Interrupt Operation .............................................................................................. 125

14.3 DMA Operations ................................................................................................................... 127

14.3.1 Initialize DMA Interface ..................................................................................................... 127

14.3.2 DMA Interrupt Operation ................................................................................................... 127

14.3.3 DMA operation .................................................................................................................. 128

14.4 Sensor Operations ................................................................................................................ 129

14.4.1 Initialize Sensor Control Module ....................................................................................... 129

14.4.2 Sensor Clock Operation .................................................................................................... 129

14.4.3 Capture Image Operation.................................................................................................. 129

14.4.4 Slave Mode Operation....................................................................................................... 130

14.4.5 Pixel Data Shift Operation................................................................................................. 131

14.4.6 Inverse Control Operation ................................................................................................. 132

14.4.7 Sample Pixel Clock Operation .......................................................................................... 132

14.4.8 Master Mode Operation..................................................................................................... 133

14.5 I2C Master Operations.......................................................................................................... 135

14.5.1 Initialize Unit ...................................................................................................................... 135

14.5.2 Write n Bytes to External Device....................................................................................... 135

14.5.3 Read n Bytes from External Device .................................................................................. 136

14.6 I2C Slave Operations............................................................................................................137

14.6.1 Initialize Unit ...................................................................................................................... 137

14.6.2 Normal Operation .............................................................................................................. 137

14.7 Quick Reference ................................................................................................................... 138

15 USB 1.1 Device Interface ................................................................................................................139

15.1 Operation Overview ..............................................................................................................139

15.2 Initialization ........................................................................................................................... 141

15.3 Control Transfer .................................................................................................................... 143

15.4 I/O Operation ........................................................................................................................ 145

15.5 DMA Operation ..................................................................................................................... 147

15.6 Quick Reference ................................................................................................................... 149

16 Host Port Interface ...........................................................................................................................150

16.1 Operation Overview ..............................................................................................................150

16.2 Address Mapping .................................................................................................................. 151

**Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

Atlas™ Programming Guide **Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

- 4-

16.3 Initialization ........................................................................................................................... 152

16.4 I/O & DMA Operation ............................................................................................................ 155

16.5 Handshaking with Host ......................................................................................................... 157

17 Secure Disk (SD) / Multi-Media Card Interface (MMC) ...................................................................158

17.1 Operation Overview ..............................................................................................................158

17.2 Internal Regsiter Programming............................................................................................. 159

17.3 I/O Operation ........................................................................................................................ 160

17.4 DMA Operation ..................................................................................................................... 161

17.5 Initialization ........................................................................................................................... 162

17.6 No Data Command/Response Transaction.......................................................................... 163

17.7 Single Block Operation ......................................................................................................... 164

17.7.1 Single Block Write ............................................................................................................. 164

17.7.2 Single Block Read ............................................................................................................. 164

17.8 Multiple Block Operation....................................................................................................... 165

17.8.1 Multiple Block Write........................................................................................................... 165

17.8.2 Multiple Block Read........................................................................................................... 165

17.8.3 Multiple Block Write Using Number Blocks....................................................................... 166

17.8.4 Multiple Block Read Using number Blocks ....................................................................... 166

18 Nand Flash Memory Interface .........................................................................................................167

18.1 Operation Overview ..............................................................................................................167

18.2 Initialization ........................................................................................................................... 167

18.3 I/O Operation ........................................................................................................................ 167

18.3.1 IO Read ............................................................................................................................. 167

18.3.2 IO Write ............................................................................................................................. 168

18.4 DMA Operation ..................................................................................................................... 168

18.5 DMA read example ............................................................................................................... 169

18.6 DMA write example...............................................................................................................169

18.7 NAND Boot-loader ................................................................................................................170

18.7.1 ARM Init Process............................................................................................................... 171

18.7.2 Flash Controller’s global register init process ................................................................... 172

18.7.3 Read Device ID ................................................................................................................. 172

18.7.4 Search File “NK.BIN”......................................................................................................... 172

18.7.5 Read “NK.BIN” and Parse It.............................................................................................. 172

18.8 Special Notes........................................................................................................................ 173

19 LCD Controller Interface ..................................................................................................................174

19.1 Operation Overview ..............................................................................................................174

19.2 Initialization ........................................................................................................................... 174

19.3 DMA Operation ..................................................................................................................... 176

19.4 Configuration Comparison for Different Mode ...................................................................... 177

19.5 Palette ................................................................................................................................... 178

19.5.1 Color Palette...................................................................................................................... 178

19.5.2 Grey Palette of FRC Sequence......................................................................................... 178

19.6 Special Register Configuration ............................................................................................. 179

19.6.1 Pixel Clock Divider ............................................................................................................ 179

19.6.2 FIFO Request Watermark Control .................................................................................... 179

19.7 Power Sequence / Back Light Control for LCD Displays...................................................... 179

20 Revision History ...............................................................................................................................180

**Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

Atlas™ Programming Guide **Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

- 5-

List of Figures

Figure 1. Atlas™ Block Diagram .......................................................................................................... 9

Figure 2. DSP Byte Select Mode........................................................................................................ 22

Figure 3. Data Mapping in 8-bit External Data Bus............................................................................ 37

Figure 4. Data Mapping in 16-bit External Data Bus .......................................................................... 37

Figure 5. Static Memory Interface Simple WriteTiming...................................................................... 41

Figure 6. Static Memory Interface Fixed Sequence WriteTiming....................................................... 43

Figure 7. Static Memory Interface Fixed Sequence WriteTiming....................................................... 45

Figure 8. Atlas™ Pin Multiplex Diagram............................................................................................. 64

Figure 9. 2-D DMA.............................................................................................................................. 71

Figure 10. 2-D DMA Wrap Around (X-Length > Width)........................................................................ 72

Figure 11. Loop-mode DMA ................................................................................................................. 73

Figure 12. NAND Boot Flow Diagram................................................................................................. 171

**Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

Atlas™ Programming Guide **Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

- 6-

List of Tables

Table 1. Reference Documents .............................................................................................................. 8

Table 3. DSP memory address mapping.............................................................................................. 19

Table 4. DSP memory usage guide...................................................................................................... 20

Table 5. DSP peripheral registers address mapping ............................................................................ 23

Table 6. Staitic Memory Chip Select Mapping...................................................................................... 36

Table 7. Staitic Memory Chip Select Mapping...................................................................................... 39

Table 8. Atlas™ DMA Channel Multiplex.............................................................................................. 63

Table 9. Atlas™ Pin Multiplex ............................................................................................................... 64

Table 10. Pixel Shift Number vs DMA Register Setting .................................................................... 138

Table 11. USB Device Endpoint Configuration ................................................................................. 149

Table 12. Differences between Master and Slave Mode .................................................................. 178

Table 13. FRC Sequence Table Example......................................................................................... 178

**Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

Atlas™ Programming Guide **Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

- 7-

1 Introduction

This document detailed descriptions and examples of programming and developing using the Centrality

Communications’ Atlas™ Processor. It is intended for the use of Centrality customers, partners, and

other interested parties to gain a detailed understanding of Centrality’s technology and architecture for

design purposes. Detailed programming guide, flow chart, and sample code are contained in this

manual to provide the user with a solid background.

1.1 Documentation Conventions

•In some sections, the documentation is still being finalized. In this case, a “TBD” will be in its

place meaning“To Be Determined”.

•Important items to make note are in blue and bold: i.e. NOTE: when laying out the SDRAM

Traces …

•Register names will be in all capital letters with an underscore for spacing. Examples include:

INT_FIQ_PENDING

•Include common conventions and assumptions for MSB, LSB, high, low, enable, etc…

•In this document, we refer to the ARM922T core as either RISC, RISC core, or ARM core.

These all refer to same ARM922T core licensed from ARM®.

•Figure Labels are placed below the figure; wheras table labels are placed above the tables they

are referring to.

•When diagrams include memory addresses, these are with respect to a specific memory domain.

When a figure describes a memory address, it will either explicitly include the memory domain

(i.e. PCMCIA, NAND Flash, SD…) or it is safe to assume it belongs to the domain of the relevant

section.

•Binary Values: Often in the register definitions specific fields within a 32 bit register are assigned

values. These values are represented by the following notation: For example if a three bit field

has the value of “3”, then the representation would be 2’b011.

•Hexadecimal Values: There are two types of representation of hexadecimal values: such as

16’h55AA, or 0x55AA.

**Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

Atlas™ Programming Guide **Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

- 8-

1.2 Referenced Documents

The following documents can be obtained from Centrality Communications to enhance the supplement

of the Atlas™ Processor.

Table 1. Reference Documents

File Name Description

ARM922T.PDF ARM922T processor core technical reference manual.

BlueApp.PDF Mindtree Consulting Bluetooth Baseband Controller Application

Document

BlueArch.PDF Mindtree Consulting Bluetooth Baseband Controller Architechture

Document

BlueImp.PDF Mindtree Consulting Bluetooth Baseband Controller Implementation

Document

BlueVer.PDF Mindtree Consulting Bluetooth Baseband Controller Verification

Document

I2C-Bus

Specification.PDF

The I2C Bus Specification version 2.1

M6730 Design

Document.PDF

Virtual IP Group M6730 – PCI to PC Card Host Adaptor Block Level

Design Document

M6730 Users Guide.PDF Virtual IP Group M6730 PCI to PC Card Host Adapter User Guide

V9012S_PM User

Guide.PDF

Virtual IP Group V9012S_PM – USB Device Controller User Guide

Atlas_dev1.PDF Centrality Communications Atlas™ Processor layout schematics

reference

Developer’s Manual

Lite.PDF

Centrality Communications Atlas™ Processor Developer’s Manual

(Lite)

**Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

Atlas™ Programming Guide **Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

- 9-

1.3 Architectural Overview

Figure 1 is the block diagram for Atlas™.

Figure 1. Atlas™ Block Diagram

•RISC Core

Atlas™ has an integrated ARM922T core with the AMBA ASB bus. The RISC acts as a controller, which

controls the other functional blocks via writing/reading memory-mapped registers. The RISC accesses

external memory via the memory bus and acts as a bus master.

•DSP Core

Most of the computation required for the multimedia and communication applications can be performed

in the Digital Signal Processor (DSP). The advantages of using a DSP include an increase in the

computation horsepower, effectiveness, and reduced memory footprint and bandwidth. The DSP

operates independent from the RISC processor and contains its own program and data memory space.

The DSP is also a bus master and can DMA data to/from external memory via the memory bus.

However, the DSP is controlled by the RISC processor through a shared register file. The RISC

processor can write commands into the register file and start/stop DSP programs. The DSP can also

write to the register file and transfer data/status to the RISC. The RISC and DSP can symbiotically

interrupt each other.

Both the RISC and the DSP can read/write to memory-mapped control registers to configure or read the

status of a peripheral block. This accesses takes place on two distinct buses, the RISC I/O Bus (RBUS)

and DSP I/O Bus (DBUS). Each block has a Control Register Interface to decode the register

accesses from the RISC and DSP and resolve any potential conflict. (Note: The RISC and the DSP can

simultaneously read/write two separate registers, as long as they are not in the same functional block).

•System Memory Bus

The system memory bus is a 32-bit high-performance, low-power bus. In the Atlas™ architecture, there

are 4 bus masters: RISC, DSP, I/O Bridge, and LCD Controller. The Bus Arbitrator arbitrates requests

of the four bus masters and directs the appropriate accesses to the single system memory bus slave –

the Memory Controller.

•Memory Controller

ARM

922T

DSP

Subsystem

System Memory

Bus Arbiter

Memory

Controller

ROM Interface

LCD Controller

I/O Bridge

NAND Flash

Smart Media

USB 1.1

Interface

SD/MMC

Interface

PCMCIA/CF

Host/Slave_

Extension

Port

Camera

Interface

Serial Ports

GPS

Baseband

Bluetooth

Baseband

SDRAM/SRAM

Flash/ROM

LCD Panel

LCD Driver

GPIOs

Keyboard

Bluetooth RF GPS RF IrDA, UART

CODEC, Tch-Scrn

CMOS/CCD

Sensor

NAND Flash

Smartmedia

USB Host SD/MMC

Card

CF/PCMCIA

Host/Slave

Extension Chip

**Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

Atlas™ Programming Guide **Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

- 10 -

The Memory Controller controls all access to external memory. The Memory Controller supports SDRAM

as the main memory for program and data storage during the chip’s normal operational mode. During

boot, the RISC processor will first transfer the code stored in Flash memory to the program space in the

SDRAM. After boot-up, the Flash memory can be considered as a peripheral device.

•Peripheral Subsystem

Atlas™ is a multi-functional platform, so it contains several peripheral interface blocks:

1) 16 channel GPS baseband

2) Bluetooth baseband

3) USB device interface

4) NAND Flash/Smart Media interface

5) CMOS/CCD sensor interface

6) NOR Flash/ROM interface

7) Universal Serial Ports

8) Audio CODEC interface

9) SD/MMC interface

10) LCD interface

All of these interface blocks have the same functionality: they each provide a means to transfer data

between Atlas™ and an external device. There are two types of transfer: I/O read/write and DMA. Some

blocks only support I/O read/write, such as the Bluetooth and GPS blocks. Some blocks support both I/O

read/write and DMA, such as the serial port, CMOS sensor, NAND Flash/Smartmedia, Flash/ROM,

SD/MMC and USB interface. Each peripheral has its own SRAM FIFO. The I/O read/write can be

executed by either the RISC or DSP, via the RBUS or DBUS respectively. The DMA can be executed

via the I/O memory bus. The peripheral blocks with DMA channel will connect to the I/O Bridge via the

I/O memory bus.

The I/O Bridge is responsible for the arbitration of the DMA requests from the peripherals. But it can only

grant the I/O memory bus to the peripheral when it's granted the system memory bus from the Bus

Arbiter.

**Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

Atlas™ Programming Guide **Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

- 11 -

1.4 Key Features

Unlike other application processors on the market today, the Atlas™ processor provides the following

key features integrated on-chip.

240MHz ARM922T RISC core

o8KB I-Cache

o8KB D-Cache

oMemory Management Unit

oDebug Capability via JTAG port

120MHz DSP core for optimized low-power acceleration for: MP3, Image Video compression

and processing, GPS, VOIP, and MIDI

o2Kx24bit Program Memory

o3Kx16bit Data Memory

16 channel GPS baseband specific hardware

Bluetooth baseband specific hardware

CMOS/CCD sensor interface

NAND Flash support with integrated Bootloader

100MHz SDRAM bus with support for 2.5V Mobile SDRAM

Graphic LCD controller with UMA for Active TFT and monochrome LCD panels

Advanced power management features including dynamic Processor Voltage Scaling, fine-

grained clock-gating to dynamically turn off peripherals

USB 1.1 device

4 Universal serial ports

Multiple card support: PCMCIA, SmartMedia®, SD, MMC, Compact Flash, etc.

28 General-purpose I/O and 116 programmable I/O

291 pin TFBGA (16x16mm)1package

Low-power 0.18u CMOS

112x12mm package option available

**Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

Atlas™ Programming Guide **Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

- 12 -

2 RISC Subsystem

2.1 Operation Overview

The RISC Subsystem includes an ARM922T RISC core (with 8KB I-Cache and 8KB D-Cache) and a

RISC interface.

The RISC interface can translate the ARM922T bus cycles into Atlas™ internal system bus cycles.

There are two types of basic bus cycle of ARM922T: I/O cycle and Memory cycle. It’s decided by the

address to define if a RISC bus cycle is I/O or Memory cycle. The I/O cycle will be transferred to the

internal RISC I/O bus (RBUS). And the Memory cycle will be transferred to the internal system memory

bus (MBUS).

All buses mentioned above are in 32-bit.

2.2 RISC Address Mapping

The ARM922T has a 32-bit address bus, which will be translated by the RISC interface into either an

access to cacheable data memory, non-cacheable data memory, or memory-mapped registers. Bits

<26:0> of the address are used as the physical address bus.

All address mapping registers must be inside the RISC interface. The RISC interface will be responsible

for all address decoding before it issues the command cycles to the system. The boot ROM should have

instructions about how to initialize these address-mapped registers. The programmer needs to provide

the system with the initialization routine.

•ROM & PCMCIA

The address mapping is defined starting from CPU reset vector (0x0000-0000). There is 512MB set

aside for ROM. However, not all of this space can be used. For security reasons, this memory must be

mirrored. Thus, the maximum size that can be set for the ROM cannot exceed 256MB. Also, because

the mirrored memory is laid out onto two sequential 256MB segments, accessing 0x0000-0000 and

0x1000-0000 directly will yield the same result.

The memory space from 512MB to 1GB is allocated to two PCMCIA sockets. Each socket takes 256MB

of memory.

•DSP Shared Memory & Extension Port

The Extension port takes 128MB space starting from 1GB address. And the DSP shared memory takes

another 128MB based on Extension port.

If the RISC reads from the reserved address space, a data abort operation will result. Writes to the

reserved address space have no effects.

•Internal Registers

Every peripheral device occupies 64K-byte space starting from 2GB to 3GB.

•System Memory

The system memory is between 3GB and 4GB. The actual memory size is also defined in the boot ROM

or by the memory auto-sizing program.

The following table shows the memory address mapping of Atlas™.

**Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

Atlas™ Programming Guide **Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

- 13 -

Table 2. System Memory Mapping

Address Range Usage Resource Size

E800_0000~FFFF_FFFF Reserved 384MB

E000_0000~E7FF_FFFF Zero Bank 128MB

C000_0000~DFFF_FFFF System Memory 512MB

8000_0000~BFFF_FFFF Internal Registers 1GB

5000_0000~7FFF_FFFF Reserved 768MB

4800_0000~4FFF_FFFF DSP Shared Memory 128MB

4000_0000~47FF_FFFF Extension Port 128MB

3000_0000~3FFF_FFFF PCMCIA Socket 1 256MB

2000_0000~2FFF_FFFF PCMCIA Socket 0 256MB

0000_0000~1FFF_FFFF Flash/ROM 512MB

**Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

Atlas™ Programming Guide **Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

- 14 -

2.3 Boot-up Control

There is a RISCINT_BOOT_UP register that can be used by software to record the boot-up status. If the

chip is boot-up from power on, then after boot-up software should set the COLD_BOOT bit in this

register. Otherwise, the software should set the WARM_BOOT bit.

Based on the value of this register, software can decide how to handle the following boot-up procedure.

When boot-up from NOR-Flash or ROM, the boot program needs to do re-direct the NOR-Flash/ROM

access to the shadowed SDRAM memory space somewhere between the boot-up. This is also done by

setting the COLD_BOOT bit. To make sure the setting taking effect as soon as possible, user can write

the FIFO_FLUSH bit in RISCINT_FIFO_FLUSH register right after set this Boot-up register.

RISCINT_BOOT_UP = 0x1;

RISCINT_FIFO_FLUSH = 0x3;

After the COLD_BOOT bit is set, all CPU access to address 0~0x0FFF_FFFF will be re-directed to the

system memory space (0xC000_0000~0xCFFF_FFFF). But the CPU can still access the NOR-

Flash/ROM memory by issuing the address of it’s mirror image sitting on 0x1000_0000~0x1FFF_FFFF.

Due to the pipeline nature of the RISC core, after the Boot-up register been set, user CANNOT access

the ROM address space at once. It needs to insert at least one NOP between them.

**Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

Atlas™ Programming Guide **Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

- 15 -

2.4 Wait State Control

Most peripherals in Atlas™ are in I/O clock domain (please refer to the section 6 “Clocks and Power

Manager”), while the RISC Subsystem is running at a higher system clock domain. So there is need for

inserting wait states when the RISC read those slow I/O devices.

Besides, due to the parastic capacitance in the silicon, the data read from a block that is far from the

CPU will have longer dealy. Sometimes the delay might be longer than one system clock cycle. In this

case, there is also need for inserting wait states.

There are totally 8 groups of wait state register bits (WS0~7); each is used to control the wait states of

one group of I/O devices. The allocation is as following:

•WS0 – RISC Interface, Interrupt Controller, OS Timer

•WS1 – DSP Interface, GPS Baseband, SDRAM Controller

•WS2 – LCD Controller, Reset Controller, Real-time Clock Controller

•WS3 – Power Manager, Resource Sharing Controller

•WS4 – Bus Arbiter, DMA Controller, Flash/ROM Controller, Camera Interface

•WS5 – USP0, USP1, USP2, USP3, Audio CODEC Interface

•WS6 – GPIO, Extension Port, SD/MMC Interface, Host Port, PCMCIA Interface

•WS7 – Bluetooth Baseband

Among those groups, WS0~WS3 are used to insert wait states for the blocks in system clock domain.

While WS4~6 are used to insert wait states of the blocks in I/O clock domain. WS7 is used for only

Bluetooth Baseband because it’s the only asynchronous device of the whole chip.

Because each group of wait state register bits are shared among several devices (except for WS7),

those devices will always have the same wait states setting. That is to say, if user want to increase wait

states for one block, then the other blocks in the same group will all have more wait states.

**Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

Atlas™ Programming Guide **Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

- 16 -

2.5 Write Pulse Control

The wait states insertion can only solve the issues when RISC read slow devices. But if RISC is trying to

write the slow device, the write enable pulse has to be adjusted too. The write enable pulse width should

be exactly the same as the slow device’s clock period. Otherwise, the data might be written to the slow

device twice. This might be OK sometimes, but sometimes unkown result may occur.

The I/O clock domain can be programmed to run at ½ or ¼ of the clock frequency of the system (pleaser

refer to the section 6 “Clocks and Power Manager”). So there are two different configurations for the

write pulse width:

•When I/O clock is ½ of the system clock domain, the write enable pulse should be 2 system

clock cycles:

RISCINT_WIDTH = 0x10;

•When I/O clock is ¼ of the system clock domain, the write enable pulse should be 4 system

clock cycles:

RISCINT_WIDTH = 0x30;

**Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

Atlas™ Programming Guide **Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

- 17 -

2.6 Timeout Control

When RISC accesses I/O device and the device has no response in a certain period, the RISC interface

will be timeout and generate an interrupt.

This certain period can be programmed by settting a 16-bit number in RISCINT_TIMEOUT register. By

default his register is not used at all. But if user like, he can easily enable the Timeout check by setting

the TIMEOUT_EN bit (bit<31> of RISCINT_TIMEOUT register).

When Timeout check is enabled and the device response is longer than the Timeout value, the RISC

interface will generate an interrupt to the CPU in RISCINT_TIMEOUT_INT register.

**Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

Atlas™ Programming Guide **Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

- 18 -

3 DSP Subsystem

3.1 Operation Overview

The DSP used in Atlas™ processor acts as a acceleration computational parts for GPS, MP3, Image

processing etc. The DSP core is provided by Faraday Technology Corp. and is instruction compatible

with ADI’s ADSP2181 except for minor differences.

The DSP is an independent processor. It has it’s own program and data memory. The RISC core can

read/write data throught it’s IDMA port and can interrupt the DSP. The DSP can do data exchange

between it’s data or program memory and SDRAM by operating the DMA controller of DSP interface. It

can also control some of the peripherals such as DMA controller, serial port interface, interrupt controller,

GPIO and extension interface by accessing the peripherals’ registers.

**Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

Atlas™ Programming Guide **Preliminary and Confidential under NDA, DO NOT DISTRIBUTE

- 19 -

3.2 DSP Memory Address Mapping

The DSP core has three sets of buses to access three parts of memory named program memory, data

memory and program-data memory. For simplification, we call these three parts of memory PM, DMX

and DMY respectively. DMX is mapped to the DSP’s data memroy space, PM and DMY are mapped to

the DSP’s program memory space. Memory read/write instructions can only access DMY.

DMX and PM are further split to two parts, one part is accessed by DSP only (named DMX-in and PM-in

respectively), and another part can either be configured as accessed by DSP or accessed by DMA

controller (named DMX-swap and PM-swap respectively). This gives flexibility to change program or

move data when the DSP is running and is the compensation to small memory space. The DSP can

change memory settings by configure memory control registers and do DMA transfer by configure the

DMA control registers.

DMX-swap and PM-swap can be configured as single buffer or double buffer. When configured as

double buffer, the buffer is spitted into two parts: one part is accessed by the DSP and another part is

accessed by the DMA controller side. When configured as single buffer, the buffer is either accessed by

the DSP or accessed by the DMA controller.

NOTE: Though double buffer gives the flexibility of programming, it is hard to control it in

program because the DSP compiler does not support such features. And in most cases, it does

not significantly improve the performance. Use this feature with caution.

The total size of DMY is 4k WORD. 1k WORD is in DSP interface and can be accessed by the DSP or

the DMA controller, other 3k WORD is in GPS baseband module and can only be accessed by the DSP.

This 3k buffer can be used by DSP as normal data memory while GPS function is not activated. The

following table is the summary of the DSP memory spaces.

Table 3. DSP memory address mapping

Memory Starting Address Size(WORD) Word Length Accessed By

DMX-in 0x0000 (DM) 1024 16 DSP only

DMX-swap (single) 0x0400 (DM) 1024 16 DSP/SDRAM

DMX-swap (double) 0x0400 (DM) 512 16 DSP/SDRAM

DMY (DSP interface) 0x3c00 (PM) 1024 16 DSP/SDRAM

DMY (GPS baseband) 0x3000 (PM) 3072 16 DSP only

PM-in 0x0000 (PM) 1024 24 DSP only

PM-swap (single) 0x0400 (PM) 1024 24 DSP/SDRAM

PM-swap (double) 0x0400 (PM) 512 24 DSP/SDRAM

Table of contents

Popular Computer Hardware manuals by other brands

ADLINK Technology

ADLINK Technology arm AMPERE COM-HPC-ALT user guide

ZALMAN

ZALMAN CNPS9700 LED user manual

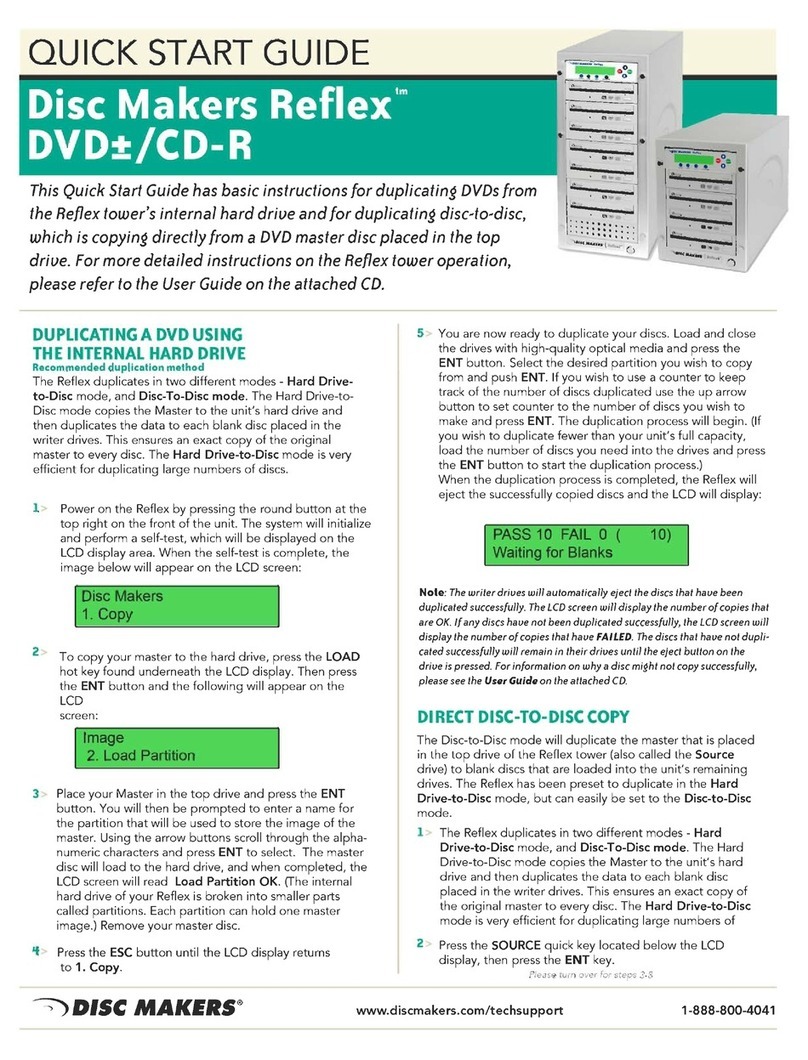

Disc Makers

Disc Makers Reflex4 quick start guide

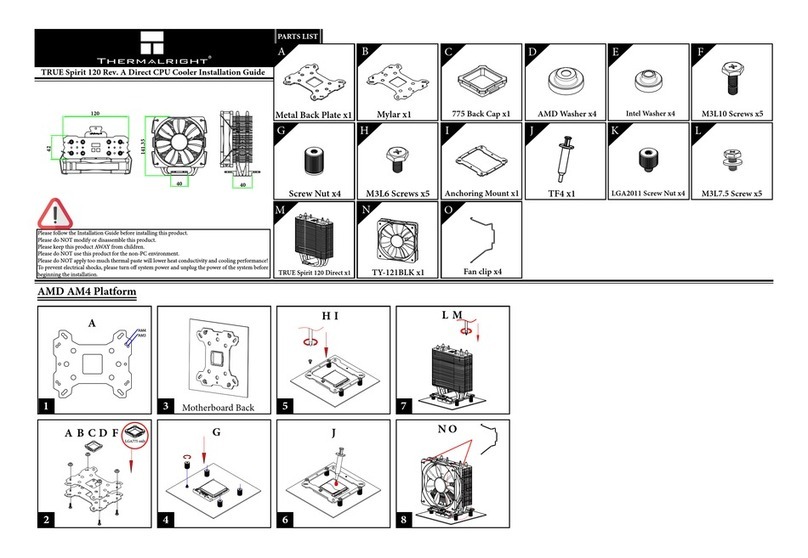

Thermalright

Thermalright TRUE Spirit 120 Direct installation guide

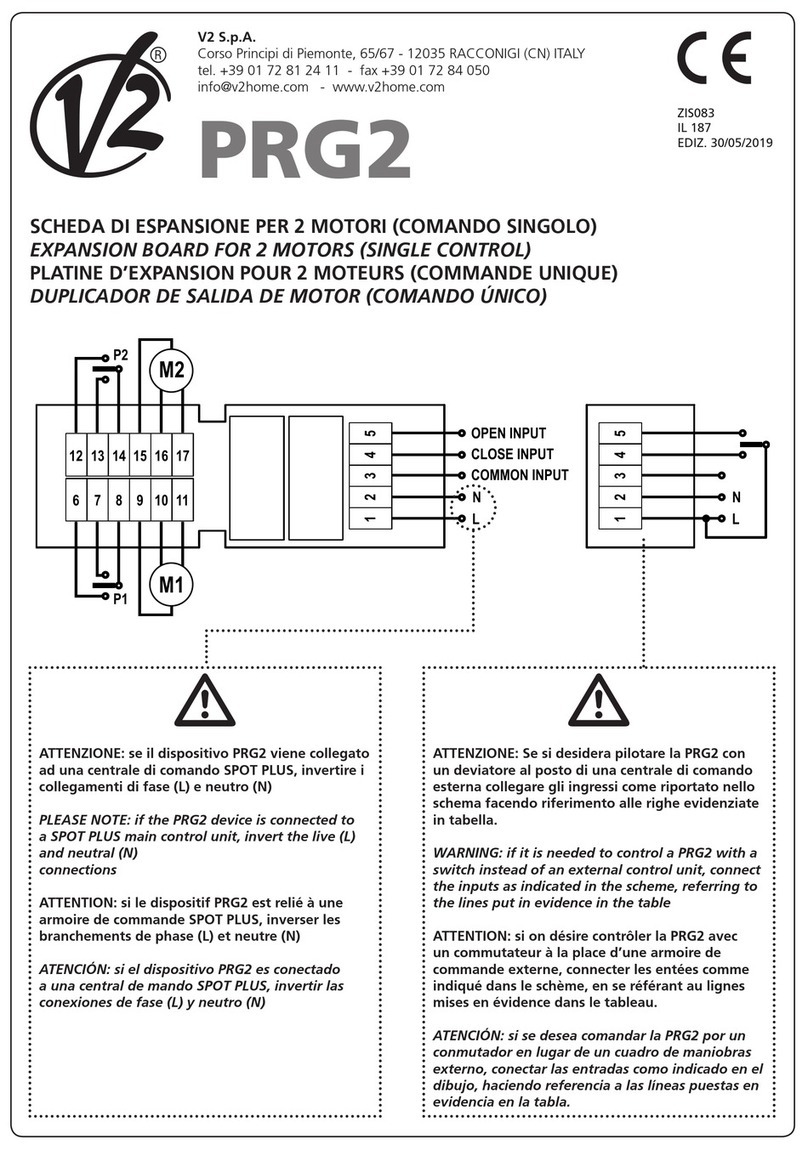

V2

V2 PRG2 instruction manual

Harman

Harman MADRIGAL AUDIO LABORATORIES MARK LEVINSON... owner's manual