AN83

2AN83REV3

TABLE OF CONTENTS

SCHEMATIC CHECKLIST ...................................................................................................................................4

SOFTWARE CHECKLIST ....................................................................................................................................5

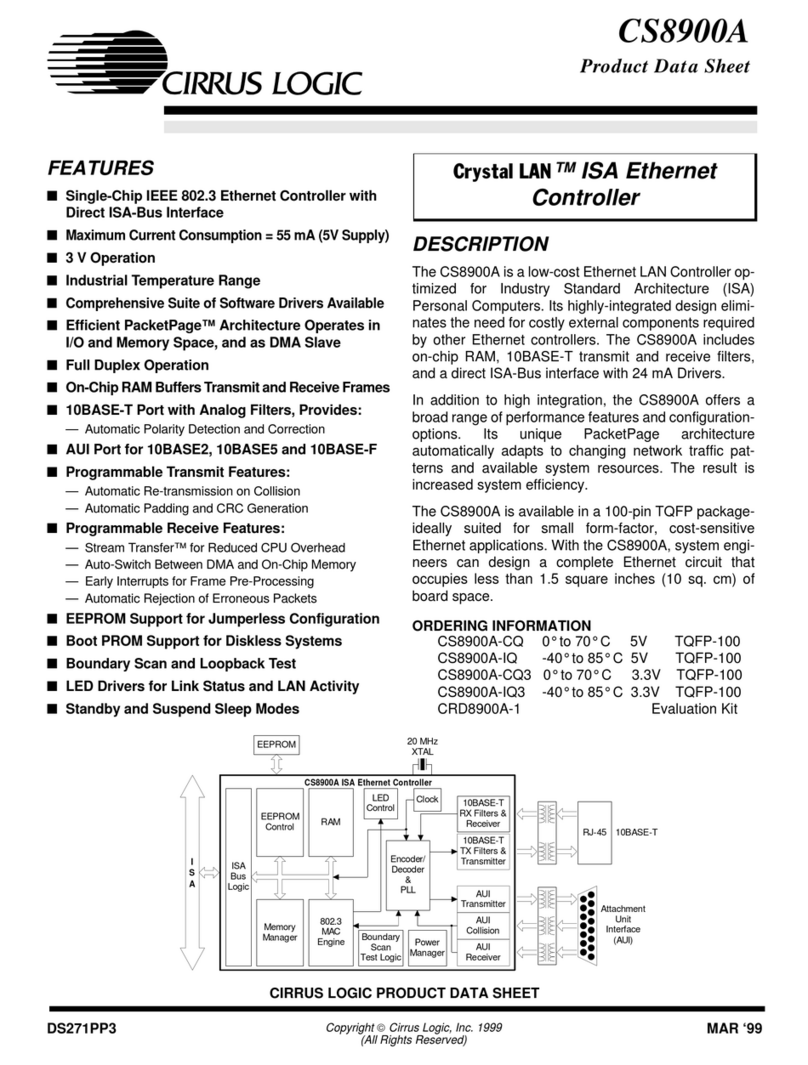

INTRODUCTION TO CS8900A TECHNICAL REFERENCE MANUAL ..............................................................6

HARDWARE DESIGN ..........................................................................................................................................7

CS8900A: CONNECTING TO NON-ISA BUS SYSTEMS ...................................................................................7

The CS8900A Architecture.............................................................................................................................7

ISA Bus ....................................................................................................................................................8

CS8900A in I/O Mode ..............................................................................................................................8

CS8900A in Memory Mode......................................................................................................................8

DMA Interface of the CS8900A................................................................................................................8

Selection of I/O, Memory and DMA Modes ....................................................................................................9

Design Example: CS8900A Interface to MC68302 ........................................................................................9

Address Generation .................................................................................................................................9

Read and Write Signals .........................................................................................................................10

SBHE Signal ..........................................................................................................................................10

Other Control Signals.............................................................................................................................10

Status Signals from CS8900A ...............................................................................................................11

Databus (SD[0:15]) Connection....................................................................................................................11

Checklist for Signal Connections to the CS8900A .......................................................................................11

EEPROM Optional........................................................................................................................................11

Design Example: CS8900A Interface to Cirrus Logic CL-PS7111 ...............................................................12

Design Example: CS8900A Interface to Hitachi SH3 ...................................................................................12

Summary ......................................................................................................................................................12

ETHERNET HARDWARE DESIGN FOR EMBEDDED SYSTEMS AND MOTHERBOARDS ..........................15

General Description ...............................................................................................................................15

Board Design Considerations ................................................................................................................15

Crystal Oscillator .............................................................................................................................15

ISA Bus Interface ............................................................................................................................15

External Decode Logic ....................................................................................................................15

EEPROM.........................................................................................................................................15

LEDs................................................................................................................................................18

10BASE-T Interface ........................................................................................................................18

10BASE-2 and AUI Interfaces.........................................................................................................18

Logic Schematics...................................................................................................................................18

Component Placement and Signal Routing ........................................................................................20

Bill of Material ........................................................................................................................................20

Contacting Cirrus Logic Support

For a complete listing of Direct Sales, Distributor, and Sales Representative contacts, visit the Cirrus Logic web site at:

http://www.cirrus.com/corporate/contacts/

Crystal LAN, StreamTransfer, PacketPage, and SMART Analog are trademarks of Cirrus Logic.

Ethernet is a registered trademark of Xerox Corp.. Artisoft and LANtastic are registered trademarks of Artisoft, Inc.. Banyan and VINES are registered trademarks

of Banyan Systems.. Digital and PATHWORKS are registered trademarks of Digital Equipment Corporation.. Intel is a registered trademark of Intel Corporation..

LAN Server and IBM are registered trademarks of International Business Machines Corp.. Microsoft, LAN Manager, Windows 95, Windows for Workgroups, and

Windows NT are registered trademarks of Microsoft.. Novell and Netware are registered trademarks of Novell, Inc..

SCO is a registered trademark of Santa

Cruz Organization, Inc

.. UNIX is a registered trademark of AT&T Technologies, Inc.

Preliminary product information describes products which are in production, but for which full characterization data is not yet available. Advance product infor-

mation describes products which are in development and subject to development changes. Cirrus Logic, Inc. has made best efforts to ensure that the information

contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided “AS IS” without warranty of

any kind (express or implied). No responsibility is assumed by Cirrus Logic, Inc. for the use of this information, nor for infringements of patents or other rights

of third parties. This document is the property of Cirrus Logic, Inc. and implies no license under patents, copyrights, trademarks, or trade secrets. No part of

this publication may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or

otherwise) without the prior written consent of Cirrus Logic, Inc. Items from any Cirrus Logic website or disk may be printed for use by the user. However, no

part of the printout or electronic files may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical,

photographic, or otherwise) without the prior written consent of Cirrus Logic, Inc.Furthermore, no part of this publication may be used as a basis for manufacture

or sale of any items without the prior written consent of Cirrus Logic, Inc. The names of products of Cirrus Logic, Inc. or other vendors and suppliers appearing

in this document may be trademarks or service marks of their respective owners which may be registered in some jurisdictions. A list of Cirrus Logic, Inc. trade-

marks and service marks can be found at http://www.cirrus.com.