Cirrus Logic CS44800 User manual

Copyright ©Cirrus Logic, Inc. 2006

(All Rights Reserved)

http://www.cirrus.com

8-Channel Digital Amplifier Controller

Features

> 100 dB Dynamic Range - System Level

< 0.03% THD+N @ 1 W - System Level

32 kHz to 192 kHz Sample Rates

InternalOscillatorCircuitSupports24.576 MHz

to 54 MHz Crystals

Integrated Sample Rate Converter (SRC)

– Eliminates Clock Jitter Effects

– Input Sample Rate Independent Operation

Power Supply Rejection Realtime Feedback

Spread Spectrum Modulation - Reduces EMI

PWM Popguard®for Single-Ended Mode

Eliminates AM Frequency Interference

Programmable Load Compensation Filters

Support for up to 40 kHz Audio Bandwidth

Digital Volume Control with Soft Ramp

– +24 to -127 dB in 0.25 dB Steps

Per Channel Programmable Peak Detect and

Limiter

SPI™ and I²C®Host Control Interfaces

Separate 2.5 V to 5.0 V Serial Port and Host

Control Port Supplies

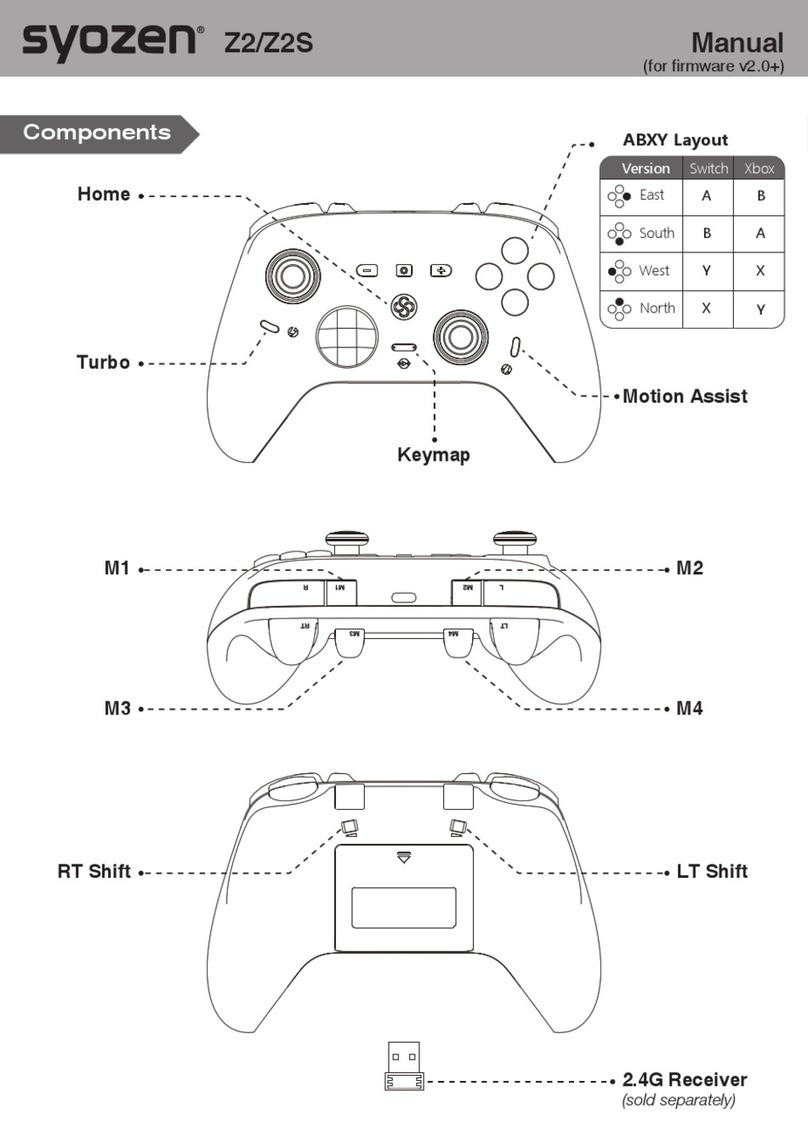

DAI

Serial

Port

XTAL

PWMOUTA1+

Power

Supply

Rejection

PWMOUTB1+

SPI/I2C Host

Control Port

SCL/CCLK

AD1/CDIN

AD0/CS

RST

INT

PSR_MCLK

PSR_SYNC

PSR_DATA

PWM

Backend

Control/

Status GPIO4

GPIO5

GPIO0

GPIO1

GPIO2

XTO

XTI

PWMOUTA1-

PWMOUTB1-

PWMOUTA2+

PWMOUTB2+

PWMOUTA2-

PWMOUTB2-

PWMOUTA3+

PWMOUTB3+

PWMOUTA3-

PWMOUTB3-

MUTE

PWMOUTA4+

PWMOUTB4+

PWMOUTA4-

PWMOUTB4-

DAI_MCLK

DAI_SCLK

DAI_LRCK

DAI_SDIN1

DAI_SDIN2

DAI_SDIN3

DAI_SDIN4

Volume

/ Limiter

Multibit

Σ∆

Modulator

PWM

Conversion

PWM

Conversion

PWM

Conversion

PWM

Conversion

Volume

/ Limiter

Multibit

Σ∆

Modulator

Volume

/ Limiter

Multibit

Σ∆

Modulator

Volume

/ Limiter

Multibit

Σ∆

Modulator

PWM

Clock

Control

Auto Fs

Detect

GPIO3

GPIO6

PSR_EN

PSR_RESET

PS_SYNC

SRC

SYS_CLK

SDA/CDOUT

MARCH '06

DS632F1

CS44800

2DS632F1

CS44800

General Description

The CS44800 is a multi-channel digital-to-PWM Class D audio system controller including interpolation, sample rate

conversion, half- and full-bridge PWM driver outputs, and power supply rejection feedback in a 64-pin LQFP pack-

age.The architecture uses a direct-to-digital approach that maintains digital signal integrity to the final output filter,

minimizing analog interference effects which negatively affect system performance.

The CS44800 integrates on-chip digital volume control, peak detect with limiter, de-emphasis, and 7 GPIO’s, allow-

ing easy interfacing to many commonly available power stages. The PWM amplifier can achieve greater than 90%

efficiency. This efficiency provides for smaller device package, less heat sink requirements, and smaller power

supplies.

The CS44800 is ideal for audio systems requiring wide dynamic range, negligible distortion and low noise, such as

A/V receivers, DVD receivers, digital speaker and automotive audio systems.

DS632F1 3

CS44800

TABLE OF CONTENTS

1. CHARACTERISTICS AND SPECIFICATIONS ...................................................................................... 8

SPECIFIED OPERATING CONDITIONS .............................................................................................. 8

ABSOLUTE MAXIMUM RATINGS ........................................................................................................ 8

DC ELECTRICAL CHARACTERISTICS ............................................................................................... 9

DIGITAL INTERFACE CHARACTERISTICS ........................................................................................ 9

PWM OUTPUT PERFORMANCE CHARACTERISTICS .................................................................... 10

PWM FILTER CHARACTERISTICS ................................................................................................... 11

SWITCHING CHARACTERISTICS - XTI ............................................................................................ 11

SWITCHING CHARACTERISTICS - SYS_CLK .................................................................................. 12

SWITCHING CHARACTERISTICS - PWMOUTA1-B4 ....................................................................... 12

SWITCHING CHARACTERISTICS - PS_SYNC ................................................................................. 12

SWITCHING CHARACTERISTICS - DAI INTERFACE ...................................................................... 13

SWITCHING CHARACTERISTICS - CONTROL PORT - I²C FORMAT ............................................. 14

SWITCHING CHARACTERISTICS - CONTROL PORT - SPI FORMAT ............................................ 15

2. PIN DESCRIPTIONS ........................................................................................................................... 16

2.1 I/O Pin Characteristics ................................................................................................................ 20

3. TYPICAL CONNECTION DIAGRAMS .....................................................................................21

4. APPLICATIONS ................................................................................................................................... 23

4.1 Overview ....................................................................................................................................... 23

4.2 Feature Set Summary ................................................................................................................... 23

4.3 Clock Generation ........................................................................................................................... 24

4.3.1 FsIn Domain Clocking .......................................................................................................... 25

4.3.2 FsOut Domain Clocking ........................................................................................................ 25

4.4 FsIn Clock Domain Modules ......................................................................................................... 27

4.4.1 Digital Audio Input Port ......................................................................................................... 27

4.4.2 Auto Rate Detect .................................................................................................................. 31

4.4.3 De-Emphasis ........................................................................................................................ 31

4.5 FsOut Clock Domain Modules ....................................................................................................... 32

4.5.1 Sample Rate Converter ........................................................................................................ 32

4.5.2 Load Compensation Filter .................................................................................................... 32

4.5.3 Digital Volume and Mute Control ..........................................................................................32

4.5.4 Peak Detect / Limiter ............................................................................................................ 33

4.5.5 PWM Engines ....................................................................................................................... 33

4.5.6 Interpolation Filter ................................................................................................................. 34

4.5.7 Quantizer .............................................................................................................................. 34

4.5.8 Modulator ............................................................................................................................. 34

4.5.9 PWM Outputs ....................................................................................................................... 34

4.5.10 Power Supply Rejection (PSR) Real-Time Feedback ........................................................ 35

4.6 Control Port Description and Timing ............................................................................................. 36

4.6.1 SPI Mode .............................................................................................................................. 36

4.6.2 I²C Mode ............................................................................................................................... 37

4.6.3 GPIOs ................................................................................................................................... 38

4.6.4 Host Interrupt ........................................................................................................................ 38

5. POWER SUPPLY, GROUNDING, AND PCB LAYOUT ....................................................................... 39

5.1 Reset and Power-Up ..................................................................................................................... 42

5.1.1 PWM PopGuard® Transient Control .................................................................................... 42

5.1.2 Recommended Power-Up Sequence ................................................................................... 42

5.1.3 Recommended PSR Calibration Sequence ........................................................................ 43

5.1.4 Recommended Power-Down Sequence .............................................................................. 44

6. REGISTER QUICK REFERENCE ........................................................................................................ 46

7. REGISTER DESCRIPTION .................................................................................................................. 50

7.1 Memory Address Pointer (MAP) .................................................................................................... 50

4DS632F1

CS44800

7.1.1 Increment (INCR) ................................................................................................................. 50

7.1.2 Memory Address Pointer (MAPx) ......................................................................................... 50

7.2 CS44800 I.D. and Revision Register (address 01h) (Read Only) ................................................. 50

7.2.1 Chip I.D. (Chip_IDx) ............................................................................................................. 50

7.2.2 Chip Revision (Rev_IDx) ...................................................................................................... 50

7.3 Clock Configuration and Power Control (address 02h) ................................................................. 51

7.3.1 Enable SYS_CLK Output (EN_SYS_CLK) ........................................................................... 51

7.3.2 SYS_CLK Clock Divider Settings (SYS_CLK_DIV[1:0]) ....................................................... 51

7.3.3 PWM Master Clock Divider Settings (PWM_MCLK_DIV[1:0]) ............................................. 51

7.3.4 Power Down XTAL (PDN_XTAL) ......................................................................................... 51

7.3.5 Power Down Output Mode (PDN_OUTPUT_MODE) ........................................................... 52

7.3.6 Power Down (PDN) .............................................................................................................. 52

7.4 PWM Channel Power Down Control (address 03h) ...................................................................... 52

7.4.1 Power Down PWM Channels (PDN_PWMB4:PDN_PWMA1) ............................................. 52

7.5 Misc. Configuration (address 04h) ................................................................................................ 53

7.5.1 Digital Interface Format (DIFX) ............................................................................................. 53

7.5.2 AM Frequency Hopping (AM_FREQ_HOP) ......................................................................... 53

7.5.3 Freeze Controls (FREEZE) .................................................................................................. 53

7.5.4 De-Emphasis Control (DEM[1:0]) ......................................................................................... 54

7.6 Ramp Configuration (address 05h) ............................................................................................... 54

7.6.1 Ramp-Up/Down Setting (RAMP[1:0]) .................................................................................. 54

7.6.2 Ramp Speed (RAMP_SPD[1:0]) .......................................................................................... 54

7.7 Volume Control Configuration (address 06h) ................................................................................ 55

7.7.1 Single Volume Control (SNGVOL) ....................................................................................... 55

7.7.2 Soft Ramp and Zero Cross Control (SZC[1:0]) ..................................................................... 55

7.7.3 Enable 50% Duty Cycle for Mute Condition (MUTE_50/50) ................................................. 55

7.7.4 Soft Ramp-Down on Interface Error (SRD_ERR) ................................................................ 56

7.7.5 Soft Ramp-Up on Recovered Interface Error (SRU_ERR) ................................................... 56

7.7.6 Auto-Mute (AMUTE) ............................................................................................................. 56

7.8 Master Volume Control - Integer (address 07h) ............................................................................ 57

7.8.1 Master Volume Control - Integer (MSTR_IVOL[7:0]) ............................................................ 57

7.9 Master Volume Control - Fraction (address 08h) .......................................................................... 57

7.9.1 Master Volume Control - Fraction (MSTR_FVOL[1:0]) ......................................................... 57

7.10 Channel XX Volume Control - Integer (addresses 09h - 10h) ..................................................... 59

7.10.1 Channel Volume Control - Integer (CHXx_IVOL[7:0]) ........................................................ 59

7.11 Channel XX Volume Control1 - Fraction (address 11h) ............................................................ 59

7.12 Channel XX Volume Control2 - Fraction (address 12h) .............................................................. 59

7.12.1 Channel Volume Control - Fraction (CHXX_FVOL[1:0]) .................................................... 59

7.13 Channel Mute (address 13h) ....................................................................................................... 60

7.13.1 Independent Channel Mute (CHXX_MUTE) ....................................................................... 60

7.14 Channel Invert (address 14h) ...................................................................................................... 60

7.14.1 Invert Signal Polarity (CHXX_INV) ..................................................................................... 60

7.15 Peak Limiter Control Register (address 15h) ............................................................................. 61

7.15.1 Peak Signal Limit All Channels (LIMIT_ALL) ...................................................................... 61

7.15.2 Peak Signal Limiter Enable (LIMIT_EN) ............................................................................. 61

7.16 Limiter Attack Rate (address 16h) .............................................................................................. 61

7.16.1 Attack Rate (ARATE[7:0]) .................................................................................................. 61

7.17 Limiter Release Rate (address 17h) ......................................................................................... 62

7.17.1 Release Rate (RRATE[7:0]) ...............................................................................................62

7.18 Chnl XX Load Compensation Filter - Coarse Adjust

(addresses 18h, 1Ah, 1Ch, 1Eh, 20h, 22h, 24h, 26h) ........................................................................ 62

7.18.1 Channel Compensation Filter - Coarse Adjust (CHXX_CORS[5:0]) .................................. 62

7.19 Chnl XX Load Compensation Filter - Fine Adjust

(addresses 19h, 1Bh, 1Dh, 1Fh, 21h, 23h, 25h, 27h) ......................................................................... 63

DS632F1 5

CS44800

7.19.1 Channel Compensation Filter - Fine Adjust (CHXX_FINE[5:0]) ......................................... 63

7.20 Interrupt Mode Control (address 28h) ......................................................................................... 63

7.20.1 Interrupt Pin Control (INT1/INT0) .......................................................................................63

7.20.2 Overflow Level/Edge Select (OVFL_L/E) ........................................................................... 64

7.21 Interrupt Mask (address 29h) ...................................................................................................... 64

7.22 Interrupt Status (address 2Ah) (Read Only) ...............................................................................64

7.22.1 SRC Unlock Interrupt (SRC_UNLOCK) .............................................................................. 64

7.22.2 SRC Lock Interrupt (SRC_LOCK) ...................................................................................... 65

7.22.3 Ramp-Up Complete Interrupt (RMPUP_DONE) ................................................................. 65

7.22.4 Ramp-Down Complete Interrupt (RMPDN_DONE) ............................................................ 65

7.22.5 Mute Complete Interrupt (Mute_DONE) ............................................................................. 65

7.22.6 Channel Over Flow Interrupt (OVFL_INT) .......................................................................... 65

7.22.7 GPIO Interrupt Condition (GPIO_INT) ................................................................................ 65

7.23 Channel Over Flow Status (address 2Bh) (Read Only) .............................................................. 66

7.23.1 ChXX_OVFL ....................................................................................................................... 66

7.24 GPIO Pin In/Out (address 2Ch) ................................................................................................... 66

7.24.1 GPIO In/Out Selection (GPIOX_I/O) .................................................................................. 66

7.25 GPIO Pin Polarity/Type (address 2Dh) ....................................................................................... 66

7.25.1 GPIO Polarity/Type Selection (GPIOX_P/T) ...................................................................... 66

7.26 GPIO Pin Level/Edge Trigger (address 2Eh) .............................................................................. 67

7.26.1 GPIO Level/Edge Input Sensitive (GPIOX_L/E) ................................................................. 67

7.27 GPIO Status Register (address 2Fh) .......................................................................................... 67

7.27.1 GPIO Pin Status (GPIOX_STATUS) .................................................................................. 67

7.28 GPIO Interrupt Mask Register (address 30h) .............................................................................. 68

7.28.1 GPIO Pin Interrupt Mask (M_GPIOX) ................................................................................. 68

7.29 PWM Configuration Register (address 31h) ............................................................................... 68

7.29.1 Over Sample Rate Selection (OSRATE) ............................................................................ 68

7.29.2 Channels A1 and B1 Output Configuration (A1/B1_OUT_CNFG) ..................................... 68

7.29.3 Channels A2 and B2 Output Configuration (A2/B2_OUT_CNFG) ..................................... 68

7.29.4 Channel A3 Output Configuration (A3_OUT_CNFG) ......................................................... 69

7.29.5 Channel B3 Output Configuration (B3_OUT_CNFG) ......................................................... 69

7.29.6 Channels A4 and B4 Output Configuration (A4/B4_OUT_CNFG) ..................................... 69

7.30 PWM Minimum Pulse Width Register (address 32h) ................................................................. 69

7.30.1 Disable PWMOUTXX - Signal (DISABLE_PWMOUTXX-) ................................................. 69

7.30.2 Minimum PWM Output Pulse Settings (MIN_PULSE[4:0]) ................................................. 70

7.31 PWMOUT Delay Register (address 33h) ................................................................................... 70

7.31.1 Differential Signal Delay (DIFF_DLY[2:0]) .......................................................................... 70

7.31.2 Channel Delay Settings (CHNL_DLY[4:0]) ........................................................................ 70

7.32 PSR and Power Supply Configuration (address 34h) ................................................................. 73

7.32.1 Power Supply Rejection Enable (PSR_EN) ....................................................................... 73

7.32.2 Power Supply Rejection Reset (PSR_RESET) .................................................................. 74

7.32.3 Power Supply Rejection Feedback Enable (FEEDBACK_EN) ........................................... 74

7.32.4 Power Supply Sync Clock Divider Settings (PS_SYNC_DIV[2:0]) ..................................... 74

7.33 Decimator Shift/Scale (addresses 35h, 36h, 37h) ....................................................................... 74

7.33.1 Decimator Shift (DEC_SHIFT[2:0]) ..................................................................................... 74

7.33.2 Decimator Scale (DEC_SCALE[18:0]) ............................................................................... 75

7.34 Decimator Outd (addresses 3Bh, 3Ch, 3Dh) ............................................................................... 75

7.34.1 Decimator Outd (DEC_OUTD[23:0]) .................................................................................. 75

8. PARAMETER DEFINITIONS ................................................................................................................ 76

9. REFERENCES ...................................................................................................................................... 77

10. PACKAGE DIMENSIONS ......................................................................................................... 78

11. THERMAL CHARACTERISTICS ....................................................................................................... 79

12. ORDERING INFORMATION .............................................................................................................. 79

13. REVISION HISTORY .......................................................................................................................... 79

6DS632F1

CS44800

LIST OF FIGURES

Figure 1.Performance Characteristics Evaluation Active Filter Circuit ...................................................... 10

Figure 2.XTI Timings ................................................................................................................................. 11

Figure 3.SYS_CLK Timings ...................................................................................................................... 12

Figure 4.PWMOUTxx Timings .................................................................................................................. 12

Figure 5.PS_SYNC Timings ...................................................................................................................... 12

Figure 6.Serial Audio Interface Timing ...................................................................................................... 13

Figure 7.Serial Audio Interface Timing - TDM Mode ................................................................................. 13

Figure 8.Control Port Timing - I²C Format ................................................................................................. 14

Figure 9.Control Port Timing - SPI Format ................................................................................................ 15

Figure 10.CS44800 Pinout Diagram ......................................................................................................... 16

Figure 11.Typical Full-Bridge Connection Diagram .................................................................................. 21

Figure 12.Typical Half-Bridge Connection Diagram .................................................................................. 22

Figure 13.CS44800 Data Flow Diagram (Single Channel Shown) ........................................................... 24

Figure 14.Fundamental Mode Crystal Configuration ................................................................................ 25

Figure 15.3rd Overtone Crystal Configuration .......................................................................................... 26

Figure 16.CS44800 Internal Clock Generation ......................................................................................... 26

Figure 17.I²S Serial Audio Formats ........................................................................................................... 28

Figure 18.Left-Justified Serial Audio Formats ........................................................................................... 28

Figure 19.Right-Justified Serial Audio Formats ......................................................................................... 29

Figure 20.One Line Mode #1 Serial Audio Format .................................................................................... 29

Figure 21.One Line Mode #2 Serial Audio Format .................................................................................... 30

Figure 22.TDM Mode Serial Audio Format ............................................................................................... 30

Figure 23.De-Emphasis Curve .................................................................................................................. 31

Figure 24.Control Port Timing in SPI Mode .............................................................................................. 36

Figure 25.Control Port Timing, I²C Slave Mode Write ............................................................................... 37

Figure 26.Control Port Timing, I²C Slave Mode Read ............................................................................... 37

Figure 27.Recommended CS44800 Power Supply Decoupling Layout .................................................... 39

Figure 28.Recommended CS44800 Crystal Circuit Layout ...................................................................... 40

Figure 29.Recommended PSR Circuit Layout .......................................................................................... 41

Figure 30.PSR Calibration Sequence ....................................................................................................... 44

Figure 31.PWM Output Delay ................................................................................................................... 72

Figure 32.64-Pin LQFP Package Drawing ................................................................................................ 78

DS632F1 7

CS44800

LIST OF TABLES

Table 1. Common DAI_MCLK Frequencies .............................................................................................. 25

Table 2. DAI Serial Audio Port Channel Allocations ................................................................................. 27

Table 3. Load Compensation Example Settings ....................................................................................... 32

Table 4. Typical PWM Switch Rate Settings ............................................................................................. 34

Table 5. Digital Audio Interface Formats ................................................................................................... 53

Table 6. Master Integer Volume Settings .................................................................................................. 57

Table 7. Master Fractional Volume Settings ............................................................................................. 58

Table 8. Channel Integer Volume Settings ............................................................................................... 59

Table 9. Channel Fractional Volume Settings ........................................................................................... 60

Table 10. Limiter Attack Rate Settings ...................................................................................................... 62

Table 11. Limiter Release Rate Settings ................................................................................................... 62

Table 12. Channel Load Compensation Filter Coarse Adjust ................................................................... 63

Table 13. Channel Load Compensation Filter Fine Adjust ........................................................................ 63

Table 14. PWM Minimum Pulse Width Settings ........................................................................................ 70

Table 15. Differential Signal Delay Settings .............................................................................................. 70

Table 16. Channel Delay Settings ............................................................................................................. 71

Table 17. Power Supply Sync Clock Divider Settings ............................................................................... 74

Table 18. Decimator Shift/Scale Coefficient Calculation Examples .......................................................... 75

8DS632F1

CS44800

1. CHARACTERISTICS AND SPECIFICATIONS

(All Min/Max characteristics and specifications are guaranteed over the Specified Operating Conditions. Typical

performance characteristics and specifications are derived from measurements taken at nominal supply voltages

and TA= 25°C.)

SPECIFIED OPERATING CONDITIONS

(GND = 0 V, all voltages with respect to ground)

Notes:

1. When using external crystal, VDX = 3.14 V(min). When using clock signal input, VDX = 2.37 V(min).

ABSOLUTE MAXIMUM RATINGS

(GND = 0 V; all voltages with respect to ground.)

WARNING:Operation at or beyond these limits may result in permanent damage to the device. Normal operation

is not guaranteed at these extremes.

2. Any pin except supplies. Transient currents of up to ±100 mA on the input pins will not cause SCR latch-up.

3. The maximum over/under voltage is limited by the input current.

Parameter Symbol Min Typ Max Units

DC Power Supply

Digital 2.5 V VD 2.37 2.5 2.63 V

XTAL (Note 1) 2.5 V

3.3 V

5.0 V

VDX 2.37

3.14

4.75

2.5

3.3

5.0

2.63

3.47

5.25

V

V

V

PWM Interface 3.3 V

5.0 V VDP 3.14

4.75 3.3

5.0 3.47

5.25 V

V

Serial Audio Interface 2.5 V

3.3 V

5.0 V

VLS 2.37

3.14

4.75

2.5

3.3

5.0

2.63

3.47

5.25

V

V

V

Control Interface 2.5 V

3.3 V

5.0 V

VLC 2.37

3.14

4.75

2.5

3.3

5.0

2.63

3.47

5.25

V

V

V

Ambient Operating Temperature

Commercial -CQZ

Automotive -DQZ TA-10

-40 -

-+70

+85 °C

°C

Parameters Symbol Min Max Units

DC Power Supply Digital

XTAL

PWM Interface

Serial Audio Interface

Control Interface

VD

VDX

VDP

VLS

VLC

-0.3

-0.3

-0.3

-0.3

-0.3

3.5

6.0

6.0

6.0

6.0

V

V

V

V

V

Input Current (Note 2) Iin -±10mA

Digital Input Voltage PWM Interface

(Note 3) Serial Audio Interface

Control Interface

VIND-PWM

VIND-S

VIND-C

-0.3

-0.3

-0.3

VDP+0.4

VLS+0.4

VLC+0.4

V

V

V

Ambient Operating Temperature -CQ

(power applied) -DQ TA-20

-50 +85

+95 °C

°C

Storage Temperature Tstg -65 +150 °C

DS632F1 9

CS44800

DC ELECTRICAL CHARACTERISTICS

(GND = 0 V, all voltages with respect to ground; DAI_MCLK = 12.288 MHz, XTAL = 24.576 MHz, PWM Switch

Rate = 384 kHz unless otherwise specified.)

4. Normal operation is defined as RST = HI with a 997 Hz, 0 dBFS input.

5. Current consumption increases with increasing XTAL clock rates and PWM switch rates. Variance be-

tween DAI clock rates is negligible.

6. ILC measured with no external loading on the SDA pin.

7. Valid with PSRR function enabled and the recommended external ADC (CS4461) and filtering.

8. Power down mode is defined as RST pin = LOW with all clock and data lines held static.

9. When RST pin = LOW, the internal oscillator is active to provide a valid clock for the SYS_CLK output.

DIGITAL INTERFACE CHARACTERISTICS

(GND = 0 V, all voltages with respect to ground)

10. Serial Port signals include: SYS_CLK, DAI_MCLK, DAI_SCLK, DAI_LRCK, DAI_SDIN1-4

Control Port signals include: SCL/CCLK, SDA/CDOUT, AD0/CS, AD1/CDIN, INT, RST, MUTE

PWM signals include: PWMOUTA1-B4, PSR_MCLK, PSR_SYNC, PSR_DATA, PS_SYNC, GPIO[6:0]

Parameter Symbol Min Typ Max Units

Normal Operation (Note 4)

Power Supply Current (Note 5) VD = 2.5 V

VDX = 3.3 V

VDP = 3.3 V

VLS = 3.3 V

VLC = 3.3 V (Note 6)

ID

IDX

IDP

ILS

ILC

-

-

-

-

-

150

2

1.2

150

250

-

-

-

-

-

mA

mA

mA

µA

µA

Power Dissipation VD=2.5 V, VDX = VDP = VLS = VLC = 3.3 V - 387 500 mW

Power Supply Rejection Ratio (Note 7) (1 kHz)

(60 Hz) PSRR -

-15

40 -

-dB

dB

Power-Down Mode (Note 8)

Power Supply Current All Supplies except VDX (Note 9) Ipd -80-µA

Parameters (Note 10) Symbol Min Typ Max Units

High-Level Input Voltage XTAL

PWM Interface

Serial Audio Interface

Control Interface

VIH

0.7xVDX

0.7xVDP

0.7xVLS

0.7xVLC

-

-

-

-

-

-

-

-

V

V

V

V

Low-Level Input Voltage XTAL

PWM Interface

Serial Audio Interface

Control Interface

VIL

-

-

-

-

-

-

-

-

0.2xVDX

0.2xVDP

0.2xVLS

0.2xVLC

V

V

V

V

High-Level Output Voltage at Io= -2 mA PWM Interface

Serial Audio Interface

Control Interface VOH

VDP-1.0

VLS-1.0

VLC-1.0

-

-

-

-

-

-

V

V

V

Low-Level Output Voltage at Io= 2 mA PWM Interface

Serial Audio Interface

Control Interface VOL

-

-

-

-

-

-

0.45

0.45

0.45

V

V

V

Input Leakage Current Iin --±10µA

Input Capacitance - - 8 pF

10 DS632F1

CS44800

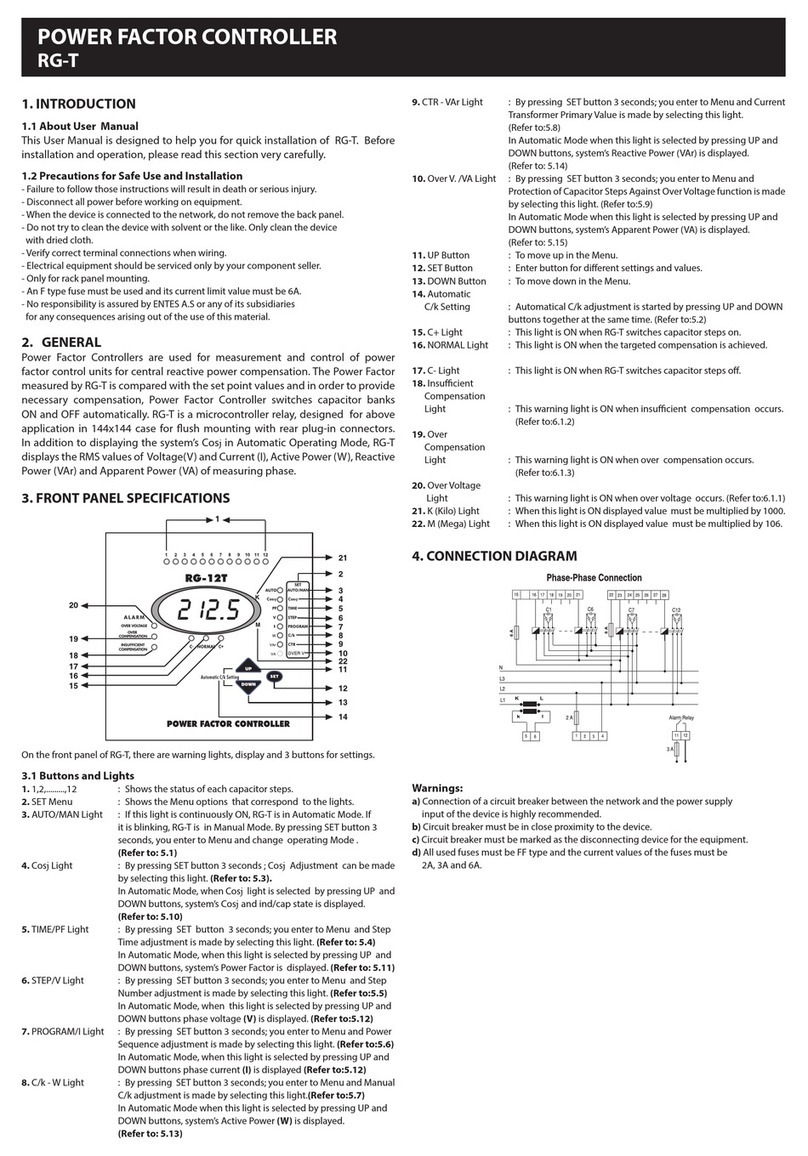

PWM OUTPUT PERFORMANCE CHARACTERISTICS

(Logic “0” = GND = 0 V; Logic “1” = VLS = VLC; VD = 2.5 V; DAI_MCLK = 12.288 MHz; XTAL= 24.576 MHz; PWM

Switch Rate = 384 kHz; Fs = 32 kHz to 192 kHz; Measurement bandwidth is 10 Hz to 20 kHz unless otherwise

specified; Performance measurements taken with a full-scale 997 Hz.)

11. Performance characteristics measured using filter shown in Figure 1.

Parameter Symbol Min Typ Max Unit

Dynamic Performance (Note 11)

24-Bits A-Weighted

unweighted

16-Bits unweighted

102

99

-

108

105

96

-

-

-

dB

dB

dB

Total Harmonic Distortion + Noise (Note 11)

24-Bits 0 dB

-20 dB

-60 dB

THD+N -

-

-

-90

-77

-45

-85

-

-

dB

dB

dB

Idle Channel Noise / Signal-to-Noise Ratio - 110 - dB

Interchannel Isolation (1 kHz) - 100 - dB

-

+

-

+

PWMOUTxx+

PWMOUTxx-

-

+-

+

Analog

Output

Figure 1. Performance Characteristics Evaluation Active Filter Circuit

DS632F1 11

CS44800

PWM FILTER CHARACTERISTICS

(Logic “0” = GND = 0 V; Logic “1” = VLS = VLC; VD = 2.5 V; DAI_MCLK = 12.288 MHz; XTAL = 24.576 MHz; PWM

Switch Rate = 384 kHz; Fs = 32 kHz to 192 kHz; Measurement bandwidth is 10 Hz to 20 kHz unless otherwise

specified.)

12. Filter response is not production tested but is characterized and guaranteed by design.

13. XTAL = 49.152 MHz; PWM Switch Rate = 768 kHz; Fs = 96 kHz to 192 kHz.

14. The equation for the group delay through the sample rate converter with OSRATE = 0b is (8.5 / Fsi) + (10

/ Fso) ± (4.5 / Fsi). The equation for the group delay through the sample rate converter with OSRATE = 1b

is (8.5 / Fsi) + (20 / Fso) ± (4.5 / Fsi).

SWITCHING CHARACTERISTICS - XTI

(VD = 2.5 V, VDP = VLC = VLS = 3.3 V, VDX = 2.5 V to 5.0 V; Inputs: Logic 0 = GND, Logic 1 = VDX)

Parameter UnitMin Typ Max

Digital Filter Response (Note 12)

Passband

OSRATE = 0b to -0.01 dB corner

to -3 dB corner

OSRATE = 1b (Note 13) to -0.01 dB corner

to -3 dB corner

0

0

0

0

-

-

-

-

1.6

24.0

3.3

44.5

kHz

kHz

kHz

kHz

Frequency Response

OSRATE = 0b 10 Hz to 20 kHz

OSRATE = 1b (Note 13) 10 Hz to 40 kHz -0.8

-1.2 -

-+0.02

+0.02 dB

dB

Group Delay (Note 14) ms

De-emphasis Error Fs = 32 kHz

(Relative to 1 kHz) Fs = 44.1 kHz

Fs = 48 kHz

-

-

-

-

-

-

±0.23

±0.14

±0.09

dB

dB

dB

Parameter Symbol Min Typ Max Unit

XTI period tclki 18.518 --- 40.69 ns

XTI high time tclkih 8.34 --- 22.38 ns

XTI low time tclkil 8.34 --- 22.38 ns

XTI Duty Cycle 45 50 55 %

External Crystal operating frequency 24.576 --- 54 MHz

XTI tclkih tclkil

tclki

Figure 2. XTI Timings

12 DS632F1

CS44800

SWITCHING CHARACTERISTICS - SYS_CLK

(VD = 2.5 V, VDP = VLC = VDX = 3.3 V, VLS = 2.5 V to 5.0 V, Cload = 50 pF)

SWITCHING CHARACTERISTICS - PWMOUTA1-B4

(VD = 2.5 V, VLS = VLC = VDX = 3.3 V, VDP = 3.3 V to 5.0 V unless otherwise specified, Cload = 10 pF)

SWITCHING CHARACTERISTICS - PS_SYNC

(VD = 2.5 V, VLS = VLC = VDX = 3.3 V, VDP = 3.3 V to 5.0 V, Cload = 20 pF)

Parameter Symbol Min Typ Max Unit

SYS_CLK Period tsclki 18.518 --- --- ns

SYS_CLK Duty Cycle 45 50 55 %

Parameter Symbol Min Typ Max Unit

PWMOUTxx Period tpwm 2.60 - 1.18 µs

Rise Time of PWMOUTxx VDP = 5.0 V

VDP = 3.3 V tr-

-1.6

2.1 -

-ns

ns

Fall Time of PWMOUTxx VDP = 5.0 V

VDP = 3.3 V tf-

-1.1

1.4 -

-ns

ns

Parameter Symbol Min Typ Max Unit

PS_SYNC Period tpsclki 592.576 --- --- ns

PS_SYNC Duty Cycle 45 50 55 %

SYS_CLK

tsclki

Figure 3. SYS_CLK Timings

PWMOUTxx

tpwm

trtf

Figure 4. PWMOUTxx Timings

PS_SYNC

tpsclki

Figure 5. PS_SYNC Timings

DS632F1 13

CS44800

SWITCHING CHARACTERISTICS - DAI INTERFACE

(VD = 2.5 V, VDX = VDP = VLC = 3.3 V, VLS = 2.5 V to 5.0 V; Inputs: Logic 0 = GND, Logic 1 = VLS.)

15. After powering up, the CS44800, RST should be held low until after the power supplies and clocks are set-

tled.

16. See Table 1 on page 26 for suggested MCLK frequencies.

17. Max DAI sample rate is 96 kHz for One Line and TDM modes of operation.

Parameters Symbol Min Max Units

RST pin Low Pulse Width (Note 15) 1-ms

DAI_MCLK Duty Cycle (Note 16) 40 60 %

DAI_SCLK Duty Cycle 45 55 %

DAI_LRCK Duty Cycle 45 55 %

DAI Sample Rate (Note 17) Fs32 192 kHz

DAI_SDIN Setup Time Before DAI_SCLK Rising Edge tds 10 - ns

DAI_SDIN Hold Time After DAI_SCLK Rising Edge tdh 10 - ns

DAI_SCLK High Time tsckh 20 - ns

DAI_SCLK Low Time tsckl 20 - ns

DAI_LRCK Setup Time Before DAI_SCLK Rising Edge tlrcks 25 - ns

DAI_SCLK Rising Edge Before DAI_LRCK Edge tlrckd 25 - ns

sckh sckl

t

t

DAI_SDINx

lrcks

t

lrckd

t

DAI_SCLK

DAI_LRCK

ds

tdh

t

Figure 6. Serial Audio Interface Timing Figure 7. Serial Audio Interface Timing - TDM Mode

sckh sckl

t

t

DAI_SDIN1

dh

t

ds

t

lrcks

t

lrckd

t

DAI_SCLK

(input)

DAI_LRCK

(input) lrcks

t

MSB MSB-1

14 DS632F1

CS44800

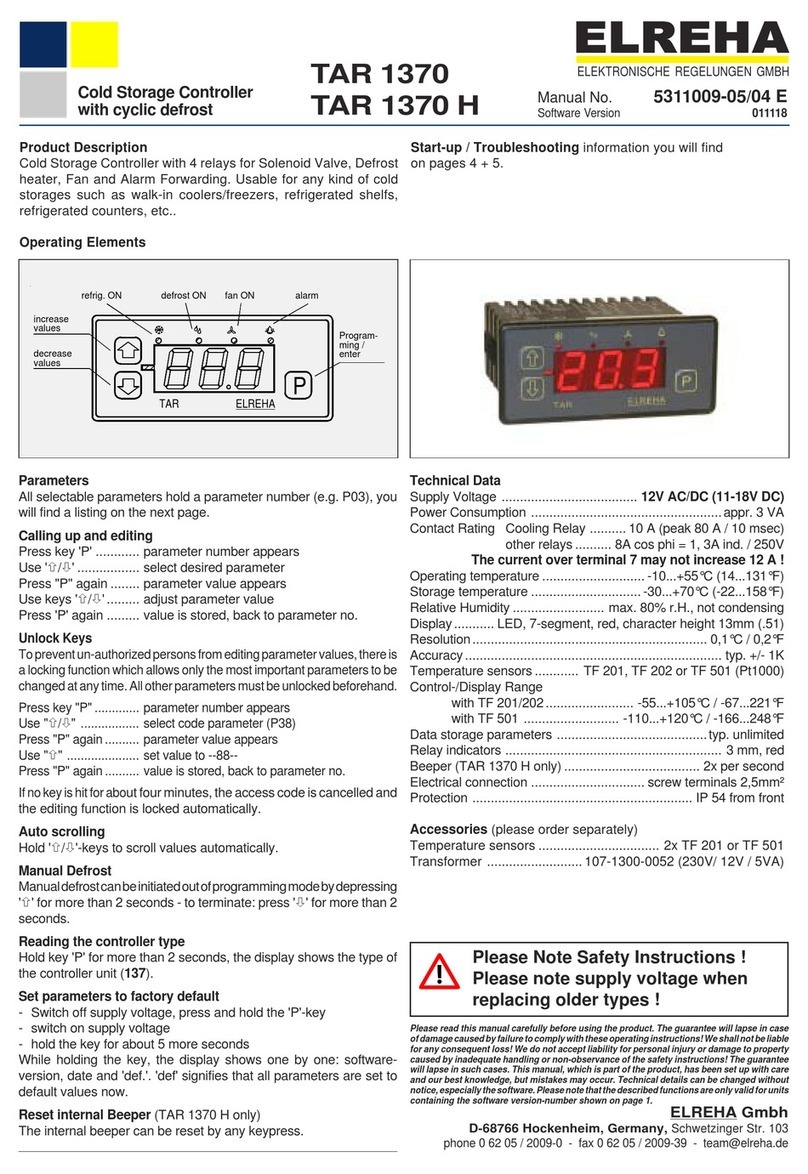

SWITCHING CHARACTERISTICS - CONTROL PORT - I²C FORMAT

(VD = 2.5 V, VDX = VDP = VLS = 3.3 V; VLC = 2.5 V to 5.0 V; Inputs: Logic 0 = GND, Logic 1 = VLC, CL=30pF)

18. Data must be held for sufficient time to bridge the transition time, tf, of SCL.

Parameter Symbol Min Max Unit

SCL Clock Frequency fscl - 100 kHz

Bus Free Time between Transmissions tbuf 4.7 - µs

Start Condition Hold Time (prior to first clock pulse) thdst 4.0 - µs

Clock Low time tlow 4.7 - µs

Clock High Time thigh 4.0 - µs

Setup Time for Repeated Start Condition tsust 4.7 - µs

SDA Hold Time from SCL Falling (Note 18) thdd 10 - ns

SDA Setup time to SCL Rising tsud 250 - ns

Rise Time of SCL and SDA tr-1000ns

Fall Time SCL and SDA tf-300ns

Setup Time for Stop Condition tsusp 4.7 - µs

tbuf thdst thdst

tlow tr

tf

thdd

thigh

tsud tsust

tsusp

Stop Start Start Stop

Repeated

SDA

SCL

Figure 8. Control Port Timing - I²C Format

DS632F1 15

CS44800

SWITCHING CHARACTERISTICS - CONTROL PORT - SPI FORMAT

(VD = 2.5 V, VDP = VLS = 3.3 V; VLC = 2.5 V to 5.0 V; Inputs: Logic 0 = GND, Logic 1 = VLC, CL=30pF)

19. Data must be held for sufficient time to bridge the transition time of CCLK.

20. For fsck <1 MHz.

Parameter Symbol Min Typ Max Units

CCLK Clock Frequency fsck 0-6.0MHz

CS High Time between Transmissions tcsh 1.0 - - µs

CS Falling to CCLK Edge tcss 20 - - ns

CCLK Low Time tscl 66 - - ns

CCLK High Time tsch 66 - - ns

CDIN to CCLK Rising Setup Time tdsu 40 - - ns

CCLK Rising to DATA Hold Time (Note 19) tdh 15 - - ns

CCLK Falling to CDOUT Stable tpd - - 50 ns

Rise Time of CDOUT tr1 - - 25 ns

Fall Time of CDOUT tf1 - - 25 ns

Rise Time of CCLK and CDIN (Note 20) tr2 - - 100 ns

Fall Time of CCLK and CDIN (Note 20) tf2 - - 100 ns

tr2 tf2

tdsu tdh

tsch

tscl

CS

CCLK

CDIN

tcss

tpd

CDOUT

tcsh

Figure 9. Control Port Timing - SPI Format

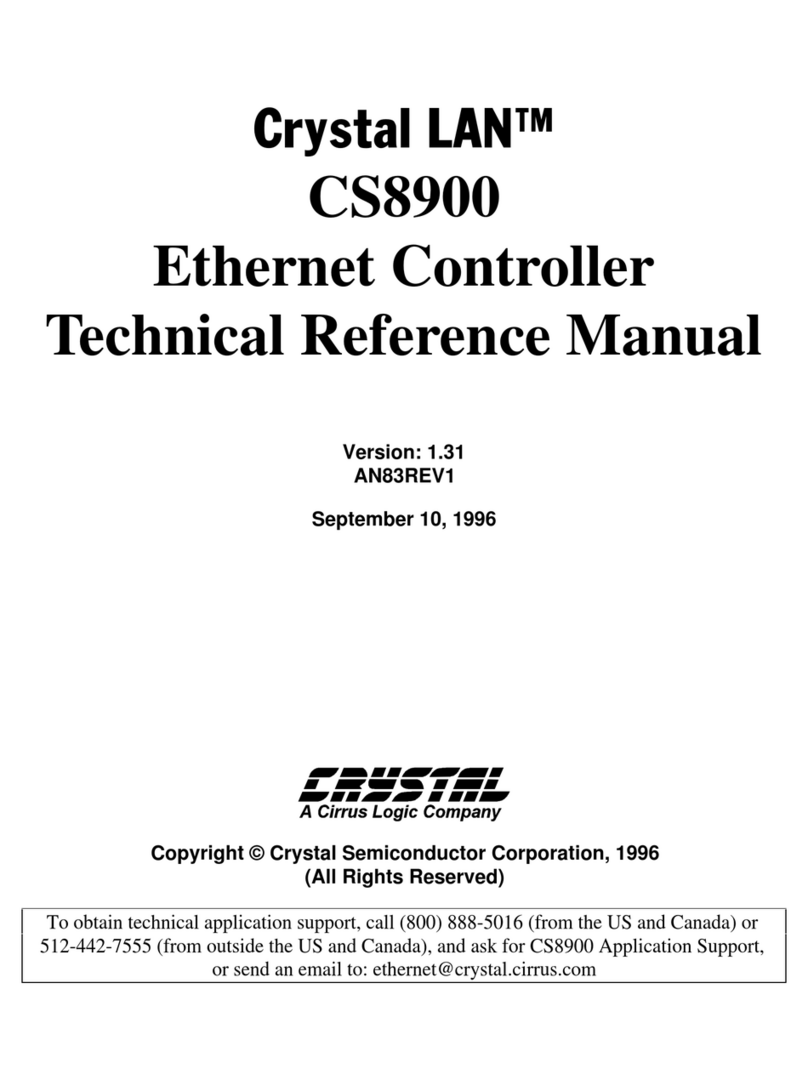

16 DS632F1

CS44800

2. PIN DESCRIPTIONS

Pin Name Pin # Pin Description

Figure 10. CS44800 Pinout Diagram

GND

XTI

XTO

VLS

DAI_MCLK

DAI_SCLK

SCL/CCLK

SDA/CDOUT

AD1/CDIN

AD0/CS

INT

RST

VD

GND

GPIO0

GND

VDP

PWMOUTB2+

VDP

GND

PWMOUTA1+

PWMOUTA1-

PWMOUTB1+

PWMOUTB1-

PWMOUTA2+

PWMOUTA2-

PSR_MCLK

PSR_SYNC

PSR_DATAL

PWMOUTB2-

PWMOUTA3+

PWMOUTA3-

PWMOUTB3+

PWMOUTB3-

PWMOUTA4+

PWMOUTA4-

PWMOUTB4+

PWMOUTB4-

VLC

DAI_LRCK

DAI_SDIN4

DAI_SDIN1

DAI_SDIN2

DAI_SDIN3

GND

VDX

GPIO3

GPIO4

GPIO6

GPIO2

VD

VDP

GND

GND

VDP

SYS_CLK

GND

PSR_RESET

GPIO1

GPIO5

MUTE

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

PSR_EN

PS_SYNC

GND

CS44800

DS632F1 17

CS44800

PS_SYNC 3 Power Supply Synchronization Clock (Output)-The PWM synchronized clock to the

switch mode power supply.

XTI 5 Crystal Oscillator Input (Input) - Crystal Oscillator input or accepts an external clock

input signal that is used to drive the internal PWM core logic.

XTO 6 Crystal Oscillator Output (Output) - Crystal Oscillator output.

SYS_CLK 8 External System Clock (Output) - Clock output. This pin provides a divided down clock

derived from the XTI input.

DAI_MCLK 9 Digital Audio Input Master Clock (Input) - Master audio clock.

DAI_SCLK 10 Digital Audio Input Serial Clock (Input) - Serial clock for the Digital Audio Input Inter-

face. The clock frequency is a multiple of the Left/Right Clock running at Fs.

DAI_LRCK 11 Digital Audio Input Left/Right Clock (Input) - Determines which channel, Left or Right,

is currently active on the serial audio data line. The rate is determined by the sampling fre-

quency Fs.

DAI_SDIN1

DAI_SDIN2

DAI_SDIN3

DAI_SDIN4

12

13

14

15

Digital Audio Input Serial Data (Input) - Input for two’s complement serial audio data.

MUTE 20 Mute (Input) - The device will perform a hard mute on all channels. All internal registers

are not reset to their default settings.

SCL/CCLK 21 Serial Control Port Clock (Input) - Serial clock for the serial control port. Requires an

external pull-up resistor to the logic interface voltage in I²C mode as shown in the Typical

Connection Diagram.

SDA/CDOUT 22 Serial Control Data (Input/Output) - SDA is a data I/O line in I²C mode and requires an

external pull-up resistor to the logic interface voltage, as shown in the Typical Connection

Diagram.; CDOUT is the output data line for the control port interface in SPI mode.

AD1/CDIN 23 Address Bit 1 (I²C)/Serial Control Data (SPI) (Input) - AD1 is a chip address pin in I²C

mode.;CDIN is the input data line for the control port interface in SPI mode.

AD0/CS 24 Address Bit 0 (I²C)/Control Port Chip Select (SPI) (Input)-AD0 is a chip address pin in

I²C mode; CS is the chip select signal in SPI mode.

INT 25 Interrupt Request (Output) - CMOS or open-drain interrupt request output. This pin is

driven to the configured active state to indicate that the PWM Controller has status data

that should be read by the host.

RST 26 Reset (Input) - The device enters a low power mode and all internal registers are reset to

their default settings when low.

GPIO6 29 General Purpose Input, Output (Input/Output)-This pin is configured as an input follow-

ing a RST condition. It can be configured as a general purpose input or output which can

be individually controlled by the Host Controller.

GPIO5 30 General Purpose Input, Output (Input/Output)-This pin is configured as an input follow-

ing a RST condition. It can be configured as a general purpose input or output which can

be individually controlled by the Host Controller.

GPIO4 31 General Purpose Input, Output (Input/Output)-This pin is configured as an input follow-

ing a RST condition. It can be configured as a general purpose input or output which can

be individually controlled by the Host Controller.

GPIO3 32 General Purpose Input, Output (Input/Output)-This pin is configured as an input follow-

ing a RST condition. It can be configured as a general purpose input or output which can

be individually controlled by the Host Controller.

18 DS632F1

CS44800

GPIO2 33 General Purpose Input, Output (Input/Output)-This pin is configured as an input follow-

ing a RST condition. It can be configured as a general purpose input or output which can

be individually controlled by the Host Controller.

GPIO1 34 General Purpose Input, Output (Input/Output)-This pin is configured as an input follow-

ing a RST condition. It can be configured as a general purpose input or output which can

be individually controlled by the Host Controller.

GPIO0 35 General Purpose Input, Output (Input/Output)-This pin is configured as an input follow-

ing a RST condition. It can be configured as a general purpose input or output which can

be individually controlled by the Host Controller.

PSR_MCLK 49 Power Supply Rejection Master Clock (Output) - Master audio clock for external PSR

ADC (CS4461).

PSR_DATAL 50 Power Supply Rejection Input Serial Data (Input) - Input for serial audio data from

external PSR ADC (CS4461).

PSR_SYNC 51 Power Supply Rejection Sync Clock (Input) - Synchronization signal for external PSR

ADC (CS4461).

PSR_RESET 52 Power Supply Rejection Reset (Output)-The reset pin for the external Power Supply

Rejection circuitry.

PSR_EN 2 Power Supply Rejection Enable (Output)-The enable pin for the external Power Supply

Rejection circuitry.

PWMOUTA1+

PWMOUTA1-

PWMOUTB1+

PWMOUTB1-

PWMOUTA2+

PWMOUTA2-

PWMOUTB2+

PWMOUTB2-

PWMOUTA3+

PWMOUTA3-

PWMOUTB3+

PWMOUTB3-

PWMOUTA4+

PWMOUTA4-

PWMOUTB4+

PWMOUTB4-

64

63

61

60

58

57

55

54

47

46

44

43

41

40

38

37

PWM Output (Output) - PWM control signals for the Class D amplifier backend.

VDX 7 Crystal Power (Input) - Positive power supply for the Crystal section.

VD 19, 27 Digital Power (Input) - Positive power supply for the digital section.

VLC 17 Host Interface Power (Input) - Determines the required signal level for the digital

input/output signals for the host interface.

VLS 16 Digital Audio Interface Power (Input) - Determines the required signal level for the digital

input signals for the digital audio interface.

VDP 39,45,

56, 62 PWM Interface Power (Input) - Determines the required signal level for the digital

input/output signals for the PWM and GPIO interface.

20 DS632F1

CS44800

2.1 I/O Pin Characteristics

Signal Name Power

Rail I/O Driver Receiver

RST VLC Input - 2.5 V and 3.3/5.0 V TTL Compatible.

SCL/CCLK VLC Input - 2.5 V and 3.3/5.0 V TTL Compatible, with Hysteresis.

SDA/CDOUT VLC Input /

Output 2.5-5.0 V,

CMOS/Open Drain 2.5 V and 3.3/5.0 V TTL Compatible, with Hysteresis.

AD0/CS VLC Input - 2.5 V and 3.3/5.0 V TTL Compatible, Internal pull-up.

AD1/CDIN VLC Input - 2.5 V and 3.3/5.0 V TTL Compatible, Internal pull-up.

INT VLC Output 2.5-5.0 V,

CMOS/Open Drain -

MUTE VLC Input - 2.5 V and 3.3/5.0 V TTL Compatible.

DAI_SDINx VLS Input - 2.5 V and 3.3/5.0 V TTL Compatible.

DAI_SCLK VLS Input - 2.5 V and 3.3/5.0 V TTL Compatible.

DAI_LRCK VLS Input - 2.5 V and 3.3/5.0 V TTL Compatible.

DAI_MCLK VLS Input - 2.5 V and 3.3/5.0 V TTL Compatible.

SYS_CLK VLS Output 2.5-5.0 V, CMOS -

XTI VDX Input - 2.5 V and 3.3/5.0 V TTL Compatible, Internal pull-down.

XTO VDX Output - -

GPIOx VDP Input /

Output 3.3/5.0 V,

CMOS/Open Drain 3.3/5.0 V TTL Compatible.

PWMOUTAx+/- VDP Output 3.3/5.0 V, CMOS -

PWMOUTBx+/- VDP Output 3.3/5.0 V, CMOS -

PSR_MCLK VDP Output 3.3/5.0 V, CMOS -

PSR_SYNC VDP Input - 3.3/5.0 V TTL Compatible, Internal pull-up.

PSR_DATA VDP Input - 3.3/5.0 V TTL Compatible, Internal pull-up.

PSR_EN VDP Output 3.3/5.0 V, CMOS -

PSR_RESET VDP Output 3.3/5.0 V, CMOS -

PS_SYNC VDP Output 3.3/5.0 V, CMOS -

Table of contents

Other Cirrus Logic Controllers manuals

Cirrus Logic

Cirrus Logic CS44600 User manual

Cirrus Logic

Cirrus Logic CRYSTAL LAN CS890 Product manual

Cirrus Logic

Cirrus Logic Crystal LAN CS8900A User manual

Cirrus Logic

Cirrus Logic Crystal LAN CS8900A Installation and operating instructions

Cirrus Logic

Cirrus Logic Crystal LAN CS8900A Operational manual