A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

Title

Size Document Number Rev

Date: Sheet of

401241

1A

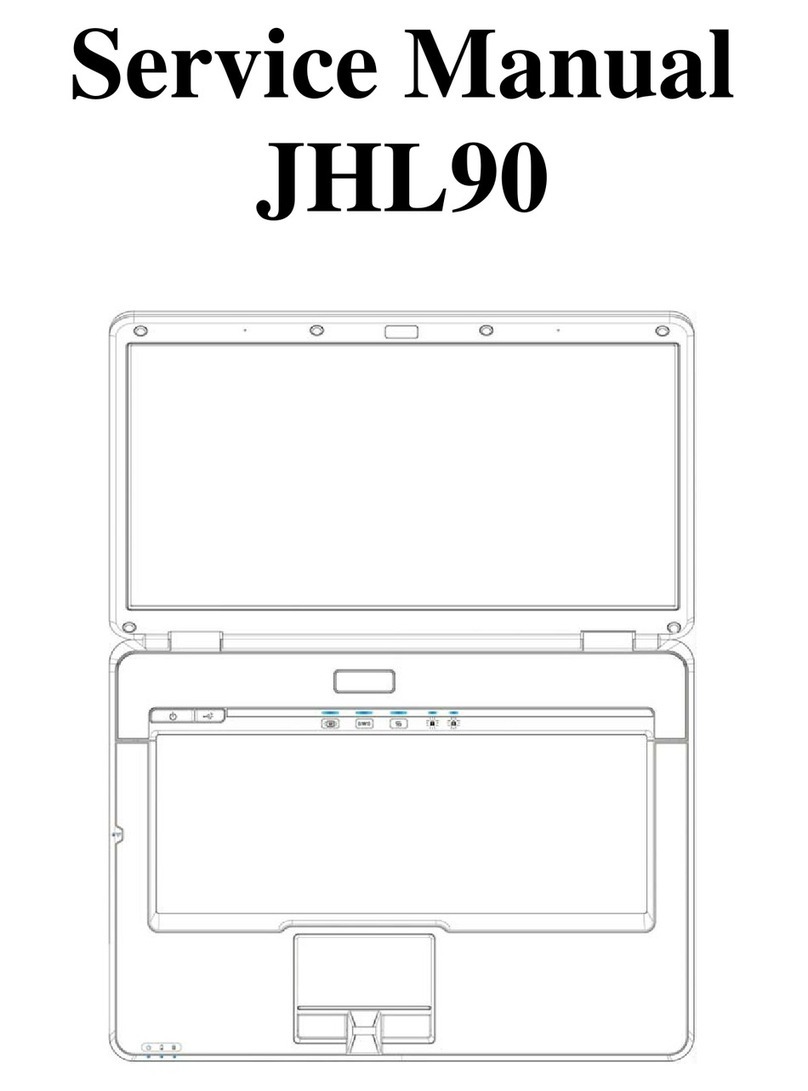

SCHEMATIC, M/B LA-1691

Custom

353,

星期二 一月

07, 2003

Compal Electronics, inc.

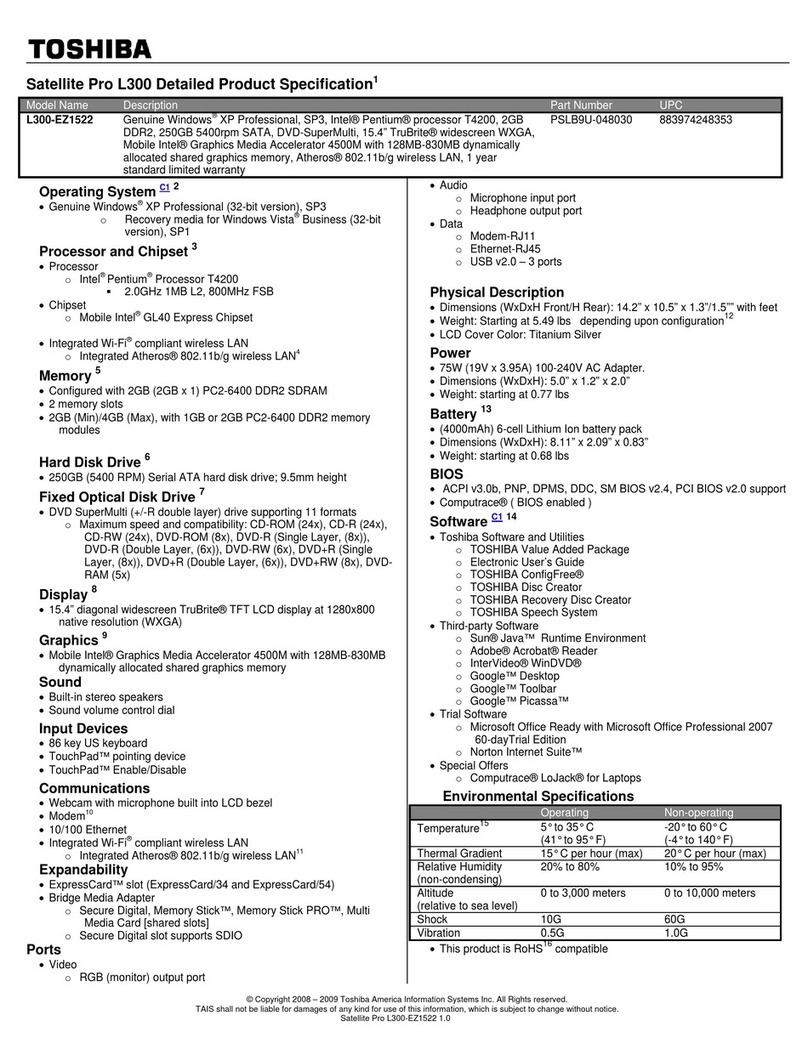

Voltage Rails

VIN

B+

+CPU_VCC

+1.2VP

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

1.2Vswitched power rail for CPU AGTL Bus

External PCI Devices

Device IDSEL# REQ#/GNT# Interrupts

CardBus

Mini-PCI

LAN

AD20

AD18

AD17

EC SM Bus1 address

Device

ADM1032

OZ168

Docking

S1 S3 S5

ON OFF

ON OFF

N/A N/A N/A

N/AN/AN/A

Power Plane Description

OFF

OFF

Note :ON* means thatthis power plane is ON only with AC power available, otherwise it is OFF.

EC SM Bus2 address

Device

Smart Battery

2

1/4

PIRQA/PIRQB(PIRQE/PIRQF)

PIRQC/PIRQD(PIRQG/PIRQH)

EEPROM(24C16/02)

DOT Board

0011 0100 b

1001 110X b

0011 011X b

XXXX XXXXb

0001 011X b

1010 000X b

AGP 4X ON OFF OFF+1.5VS

3 PIRQB(PIRQD)

(24C04)

1011 000Xb

Smart Battery

0001 011X b

ICH3 SM Bus address

Device

Clock Generator (

ICS-950810)

Address

Address Address

1101 001X

+1.25VS 1.25V switched power rail ON OFF OFF

1394

AD16 0

PIRQA

STATE SIGNAL

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

SLP_S1# SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

ON

ON

ON

ON

ON

ON

ON ON

ON

ON

ON

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

LOW

LOW LOW LOW LOW

LOWLOWLOW

LOW

LOW

LOW

HIGH HIGH HIGH HIGH

HIGHHIGHHIGH

HIGH

HIGH

HIGH

+1.2VS 1.2V switched power rail for Montara core ON OFF OFF

1394

CardBus

LAN

MINIPCI

Topology

Mount R458 RP122

Unmount R474 RP125 R533

Trace: PIRQA#_1394

Use IRQA

Trace:PIRQA#/E#

PIRQB#/F#/D#

Use IRQA IRQB

Trace:PIRQB#/F#/D#

Use IRQB

Trace:PIRQC#/G#

PIRQD#/H#

Use IRQC IRQD

Board ID Table for AD channel

Vcc 3.3V +/- 5%

100K +/- 5%Ra

Board ID

Rb V min

0

1

2

3

0

8.2K +/- 5% 0 V

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V 0.503 V

0.819 V 0.538 V

0.875 V

AD_BID

V typ

AD_BID

V

AD_BID

max

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5% 3.300 V

0 V 0 V

4

5

6

7NC

1.036 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V 2.200 V

3.300 V 2.341 V

1.185 V 1.264 V

Board ID

0

1

2

3

4

5

6

7

PCB Revision

0.1 , 0.2

OFF

ON

+5V

ON

OFF

OFF

+3V

2.5V power rail

ON

ON

ON

ON

OFF

RTCVCC

3.3V power rail

OFF

ON

5V power rail

ON*

OFF

5V switched power rail

+2.5V

OFF

RTC power

3.3V switched power rail

ON

OFF

ON

ON

+12VALW

+3VS

ON

+5VALW

ON

+5VS

ON

ON

2.5V switched power rail+2.5VS

ON*ON

ON*

ON

12V always on power rail

+3VALW

OFF

ON

5V always on power rail

3.3V always on power rail

ON

OFF1.8V switched power rail ON OFF

1.8V always power rail ON ON

+1.8VS

ON*+1.8VALW

**

**

0.3

NO DIRECT CD PLAY

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.