Technical Reference Guide

Compaq Deskpro EN Series of Personal Computers

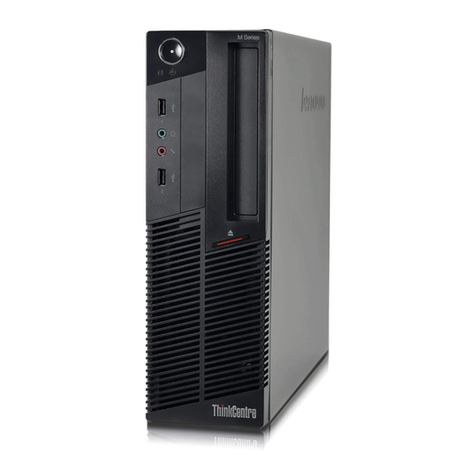

Net PC and Small Form Factor Models

First Edition - June 1998

viii

LIST OF FIGURES

FIGURE 2–1. COMPAQ DESKPRO EN SERIES SMALL FORM FACTOR PERSONAL COMPUTER WITH MONITOR2-1

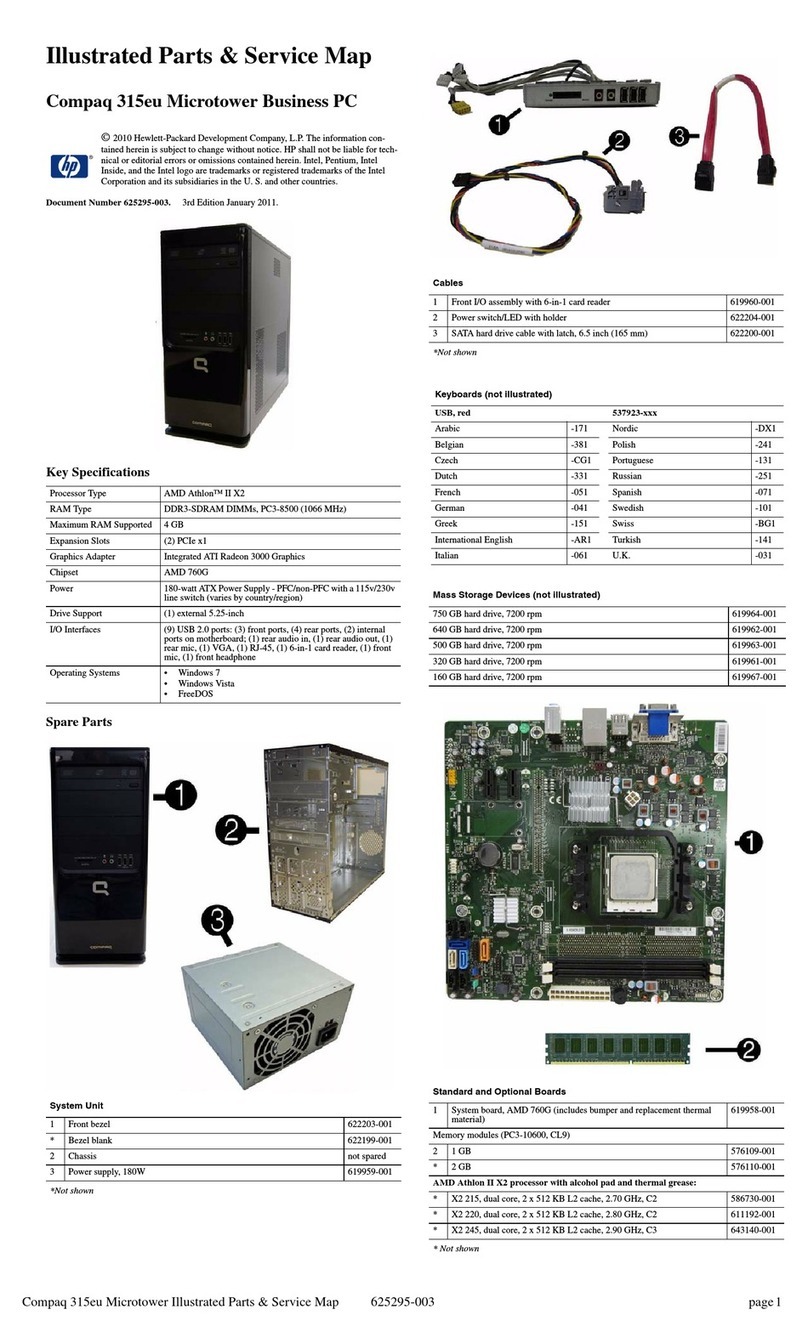

FIGURE 2–2. CABINET LAYOUT, FRONT VIEW .......................................................................................2-4

FIGURE 2–3. CABINET LAYOUT, REAR VIEW .........................................................................................2-5

FIGURE 2–4. DESKTOP CHASSIS LAYOUT, TOP VIEW..............................................................................2-6

FIGURE 2–5. BOARD CONNECTOR AND SWITCH LOCATIONS...................................................................2-7

FIGURE 2–6. SYSTEM ARCHITECTURE, BLOCK DIAGRAM........................................................................2-9

FIGURE 2–7. PENTIUM II SEC CARTRIDGE AND HEAT SINK.................................................................. 2-10

FIGURE 3–1. PROCESSOR/MEMORY SUBSYSTEM ARCHITECTURE............................................................ 3-2

FIGURE 3–2. PENTIUM II PROCESSOR INTERNAL ARCHITECTURE............................................................3-3

FIGURE 3–3. SYSTEM MEMORY MAP..................................................................................................... 3-8

FIGURE 4–1. PCI BUS DEVICES AND FUNCTIONS.....................................................................................4-2

FIGURE 4–2. PCI BUS CONNECTOR (32-BIT 5-VOLT TYPE).................................................................... 4-3

FIGURE 4–3. TYPE 0 CONFIGURATION CYCLE........................................................................................ 4-6

FIGURE 4–4. PCI CONFIGURATION SPACE MAP...................................................................................... 4-7

FIGURE 4–5. AGP 1X DATA TRANSFER (PEAK TRANSFER RATE: 266 MB/S)........................................ 4-12

FIGURE 4–6. AGP 2X DATA TRANSFER (PEAK TRANSFER RATE: 532 MB/S)........................................ 4-13

FIGURE 4–7. ISA BUS BLOCK DIAGRAM................................................................................................ 4-15

FIGURE 4–8. ISA EXPANSION CONNECTOR..........................................................................................4-16

FIGURE 4–9. MASKABLE INTERRUPT PROCESSING, BLOCK DIAGRAM.................................................... 4-22

FIGURE 4–10. CONFIGURATION MEMORY MAP.................................................................................... 4-28

FIGURE 5–1. 40-PIN IDE CONNECTOR. .................................................................................................5-8

FIGURE 5–2. 34-PIN DISKETTE DRIVE CONNECTOR.............................................................................. 5-13

FIGURE 5–3. SERIAL INTERFACES BLOCK DIAGRAM ............................................................................. 5-14

FIGURE 5–4. SERIAL INTERFACE CONNECTOR (MALE DB-9 AS VIEWED FROM REAR OF CHASSIS)........... 5-14

FIGURE 5–5. PARALLEL INTERFACE CONNECTOR (FEMALE DB-25 AS VIEWED FROM REAR OF CHASSIS).. 5-26

FIGURE 5–6. 8042-TO-KEYBOARD TRANSMISSION OF CODE EDH, TIMING DIAGRAM............................ 5-27

FIGURE 5–7. KEYBOARD OR POINTING DEVICE INTERFACE CONNECTOR............................................... 5-33

FIGURE 5–8. UNIVERSAL SERIAL BUS CONNECTOR (ONE OF TWO AS VIEWED FROM REAR OF CHASSIS)..... 5-35

FIGURE 5–9. AUDIO SUBSYSTEM BLOCK DIAGRAM .............................................................................. 5-37

FIGURE 5–10. ANALOG SIGNAL SAMPLING/QUANTIZING ...................................................................... 5-38

FIGURE 5–11. DAC OPERATION ......................................................................................................... 5-38

FIGURE 5–12. AUDIO SUBSYSTEM-TO-ISA BUS PCM AUDIO DATA FORMATS / BYTE ORDERING .......... 5-39

FIGURE 5–13. FM SYNTHESIS PATCH.................................................................................................. 5-40

FIGURE 5–14. AUDIO CONTROLLER-TO-ISA BUS FM AUDIO DATA FORMAT ........................................ 5-40

FIGURE 5–15. 10/100 TX NETWORK INTERFACE CONTROLLER BLOCK DIAGRAM ................................. 5-45

FIGURE 5–16. ETHERNET TPE CONNECTOR (RJ-45, VIEWED FROM CARD EDGE) ................................... 5-47

FIGURE 6-1. GRAPHICS SUBSYSTEM BLOCK DIAGRAM ............................................................................6-2

FIGURE 6-2. ATI 3D RAGE PRO TURBO AGP 2X GRAPHICS CONTROLLER ............................................6-3

FIGURE 6-3. VGA MONITOR CONNECTOR............................................................................................. 6-7

FIGURE 7–1. POWER DISTRIBUTION AND CONTROL, BLOCK DIAGRAM....................................................7-1

FIGURE 7–2. POWER CABLE DIAGRAM ..................................................................................................7-5

FIGURE 7–3. LOW VOLTAGE SUPPLY, BLOCK DIAGRAM.........................................................................7-6

FIGURE 7–4. SIGNAL DISTRIBUTION DIAGRAM.......................................................................................7-7

FIGURE 7–5. HEADER PINOUTS .............................................................................................................7-8