Document Number: 002-14943 Rev. *N Page 3 of 96

Contents

1. Introduction ................................................................... 4

1.1 Overview ............................................................... 4

1.2 Features ................................................................ 5

1.3 Standards Compliance .......................................... 6

2. Power Supplies and Power Management ...................7

2.1 Power Supply Topology ........................................ 7

2.2 WLAN Power Management ................................... 9

2.3 PMU Sequencing .................................................. 9

2.4 Power-Off Shutdown ........................................... 10

2.5 Power-Up/Power-Down/Reset Circuits ...............10

3. Frequency References ............................................... 11

3.1 Crystal Interface and Clock Generation .............. 11

3.2 TCXO ..................................................................11

3.3 Frequency Selection ............................................ 13

3.4 External 32.768 kHz Low-Power Oscillator ......... 14

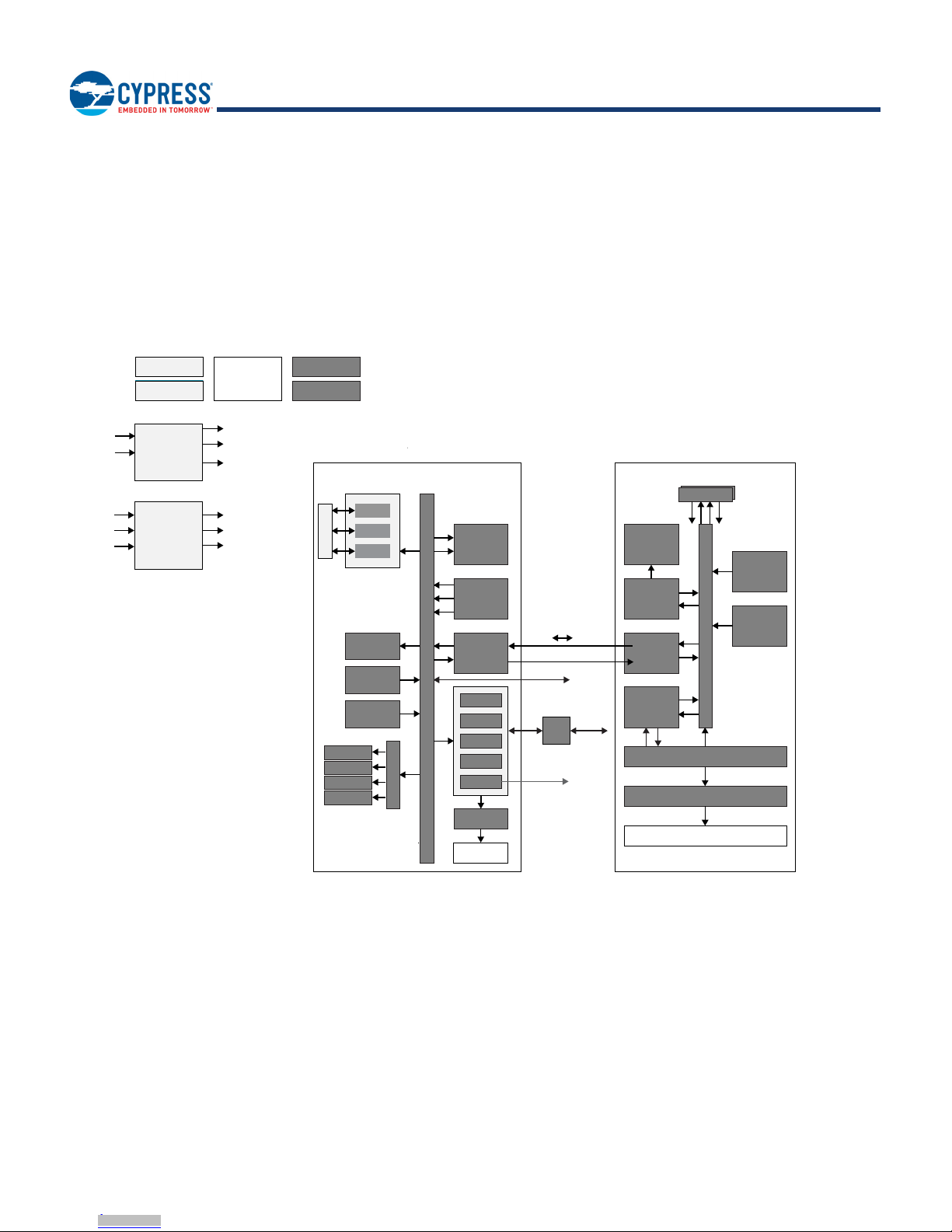

4. Bluetooth Subsystem Overview ................................15

4.1 Features .............................................................. 15

4.2 Bluetooth Radio ................................................... 16

5. Bluetooth Baseband Core ......................................... 17

5.1 Bluetooth 5.0 Features ........................................ 17

5.2 Link Control Layer ............................................... 17

5.3 Test Mode Support .............................................. 17

5.4 Bluetooth Power Management Unit ..................... 18

5.5 Adaptive Frequency Hopping ..............................21

5.6 Advanced Bluetooth/WLAN Coexistence ............21

5.7 Fast Connection (Interlaced Page and Inquiry

Scans) ................................................................ 21

6. Microprocessor and Memory Unit for Bluetooth ..... 22

6.1 RAM, ROM, and Patch Memory ..........................22

6.2 Reset ................................................................... 22

7. Bluetooth Peripheral Transport Unit ........................ 23

7.1 PCM Interface ..................................................... 23

7.2 UART Interface .................................................... 30

7.3 I2S Interface ........................................................ 31

8. WLAN Global Functions ............................................ 34

8.1 WLAN CPU and Memory Subsystem .................. 34

8.2 One-Time Programmable Memory ......................34

8.3 GPIO Interface .................................................... 34

8.4 External Coexistence Interface ...........................34

8.5 UART Interface .................................................... 35

8.6 JTAG Interface .................................................... 35

9. WLAN Host Interfaces ................................................ 36

9.1 SDIO v2.0 ............................................................ 36

9.2 HSIC Interface ..................................................... 38

10. Wireless LAN MAC and PHY ...................................39

10.1 MAC Features ................................................... 39

10.2 WLAN PHY Description ..................................... 42

11. WLAN Radio Subsystem .......................................... 44

11.1 Receiver Path .................................................... 44

11.2 Transmit Path .................................................... 44

11.3 Calibration ......................................................... 44

12. Pinout and Signal Descriptions .............................. 45

12.1 Signal Assignments ........................................... 45

12.2 Signal Descriptions ............................................ 45

12.3 I/O States .......................................................... 54

13. DC Characteristics ................................................... 57

13.1 Absolute Maximum Ratings ............................... 57

13.2 Environmental Ratings ...................................... 57

13.3 Electrostatic Discharge Specifications .............. 58

13.4 Recommended Operating Conditions and DC

Characteristics .................................................... 58

14. Bluetooth RF Specifications .................................... 60

15. WLAN RF Specifications .......................................... 67

15.1 Introduction ........................................................ 67

15.2 2.4 GHz Band General RF Specifications ......... 68

15.3 WLAN 2.4 GHz Receiver Performance

Specifications ..................................................... 68

15.4 WLAN 2.4 GHz Transmitter Performance

Specifications ..................................................... 72

15.5 WLAN 5 GHz Receiver Performance

Specifications ..................................................... 73

15.6 WLAN 5 GHz Transmitter Performance

Specifications ..................................................... 75

15.7 General Spurious Emissions Specifications ...... 76

16. Internal Regulator Electrical Specifications .......... 77

16.1 Core Buck Switching Regulator ......................... 77

16.2 3.3V LDO (LDO3P3) .........................................78

16.3 2.5V LDO (LDO2P5) .........................................79

16.4 HSICDVDD LDO ............................................... 79

16.5 CLDO ................................................................ 80

16.6 LNLDO .............................................................. 81

17. System Power Consumption ...................................82

17.1 WLAN Current Consumption ............................. 82

17.2 Bluetooth and BLE Current Consumption ......... 83

18. Interface Timing and AC Characteristics ............... 84

18.1 SDIO Timing ...................................................... 84

18.2 HSIC Interface Specifications ............................86

18.3 JTAG Timing ..................................................... 86

19. Power-Up Sequence and Timing ............................. 87

19.1 Sequencing of Reset and Regulator Control

Signals ................................................................ 87

20. Package Information ................................................ 90

20.1 Package Thermal Characteristics ..................... 90

20.2 Junction Temperature Estimation and PSIJT

Versus THETAJC ................................................ 90

20.3 Environmental Characteristics ........................... 90

21. Mechanical Information ........................................... 91

22. Ordering Information ................................................ 93

23. Additional Information ............................................. 93

23.1 Acronyms and Abbreviations ............................. 93

23.2 IoT Resources ................................................... 93

Document History ........................................................... 94

Sales, Solutions, and Legal Information ...................... 96

Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.