Document Number: 002-14874 Rev. *S Page 7 of 51

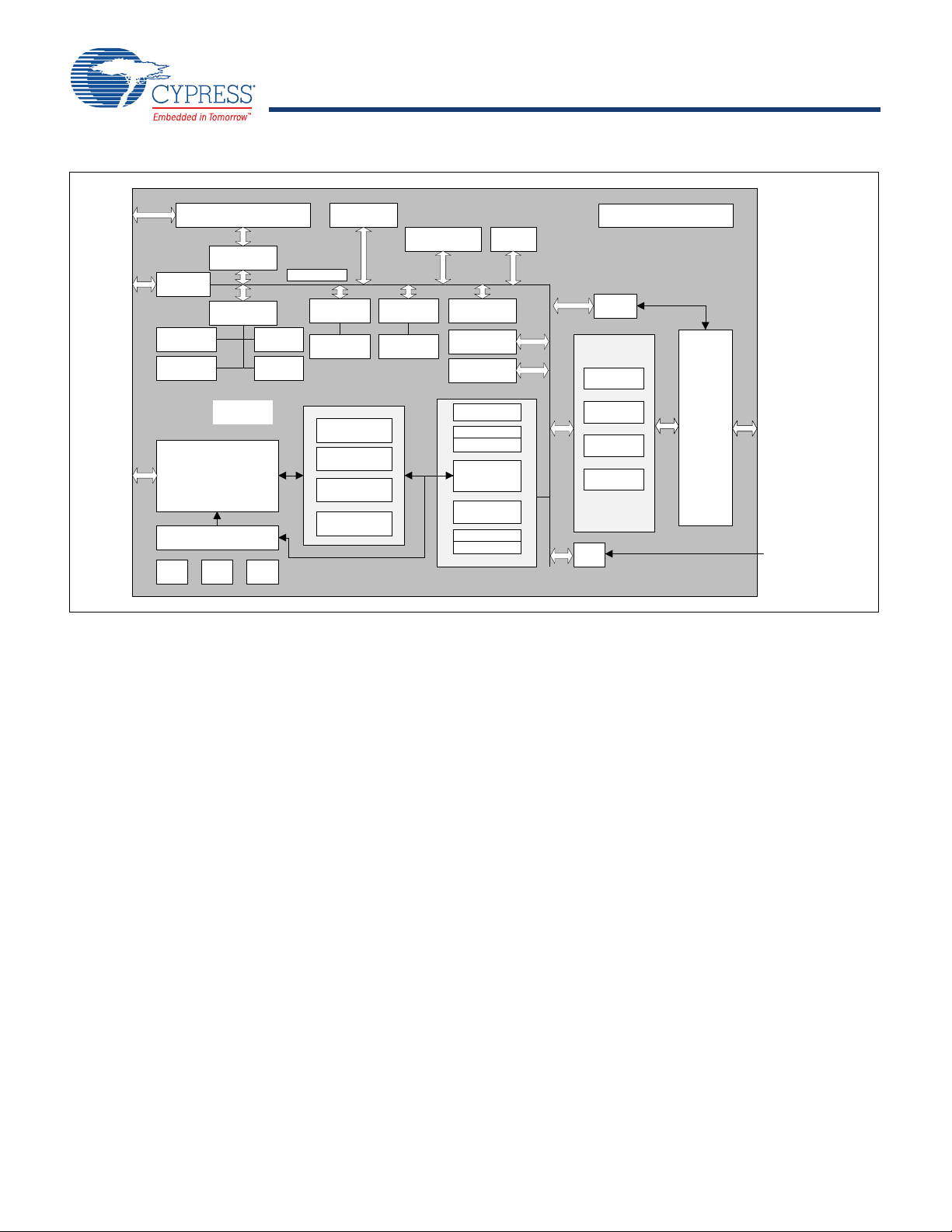

1.3.1 Transmit

The CYW20734 features a fully integrated zero-IF transmitter. The baseband transmit data is GFSK-modulated in the modem block

and upconverted to the 2.4 GHz ISM band in the transmitter path. The transmitter path consists of signal filtering, I/Q upconversion,

output power amplifier, and RF filtering. The transmitter path also incorporates /4-DQPSK for 2 Mbps and 8-DPSK for 3 Mbps to

support EDR. The transmitter section is compatible to the Bluetooth Low Energy specification. The transmitter PA bias can also be

adjusted to provide Bluetooth class 1 or class 2 operation.

1.3.2 Digital Modulator

The digital modulator performs the data modulation and filtering required for the GFSK, /4-DQPSK, and

8-DPSK signal. The fully digital modulator minimizes any frequency drift or anomalies in the modulation characteristics of the trans-

mitted signal and is much more stable than direct VCO modulation schemes.

1.3.3 Digital Demodulator and Bit Synchronizer

The digital demodulator and bit synchronizer take the low-IF received signal and perform an optimal frequency tracking and bit-

synchronization algorithm.

1.3.4 Power Amplifier

The fully integrated PA supports Class 1 or Class 2 output using a highly linearized, temperature-compensated design. This provides

greater flexibility in front-end matching and filtering. Due to the linear nature of the PA combined with some integrated filtering, external

filtering is required to meet the Bluetooth and regulatory harmonic and spurious requirements. For integrated mobile handset appli-

cations in which Bluetooth is integrated next to the cellular radio, external filtering can be applied to achieve near thermal noise levels

for spurious and radiated noise emissions. The transmitter features a sophisticated on-chip transmit signal strength indicator (TSSI)

block to keep the absolute output power variation within a tight range across process, voltage, and temperature.

1.3.5 Receiver

The receiver path uses a low-IF scheme to downconvert the received signal for demodulation in the digital demodulator and bit

synchronizer. The receiver path provides a high degree of linearity, an extended dynamic range, and high-order on-chip channel

filtering to ensure reliable operation in the noisy 2.4 GHz ISM band. The front-end topology, with built-in out-of-band attenuation,

enables the CYW20734 to be used in most applications with minimal off-chip filtering. For integrated handset operation, in which the

Bluetooth function is integrated close to the cellular transmitter, external filtering is required to eliminate the desensitization of the

receiver by the cellular transmit signal.

1.3.6 Digital Demodulator and Bit Synchronizer

The digital demodulator and bit synchronizer take the low-IF received signal and perform an optimal frequency tracking and bit

synchronization algorithm.

1.3.7 Receiver Signal Strength Indicator

The radio portion of the CYW20734 provides a receiver signal strength indicator (RSSI) signal to the baseband, so that the controller

can take part in a Bluetooth power-controlled link by providing a metric of its own receiver signal strength to determine whether the

transmitter should increase or decrease its output power.

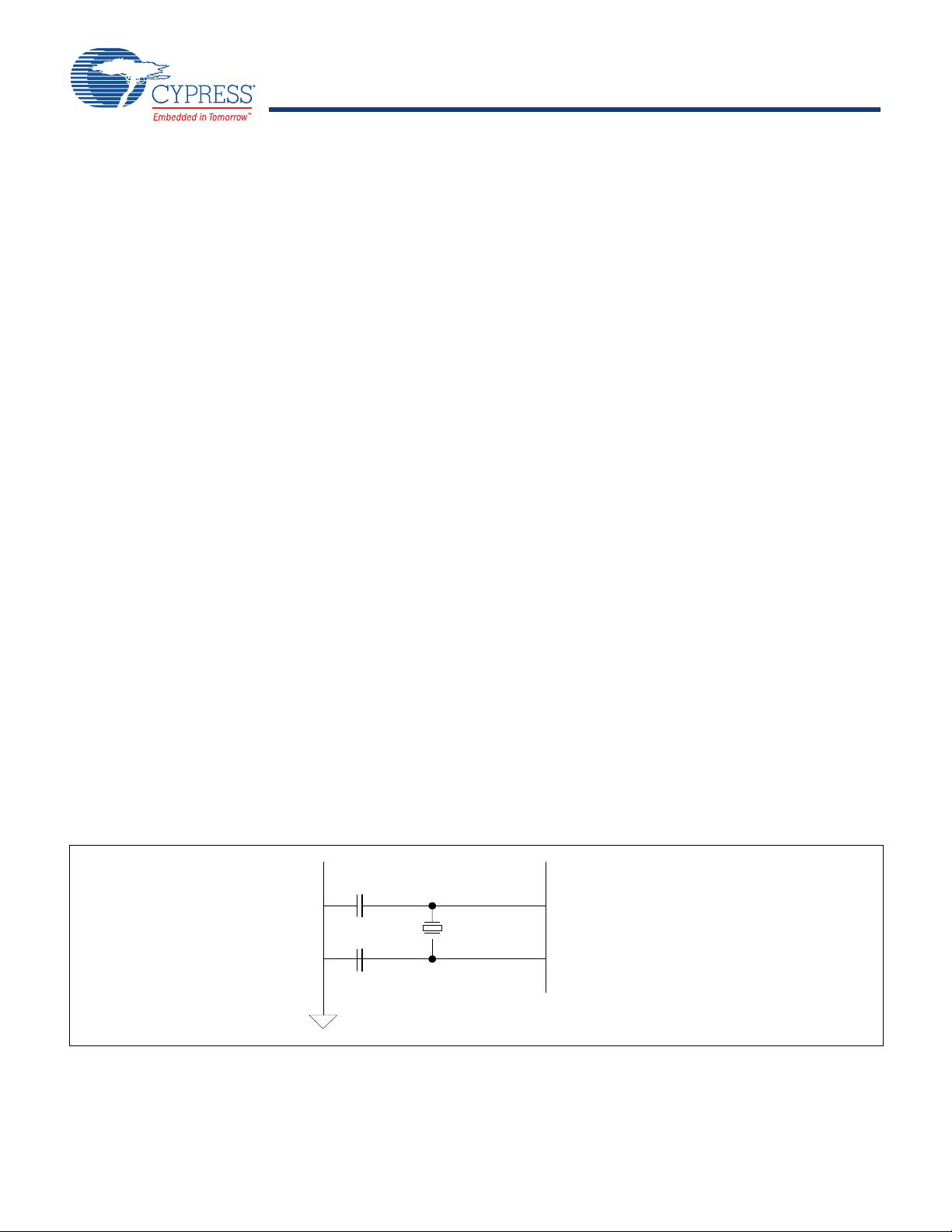

1.3.8 Local Oscillator Generation

A local oscillator (LO) generation provides fast frequency hopping (1600 hops/second) across the 79 maximum available channels.

The LO generation subblock employs an architecture for high immunity to LO pulling during PA operation. The CYW20734 uses an

internal RF and IF loop filter.

1.3.9 Calibration

The CYW20734 radio transceiver features an automated calibration scheme that is fully self-contained in the radio. No user interaction

is required during normal operation or during manufacturing to provide optimal performance. Calibration tunes the performance of all

the major blocks within the radio to within 2% of optimal conditions, including gain and phase characteristics of filters, matching

between key components, and key gain blocks. This takes into account process variation and temperature variation. Calibration occurs

transparently during normal operation during the settling time of the hops, and calibrates for temperature variations as the device

cools and heats during normal operation in its environment.

1.3.10 Internal LDO

The CYW20734 has a 1.2V internal LDO that supplies power to the baseband and the radio.