2

DN-D9000

SPECIFICATIONS

GENERAL

Type: Twin mechanism compact disc player with wired remote control

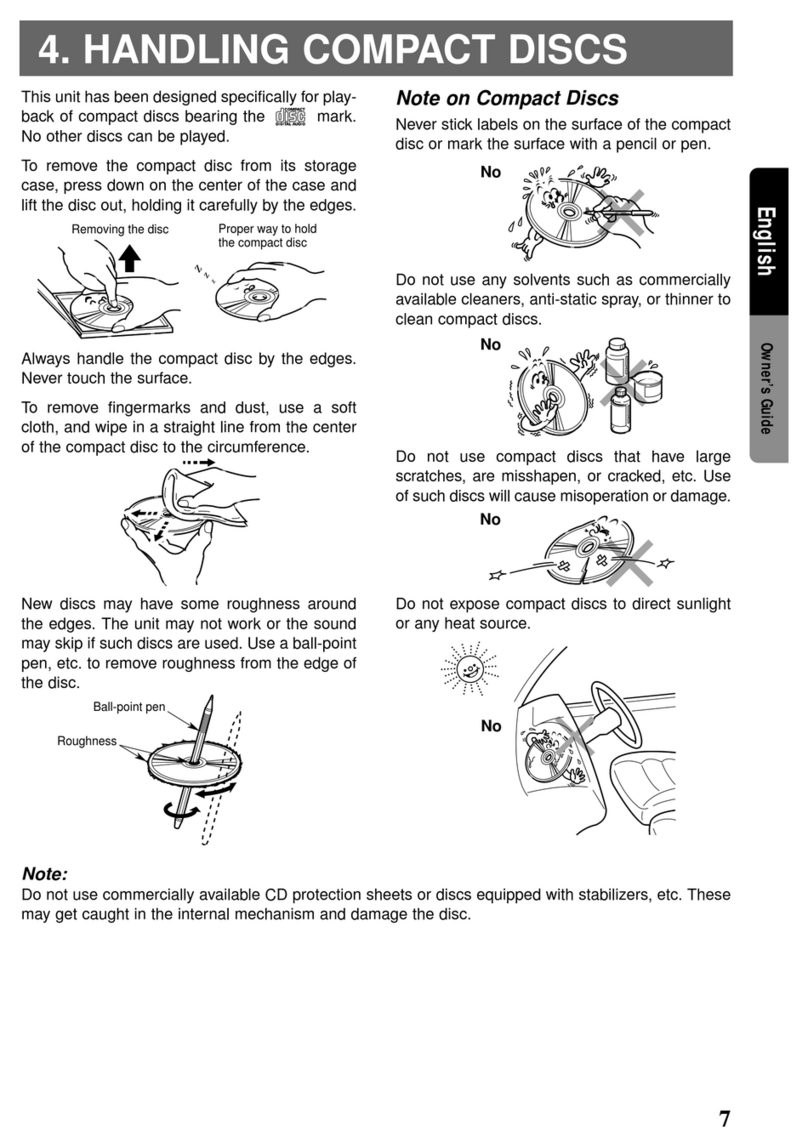

Disc Type: Standard compact discs (12 cm and 8 cm discs)

For CD-R and CD-RW discs, only finalized ones can be played back.

However, some discs may not be playable depending on their recording

conditions.

Dimensions: Player unit: 482 (W) ×88 (H) ×252 (D) mm (without feet)

18-31/32" (W) ×3-15/32" (H) ×9-59/64" (D)

Remote control unit: 482 (W) ×62 (H) ×40 (D) mm (without feet)

18-31/32" (W) ×2-7/16" (H) ×1-37/64" (D)

Installation: 19-inch rack mountable

Player unit: 2U

Remote control unit: 3U

Player unit: 8 kg (17 lbs. 10.2oz)

Remote control unit: 4 kg (8 lbs. 13.1oz)

Power Supply: U.S.A. & Canada model: 120 V AC ±10 %, 60 Hz

Europe & Asia model: 230 V AC ±10 %, 50 Hz

Power Consumption: 33 W

Environmental Conditions: Operational temperature: 5 to 35 °C (41 to 95 °F)

Operational humidity: 25 to 85 % (no condensation)

Storage temperature: −20 to 60 °C (4 to 140 °F)

AUDIO SECTION

Main out/Monitor out

Quantization: 24-bit linear per channel

Sampling Frequency: 44.1 kHz at normal pitch

Oversampling Rate: 8 times

Total Harmonic Distortion: ±0.01 % or less

S/N Ratio: 90 dB or more

Channel Separation: 85 dB or more

Frequency Response: 20 to 20,000 Hz

Analog output

Main Out Level: 2.0 Vrms

Monitor Out Level: 2.0 Vrms

Digital Output:

Signal Format: SPDIF (−6 dB)

Output Level: 0.5 Vp-p 75 Ω/ohms

Load Impedance: 10 kΩ/kohms or more

FUNCTIONS

Instant Start: Within 20 msec.

Variable Pitch

Main, αTrack: ±4 % (0.05 % pitch), ±10 % (0.1 % pitch), ±16 % (0.1 % pitch),

±24 % (0.1 % pitch), ±100 % (1 % pitch)

Pitch Bend: Pitch range: ±4 %, ±10 % : ±12 %

Pitch range: ±16 %, ±24 %: ±26 %

Pitch range: ±100 % : ±99 %

SAMPLER

Sampling: 44.1 kHz

Length: 15 sec

Output Level: 2.0 Vrms (Variable/−14~+6 dB)

Variable Pitch: ±24 % (0.1 % pitch)

Search Precision: 1/75 sec (1 subcode frame)

Max. Scan Speed: Over 20 times normal speed

Max. Memo Memory Steps: 5,000 steps

SAFETY PRECAUTIONS

The following check should be performed for the continued protection of the customer and service technician.

LEAKAGE CURRENT CHECK

Before returning the unit to the customer, make sure you make either (1) a leakage current check or (2) a line to chassis

resistance check. If the leakage current exceeds 0.5 milliamps, or if the resistance from chassis to either side of the

power cord is less than 460 kohms, the unit is defective.