3.1.4.3

3.1.4.4

3.1.4.5

3.1.4.6

3.1.4.7

3.1.5

3.1.5.1

3.1.5.2

3.2

3.2.1

3.2.2

3.2.3

3.2.4

3.2.5

3.2.6

3.2.7

3.2.8

3.2.9

3.3

3.3.1

3.3.2

3.3.3

3.3.4

3.3.5

3.3.6

3.3.7

3.3.8

3.3.9

3.3.10

3.3.11

3.3.12

3.3.13

3.3.14

3.3.15

3.3.16

3.4

3.5

3.5.1

3.5.2

3.6

3.6.1

3.6.2

3.6.3

3.6.4

3.6.4.1

3.6.4.2

3.6.5

3.6.5.1

3.6.5.2

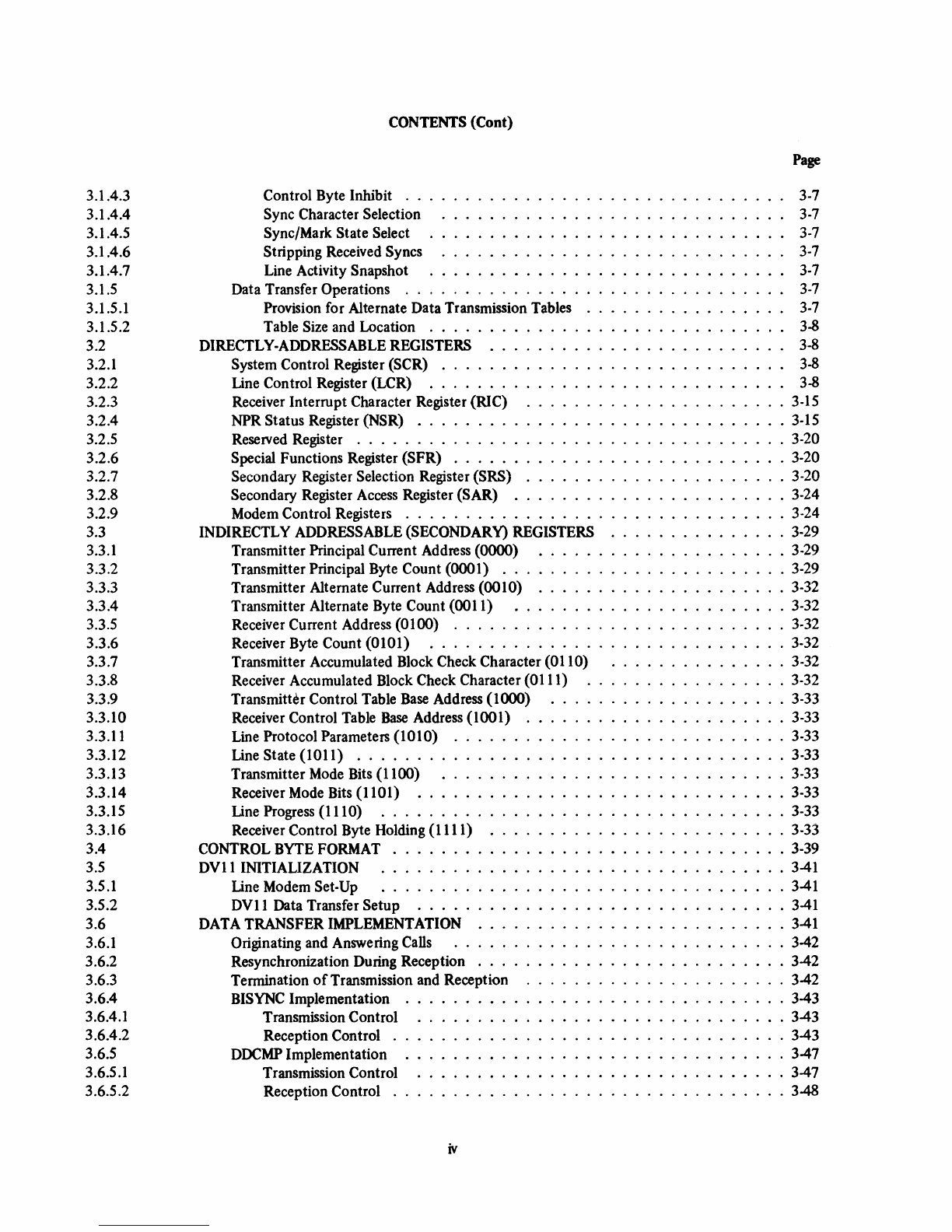

CONTENTS (Cont)

Page

Control Byte Inhibit

...

. . . . . . . . . . . . . . . . . . . 3-7

Sync Character Selection . . . . . . . . . . . . . . . . . . . 3-7

Sync/Mark State Select . . . .

..

............

3-7

Stripping Received Syncs

......................

3-7

Line Activity Snapshot . . . . . . . . . . . . . . . . . . . . . . . . 3-7

Data Transfer Operations

....................

3-7

Provision for Alternate Data Transmission Tables

............

3-7

Table Size and Location . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

DIRECTLY-ADDRESSABLE REGISTERS

..................

3-8

System Control Register (SCR) . . . . . . . . . . . . . . 3-8

Line Control Register (LCR)

..........

3-8

Receiver Interrupt Character Register (RIC)

....

3-15

NPR Status Register (NSR)

..

. . . . . . . . . . . . . . . . 3-15

Reserved Register

.....

. . . . . . . . . . . . . . . . . . 3-20

Special Functions Register

(SFR)

. . . . . . . . . . . . . . . 3-20

Secondary Register Selection Register (SRS)

....

. . . . . . . 3-20

Secondary Register Access Register (SAR)

.....

. . . . . . . 3-24

Modem Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-24

INDIRECTLY ADDRESSABLE (SECONDARy) REGISTERS

...............

3-29

Transmitter Principal Current Address

(0000)

. . . . . . . . . . . 3-29

Transmitter Principal Byte Count (000

I)

..

. . . . . . . . . . . . . . 3-29

Transmitter Alternate Current Address

(0010)

..

.

..........

3-32

Transmitter Alternate Byte Count

(00

II)

. . . . . . . 3-32

Receiver Current Address (0100)

.........

.

........

3-32

Receiver Byte Count

(0101)

............

.

..........

3-32

Transmitter Accumulated Block Check Character (0110)

...............

3-32

Receiver Accumulated Block Check Character (0111)

....

,

....

3-32

Transmitter Control Table Base Address

(I

(00)

. . . . .

...

. 3-33

Receiver Control Table

Base

Address

(100

1) . . . . . .

..

. . 3-33

Line Protocol Parameters

(1010)

.......

. . . . . .

..

3-33

Line State

(lOll)

...

. . . . . . . . . . . . . . . . . . . . . . . . .

..

3-33

Transmitter Mode Bits (1100) . . . . . . . . . .

..

3-33

Receiver Mode Bits (1101)

....

. . . . . . . . . .

..

3-33

Line Progress (1110)

..........

.

..............

3-33

Receiver Control Byte Holding

(1111)

. . . . . . . . . . . . .

3-33

CONTROL BYTE

FORMAT.

. . . . . . . . . . . . . . . . . . . . . . . . . . 3-39

DVl1

INITIALIZATION . . . . . . . . . . . . .

..............

3-41

Line Modem Set-Up . . . . . . . . . . . . . . . . . . . . . . . . . . 3-41

DVl1

Data Transfer

Setup.

. . . . . . . . . . . . . . . .

..

.

.....

3-41

DATA TRANSFER IMPLEMENTATION

.......................

3-41

Originating and Answering Calls . . . . . . . . . . . . . . . . . . . . . . . . . . 3-42

Resynchronization During Reception . . . . . . . .

..

...........

. 3-42

Termination

of

Transmission and Reception

...........

. . 3-42

BISYNC Implementation

...

. . . . . . . . . . . . . . 3-43

Transmission Control

....................

. . 3-43

Reception Control . . . . . . . . . . . . . . . . . . . . . . . . 3-43

DDCMP Implementation

......

. . . . . . . . . . . . . . . . . . . . . . 3-47

Transmission Control . . . . . . . . . . . . . .

.....

3-47

Reception Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-48

iv