Reference Manual epc10x

Table of Contents

1. Introduction.................................................................................................................................................... 3

2. Light Curtain Principle..................................................................................................................................

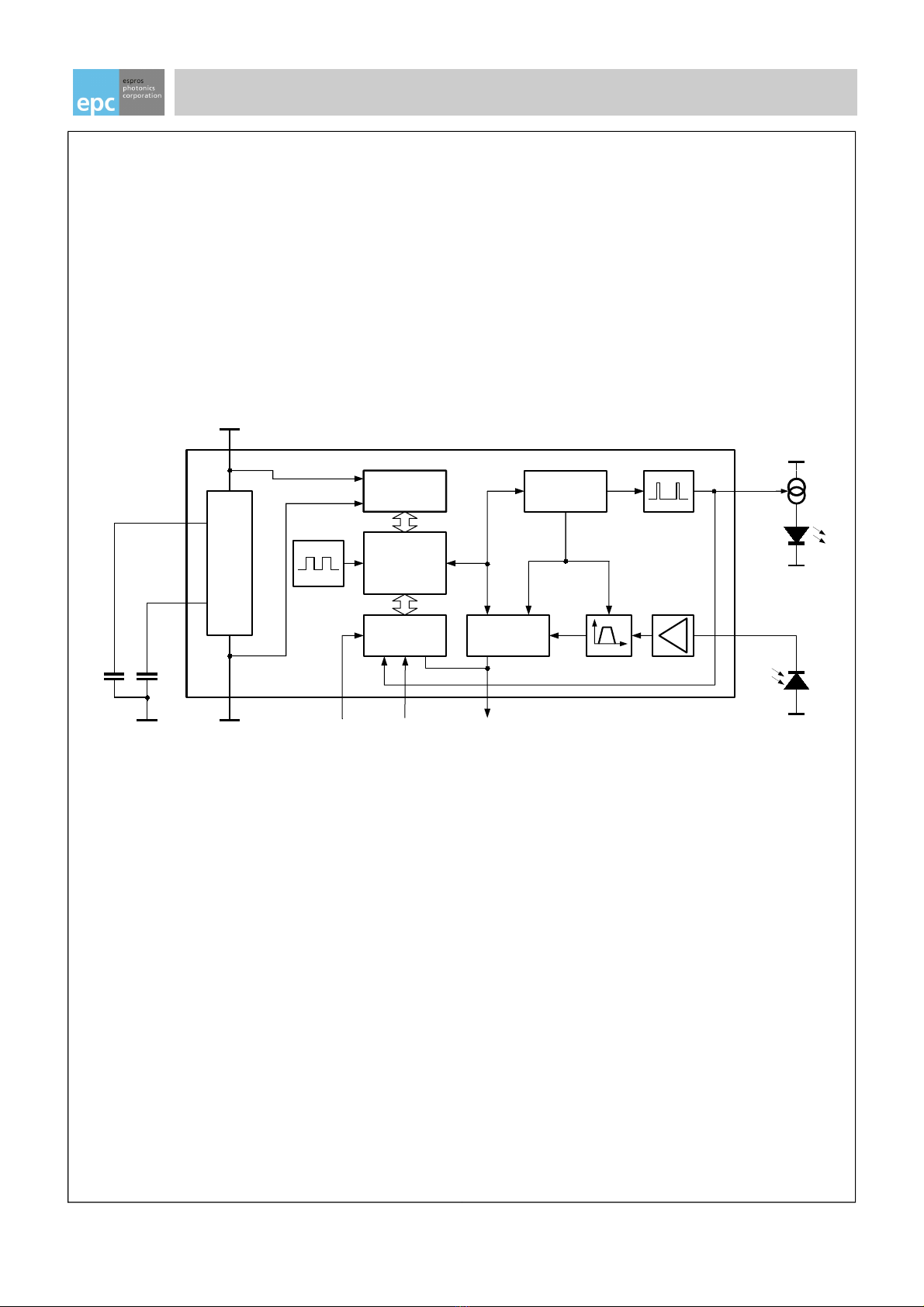

2.1 System Overvie ........................................................................................................................................................................................... 4

2.2 Light Curtain Receiver Edge..........................................................................................................................................................................6

2.3 Light Curtain Emitter Edge.............................................................................................................................................................................6

3. 2-Wire Bus...................................................................................................................................................... 7

3.1 General Description....................................................................................................................................................................................... 7

3.2 Bus Wire Considerations............................................................................................................................................................................... 8

3.3 Bus Signal Waveform.................................................................................................................................................................................... 9

. Parameter Memory...................................................................................................................................... 10

4.1 Receiver Parameters (epc100)....................................................................................................................................................................11

4.2 Sample Receiver Parameter Setting........................................................................................................................................................... 13

4.3 Transmitter Parameters (epc101)................................................................................................................................................................14

4.4 Sample Transmitter Parameter Setting....................................................................................................................................................... 16

5. Timing........................................................................................................................................................... 17

5.1 Overvie ...................................................................................................................................................................................................... 17

5.2 Timing Details.............................................................................................................................................................................................. 17

5.3 Special Cases.............................................................................................................................................................................................. 18

6. SPI Interface................................................................................................................................................. 19

6.1 Timing Specifications...................................................................................................................................................................................19

6.2 General Description..................................................................................................................................................................................... 19

6.3 Command List..............................................................................................................................................................................................20

6.4 Detailed Command Descriptions................................................................................................................................................................. 21

7. Address Programming................................................................................................................................ 2

7.1 General Description..................................................................................................................................................................................... 24

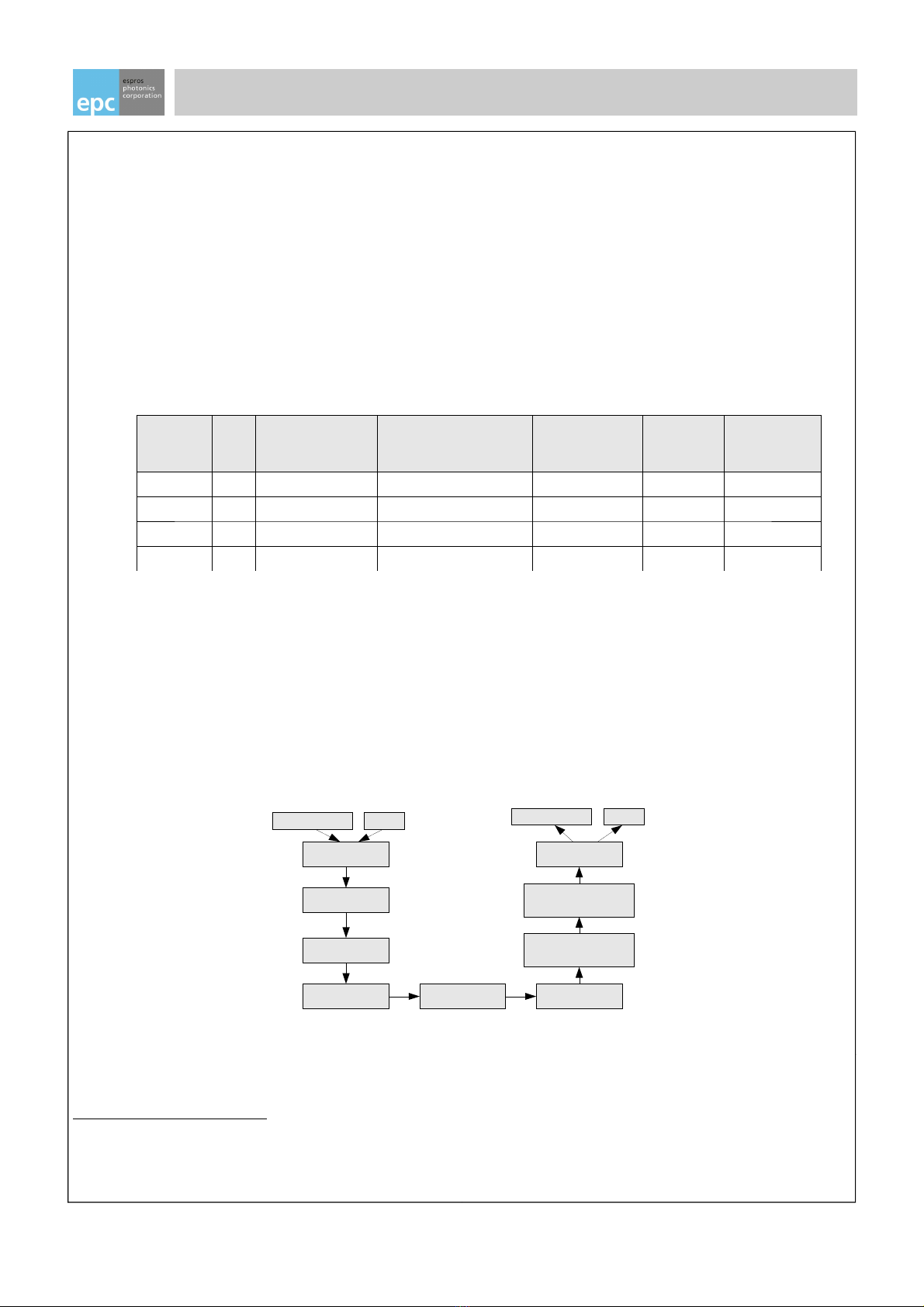

7.2 Programming Procedure..............................................................................................................................................................................25

8. Considerations for Safety Applications..................................................................................................... 26

8.1 Data Integrity on the 2-Wire Po er-Bus...................................................................................................................................................... 26

8.2 Residual Error Rate..................................................................................................................................................................................... 26

8.3 Error Cases..................................................................................................................................................................................................26

8.4 Error Codes..................................................................................................................................................................................................26

© 2012 ESPROS Photonics Corporation

Characteristics subject to change without notice

Page 2/26 Reference Manua epc100 - V2.2