FSD200

7

Product Information

Basic system topology of FSD200/210 is the same as

the original FSDH565/0165 devices. The FSD210

devices require a bias winding, whereas the FSD200

devices do not. Other features of the two types of

devices are almost the same and are listed below.

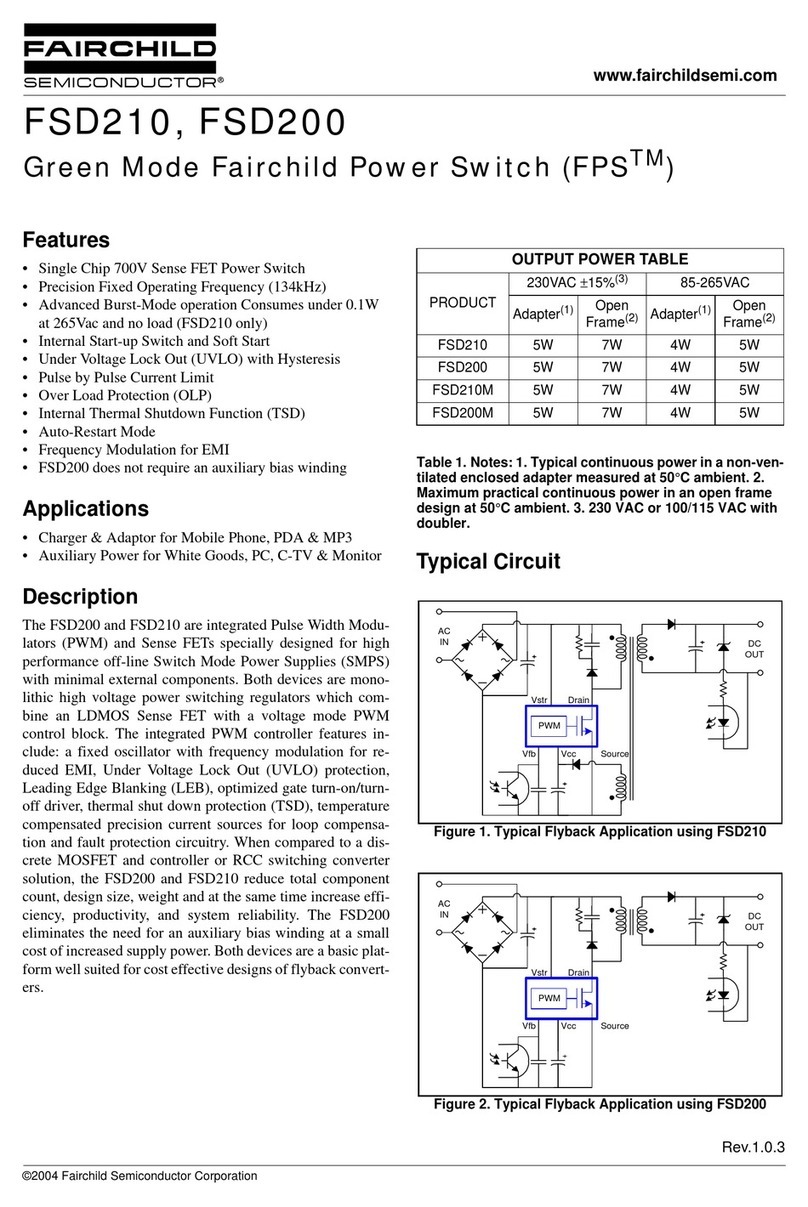

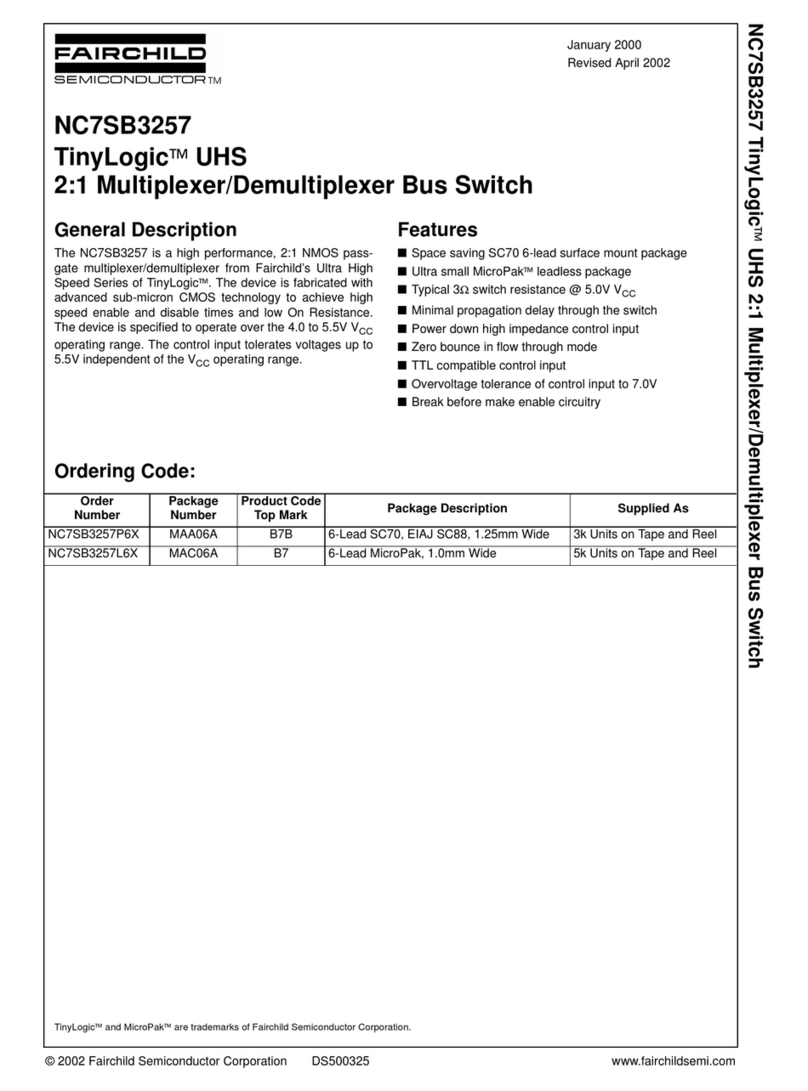

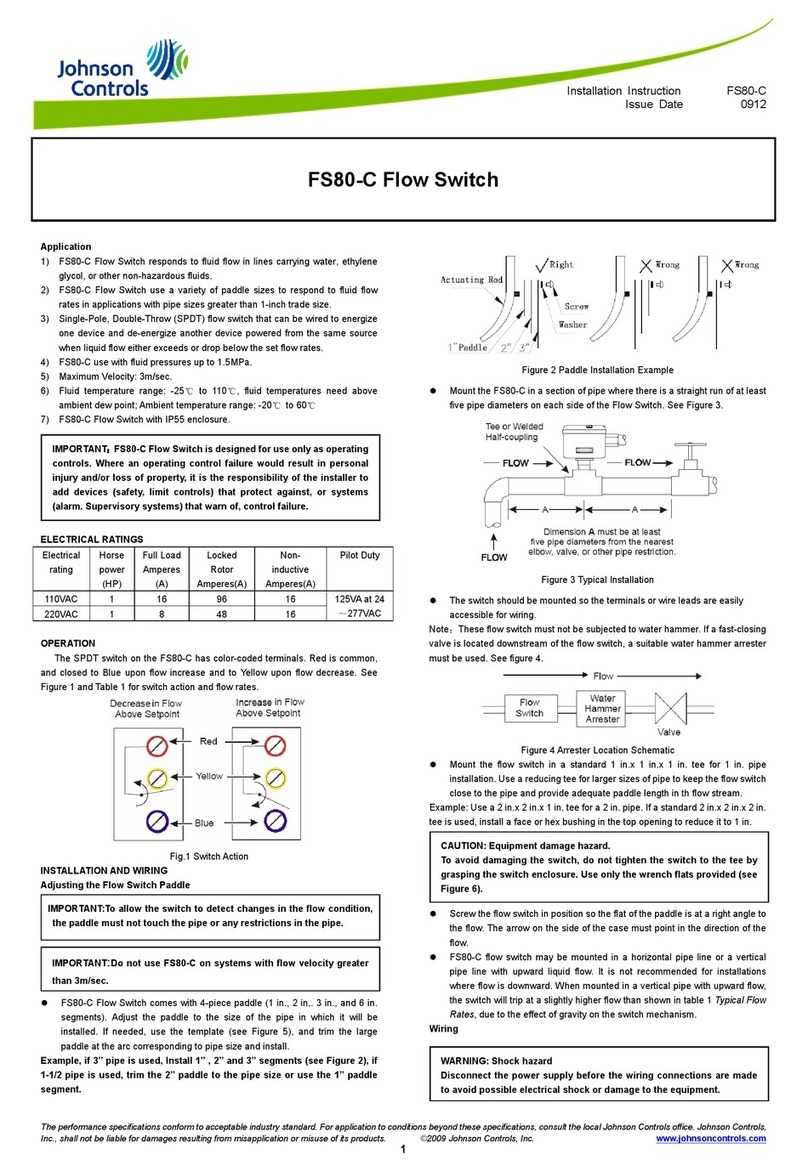

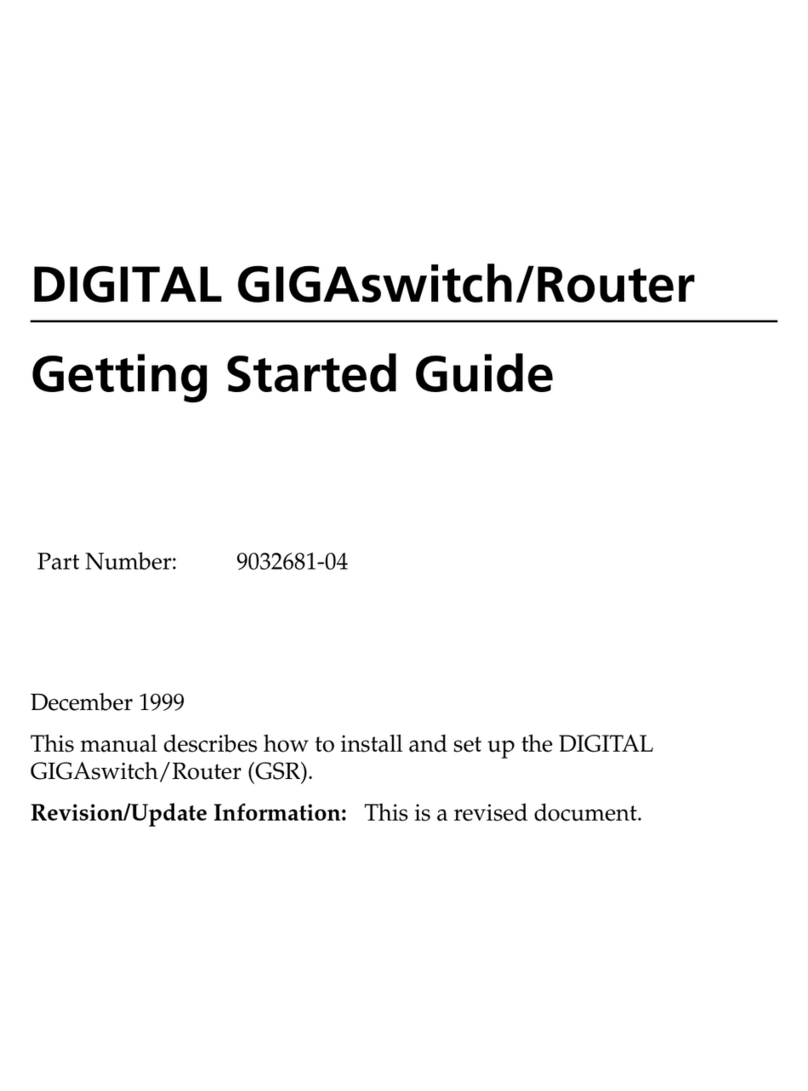

Figure 1. Line-up Table

Functional Description

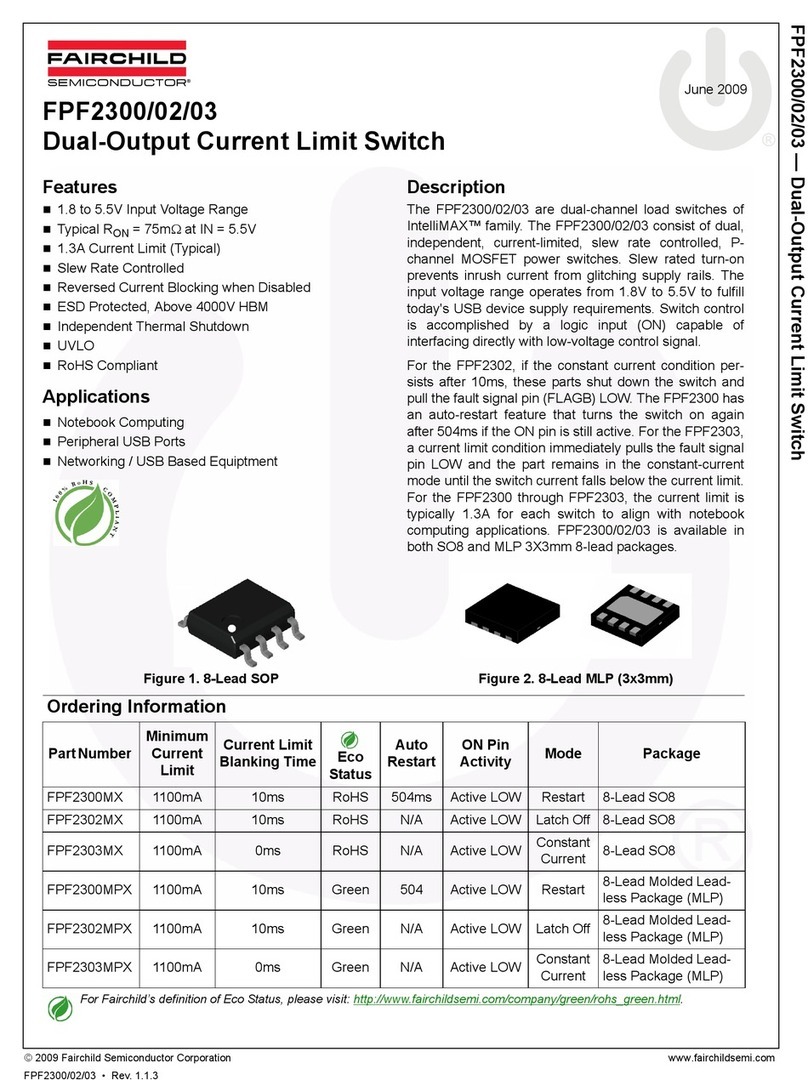

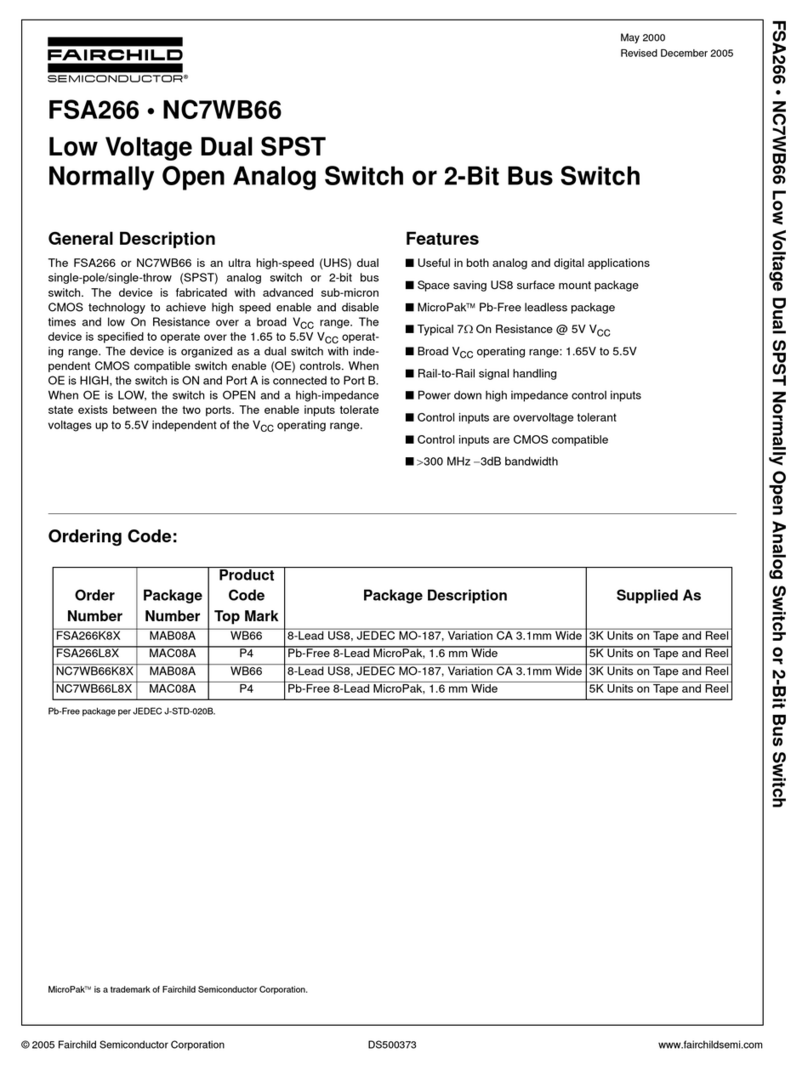

1. Startup : At startup, an internal high voltage current

source supplies the internal bias and charges the

external Vcc capacitor as shown in Figure 1. In the

case of the FSD210, when Vcc reaches 8.7V the

device starts switching and the internal high voltage

current source is disabled. The device continues to

switch provided that Vcc does not drop below 6.7V.

After startup the bias is supplied from the auxiliary

transformer winding. In the case of FSD200, Vcc is

continuously supplied from the external high voltage

source and Vcc is regulated to 7V by an internal high

voltage regulator (HV Reg). The internal startup switch

is not disabled and an auxiliary winding is not required.

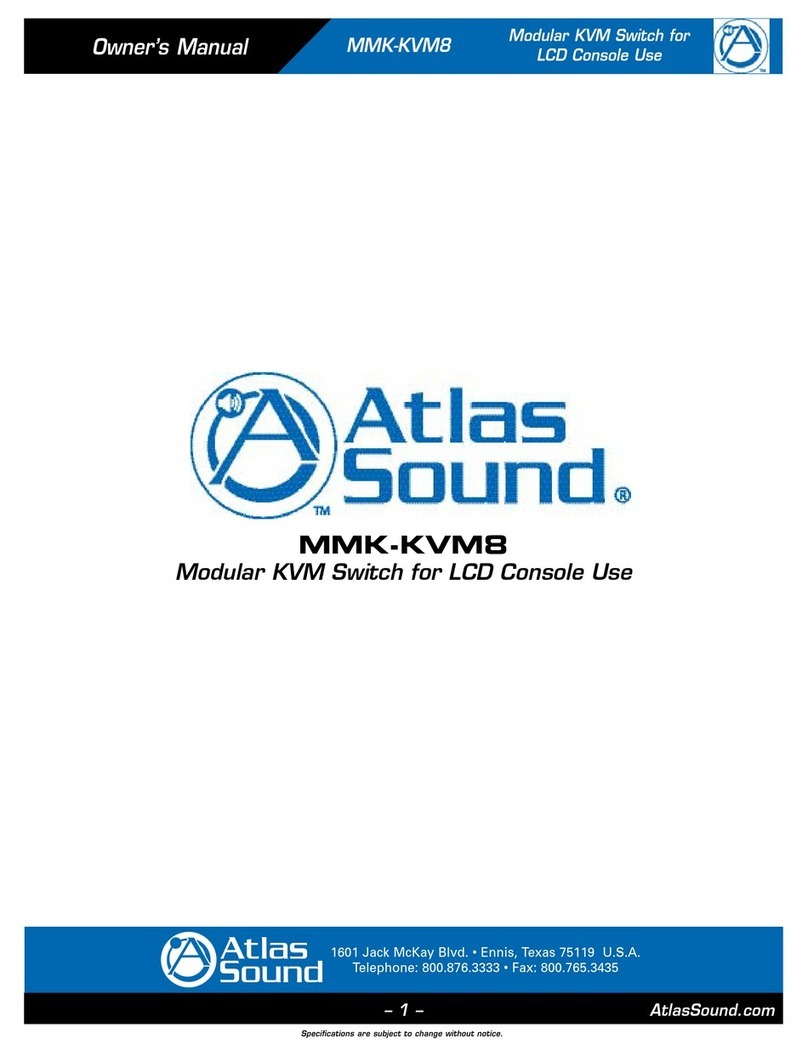

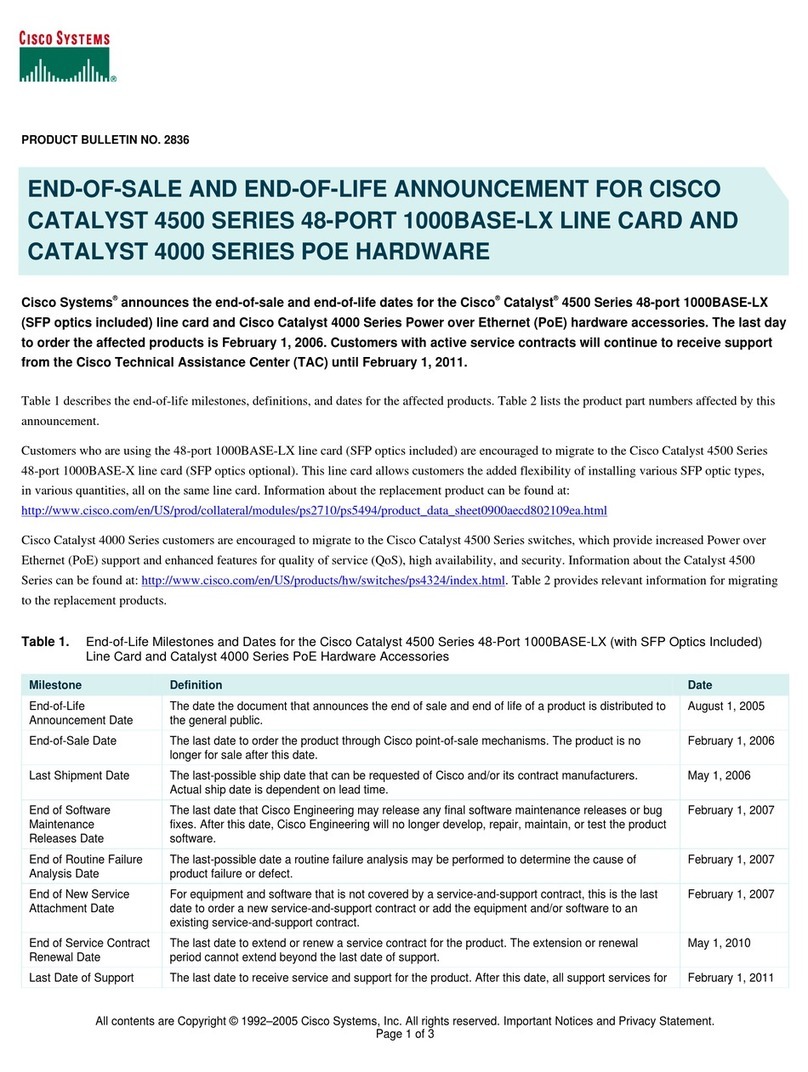

Figure 2.

Figure 2. Internal startup circuit

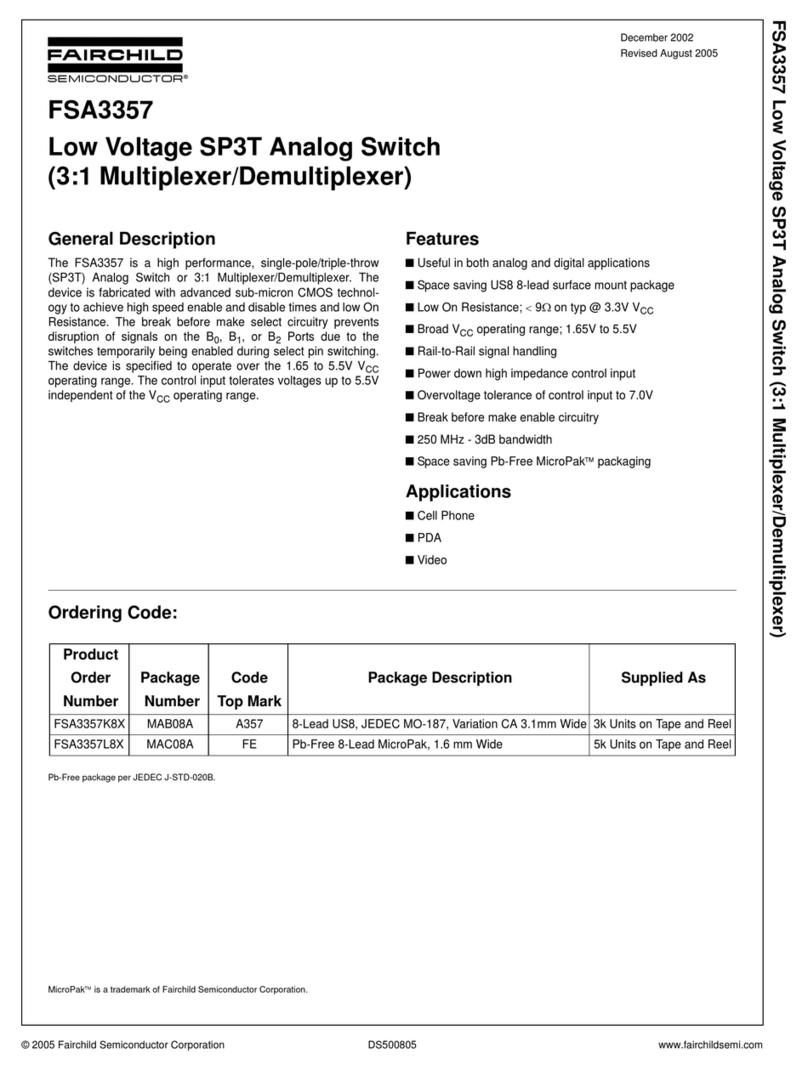

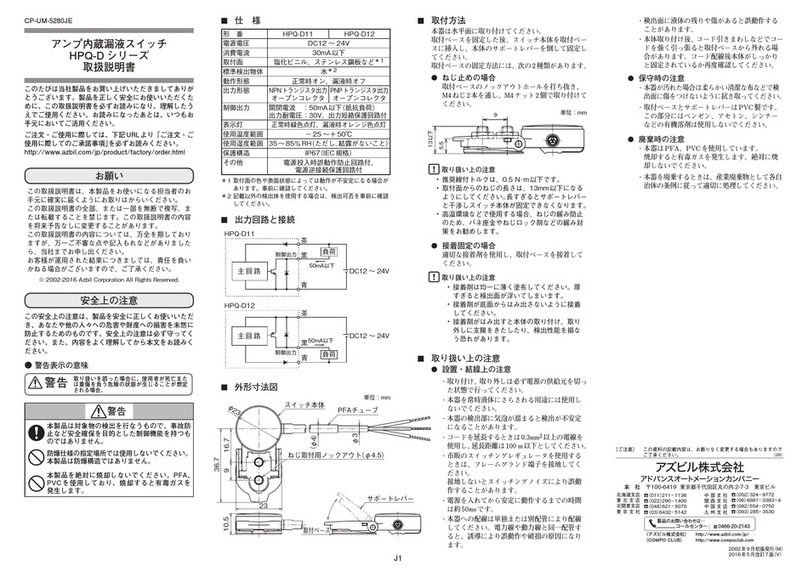

2. Feedback Control : The FSD200/210 are voltage

mode devices as shown in Figure 3. Usually, an opto-

coupler and KA431 type voltage reference are used to

implement the feedbacknetwork. The feedback voltage

is compared with an internally generated sawtooth

waveform. This directly controls the duty cycle. When

the KA431 reference pin voltage exceeds the internal

reference voltage of 2.5V, the optocoupler LED current

increase pulling down the feedback voltage and

reducing the duty cycle. This will happen when the

input voltage increases or the output load decreases.

3. Leading edge blanking (LEB) : When the MOSFET

turns on, there will usually be a large current spike

through the MOSFET. This is caused by primary side

capacitance and secondary side rectifier reverse

recovery. This could cause premature termination of

the switching pulse if it exceeded the over-current

threshold. Therefore, the FPS uses a leading edge

blanking (LEB) circuit. This circuit inhibits the pver-

current comparator for a short time after the MOSFET

is turned on.

Figure 3. PWM and feedback circuit

4. Protection Circuit : The FSD200/210 has 2 self

protection functions: over-load protection (OLP) and

thermal shutdown (TSD). Because these protection

circuits are fully integrated into the IC with no external

components, system reliability is improved without cost

increase. If either of these functions are triggered, the

FPS starts an auto-restart cycle. Once the fault

condition occurs, switching is terminated and the

MOSFET remains off. This cause Vcc to fall. When Vcc

reaches the UVLO stop voltage (6.7:FSD210,

6V:FSD200), the protection is reset and the internal

high voltage current source charges the Vcc capacitor.

When Vcc reaches the UVLO start voltage

(8.7V:FSD210, 7V:FSD200), the device attempts to

resume normal operation. If the fault condition is no

longer present start up will be successful. If it is still

present the cycle is repeated. This is shown in Figure 4.

ooooBurst function

145℃(Hys 50℃)145℃(Hys 50℃)145℃(Hys 50℃)145℃(Hys 50℃)Thermal Shutdown(typ.)

6W4W6W4W85~265VAC

Output

Power

Package Type

Operating Current (max)

Frequency Modulation

Switching Frequency

Current Limit (typ.Iover)

On-state Resistance (max)

Breakdown vol tage (min)

Product Parameter

7DIP/7SMD7DIP/7SMD7DIP/7SMD7DIP/7SMD

Without Bias WindingWith Bias Winding

770uA770uA770uA770uA

134kHz134kHz134kHz134kHz

±4kHz

0.3A

32ohm

700V

BCDMOS

FSD200

±4kHz

0.3A

32ohm

700V

BCDMOS

FSD210

±4kHz

0.48A

18ohm

700V

BCDMOS

FSD211

18ohm

±4kHz

0.48A

700V

BCDMOS

FSD201

ooooBurst function

145℃(Hys 50℃)145℃(Hys 50℃)145℃(Hys 50℃)145℃(Hys 50℃)Thermal Shutdown(typ.)

6W4W6W4W85~265VAC

Output

Power

Package Type

Operating Current (max)

Frequency Modulation

Switching Frequency

Current Limit (typ.Iover)

On-state Resistance (max)

Breakdown vol tage (min)

Product Parameter

7DIP/7SMD7DIP/7SMD7DIP/7SMD7DIP/7SMD

Without Bias WindingWith Bias Winding

770uA770uA770uA770uA

134kHz134kHz134kHz134kHz

±4kHz

0.3A

32ohm

700V

BCDMOS

FSD200

±4kHz

0.3A

32ohm

700V

BCDMOS

FSD210

±4kHz

0.48A

18ohm

700V

BCDMOS

FSD211

18ohm

±4kHz

0.48A

700V

BCDMOS

FSD201

Vin,dc

Vstr

Vcc HV

Reg.

Vin,dc

Vstr

Vcc

7V

Vcc>8.7V

off

Vcc<6.7V

on

Istr Istr

FSD21x FSD20x

4

OSC

Vcc Vref

5uA 0.25mA

VSD

R

FB Gate

driver

OLP

Vfb

KA431

Cfb

Vo