Cinterion®ALAS5 Hardware Interface Overview

1.2 Key Features at a Glance

15

ALAS5_HIO_v00.030a 2019-04-01

Confidential / Preliminary

Page 10 of 50

Interfaces

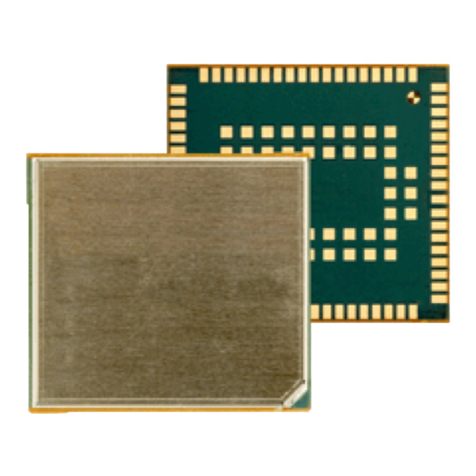

Module interface Surface mount device with solderable connection pads (SMT application

interface).

Land grid array (LGA) technology ensures high solder joint reliability and

provides the possibility to use an optional module mounting socket.

For more information on how to integrate SMT modules see also [3]. This

application note comprises chapters on module mounting and application

layout issues as well as on additional SMT application development equip-

ment.

Antenna 50. GSM/UMTS/LTE main antenna, LTE Diversity/MIMO antenna,

(active/passive) GNSS antenna

USB USB 2.0 High Speed (480Mbit/s) device interface or

USB 3.0 Super Speed (5Gbit/s) device interface

Serial interface ASC0:

• 8-wire (plus GND line) interface unbalanced, asynchronous

• Fixed baud rates from 115,200 to 921,600bps

• Supports RTS0/CTS0 hardware flow control

Linux controlled only:

ASC1:

• 4-wire, unbalanced asynchronous interface

• Fixed baud rates: 115,200bps to 921,60bps

• Supports RTS1/CTS1 hardware flow control

ASC2:

2-wire, unbalanced asynchronousinterface at RXD2 and TXD2 lines used

for tracing and debugging purposes (optional)

UICC interface 2 UICC interfaces (switchable)

Supported chip cards: UICC/SIM/USIM 2.85V, 1.8V

I2C interface 1 I2C interface

Audio 2 digital interfaces (I2S) - first DAI reserved for future use

Power on/off, Reset

Power on/off Switch-on by hardware signal IGT

Switch-off by AT command (AT^SMSO) or IGT (option)

Automatic switch-off in case of critical temperature or voltage conditions

Reset Orderly shutdown and reset by AT command

Emergency-off Emergency-off by hardware signal EMERG_OFF

Special Features

Antenna SAIC (Single Antenna Interference Cancellation) / DARP (Downlink

Advanced Receiver Performance)

Rx Diversity (receiver type 3i - 64-QAM) / MIMO

GPIO 15 I/O pins of the application interface programmable as GPIO.

GPIO1 can be configured as dead reckoning synchronization signal.

Programming can be done via AT commands.

Emergency call handling

(not for -US variant) EU eCall 3GPP Release 10 compliant (modem)

ERA compliant (modem and GNSS)

ADC inputs Analog-to-Digital Converter with four unbalanced analog inputs for (exter-

nal) antenna diagnosis

JTAG JTAG interface for debug purposes

Feature Implementation