Contents

vi

Devices on the ISA Bus. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Ultra I/O Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Audio Controller. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

System ROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Little Ben . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Other PCI and ISA Accessory Devices under Plug and Play . . . . . . . . . 20

3 Interface Boards and Mass-Storage Drives

HP Integrated OpenGL Interface Board . . . . . . . . . . . . . . . . . . . . . . . 22

Drivers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Start Up. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Video Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Available Video Resolutions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

HP PCI Integrated 10/100 BT Interface Board . . . . . . . . . . . . . . . . . . 25

Board Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Configuring the Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Further Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

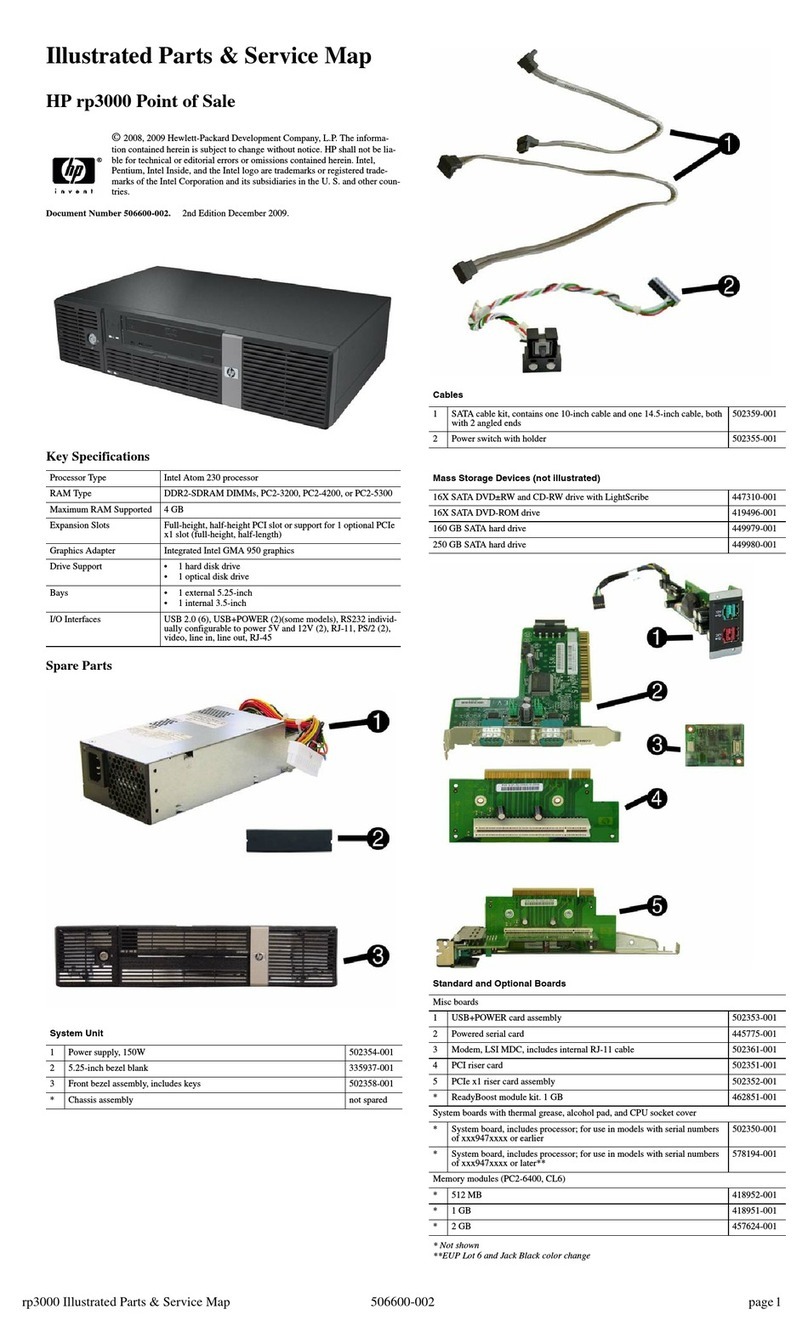

Mass-Storage Drives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Hard Disk Drives. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Flexible Disk Drives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

CD-ROM Drives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

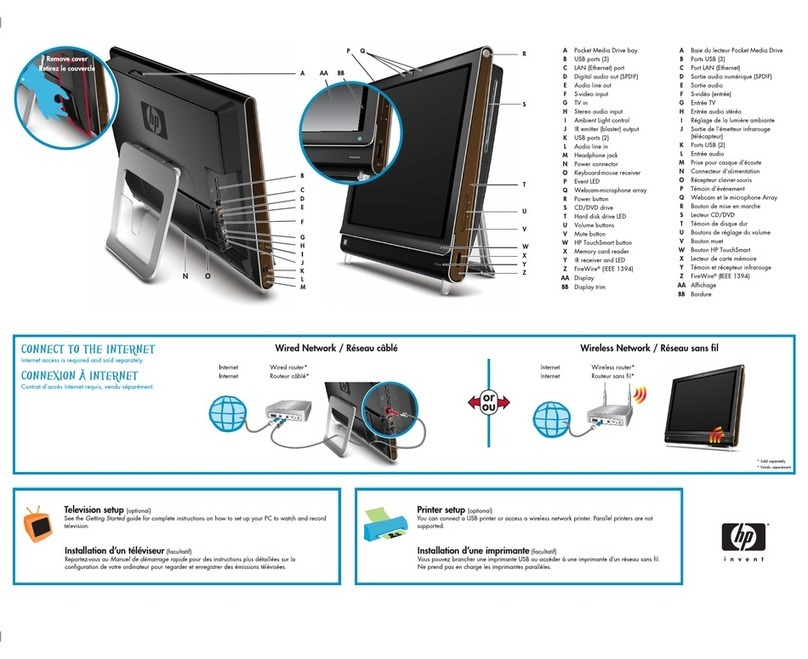

Connectors and Sockets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

4HPBIOS

Setup Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

BIOS Addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

System Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Product Identification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36