3 - 3

3-1-10 SQUELCH CIRCUIT (MAIN UNIT)

The transceiver has two squelch circuits, voice activated

squelch for J3E/H3E and S-meter squelch forA1A/FSK/J2B.

(1) AF ACTIVATED SQUELCH

A portion of the AF signal from the active low-pass filter

(IC20b) is amplified at the limiter amplifier (IC20a) and is

then applied to the one-shot multi-vibrator (IC22c, IC22d).

The one shot multi-vibrator functions as an F-V converter

which generates a signal only when audio signals are

received.

The output signals pass through the NOR gate (IC22b) and

then the 3 Hz low-pass filter (IC21a) to remove the remain-

ing noise components. The filtered signal is applied to the

window comparator (IC21b). The NOR gate (IC22b) deacti-

vates the audio activated squelch during A1A/FSK/J2B

mode operation.

The comparator outputs “High” when the integrated signals

exceed the reference voltage. C269, R310 and R780 are

used as a time constant circuit. The resulting signal output

from IC22a is inverted at Q46 and is then applied to the CPU

as the “SQLS” signal. The CPU controls the squelch gate

(IC12a) when the “SQLS” signal is received.

(2) S-METER SQUELCH

The S-meter signal from IC19b is applied to the squelch

comparator (IC19a) to close or open the squelch circuit. The

reference voltage is adjusted by R257 and then applied to

the (–) terminal of the comparator (IC19a). When the S-

meter signal exceeds the reference voltage, the comparator

outputs “High” to the CPU via IC22a and Q46 in the same

manner as the voice activated squelch circuit.

3-2 TRANSMITTER CIRCUITS

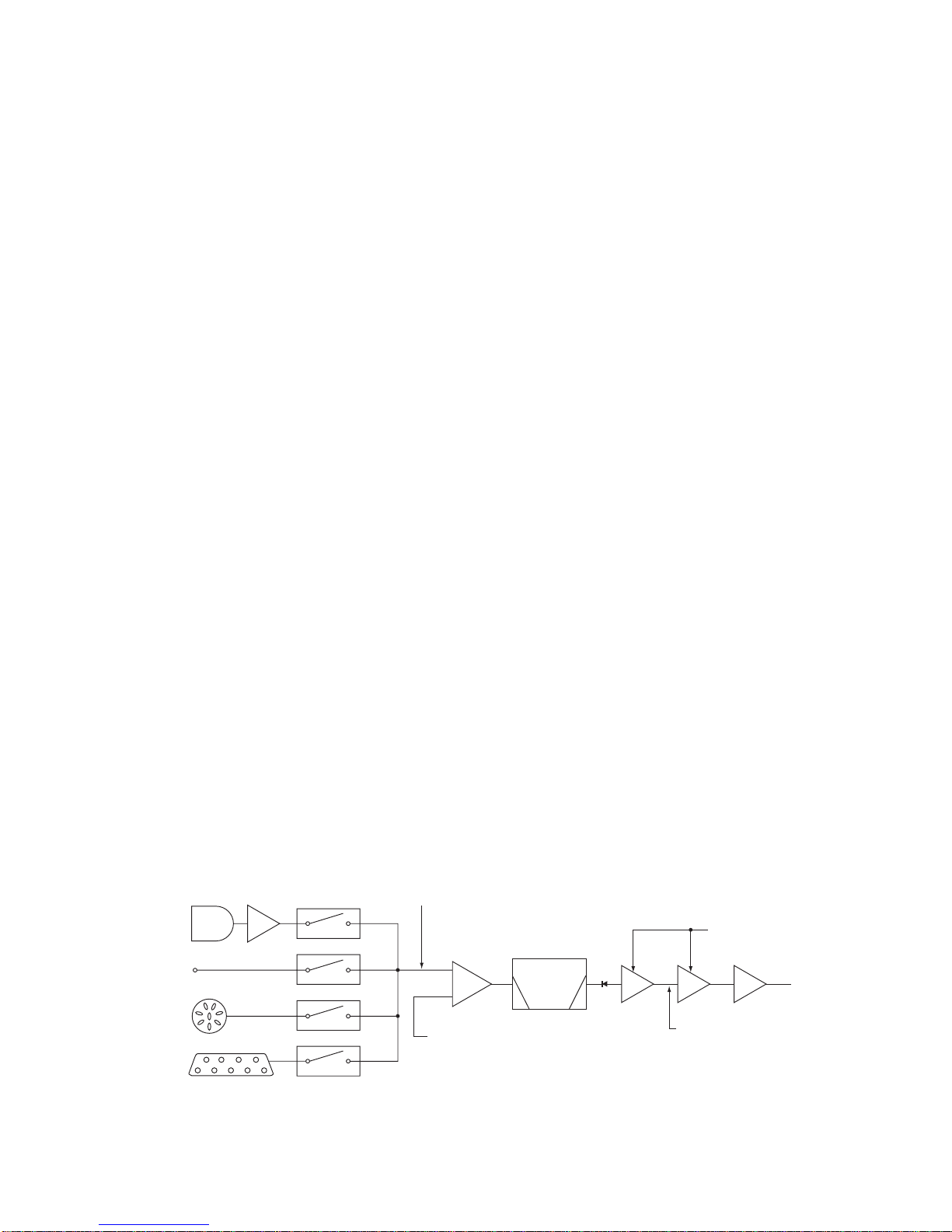

3-2-1 MICROPHONE AMPLIFIER CIRCUIT

(LOGIC BOARD IN THE RC-21)

The AF signals from the [MICROPHONE] connector pass

through the microphone gain controller (R81) and AF ampli-

fier (IC12a), and are applied to the CTRL1 board. The

microphone AGC circuit (D9, D10, Q13, Q14) controls the

amplifier gain to prevent signal distortion.

The AF signals are converted into PWM signal at the PWM

modulation circuit (IC3, Q1, D1) via the AF amplifier (CTRL1

board; IC4), and are applied to the serial interface IC (IC1).

The serial interface IC outputs PWM signal to the CTRL2

board (IC-M710 RT) via a coaxial cable.

The PWM signal from the RC-21 (controller) is applied to the

MAIN unit after being converted into an analog signal by

passing though the serial interface IC on the CTRL2 board.

TheAF signals are applied to the balanced modulator (MAIN

unit; IC9, pin 1) via the AF switch (IC38b).

External modulation inputs from the ACC socket or a 2-tone

emergency signal from the CPU are applied to the balanced

modulator directly via AF switches (IC38, IC39).

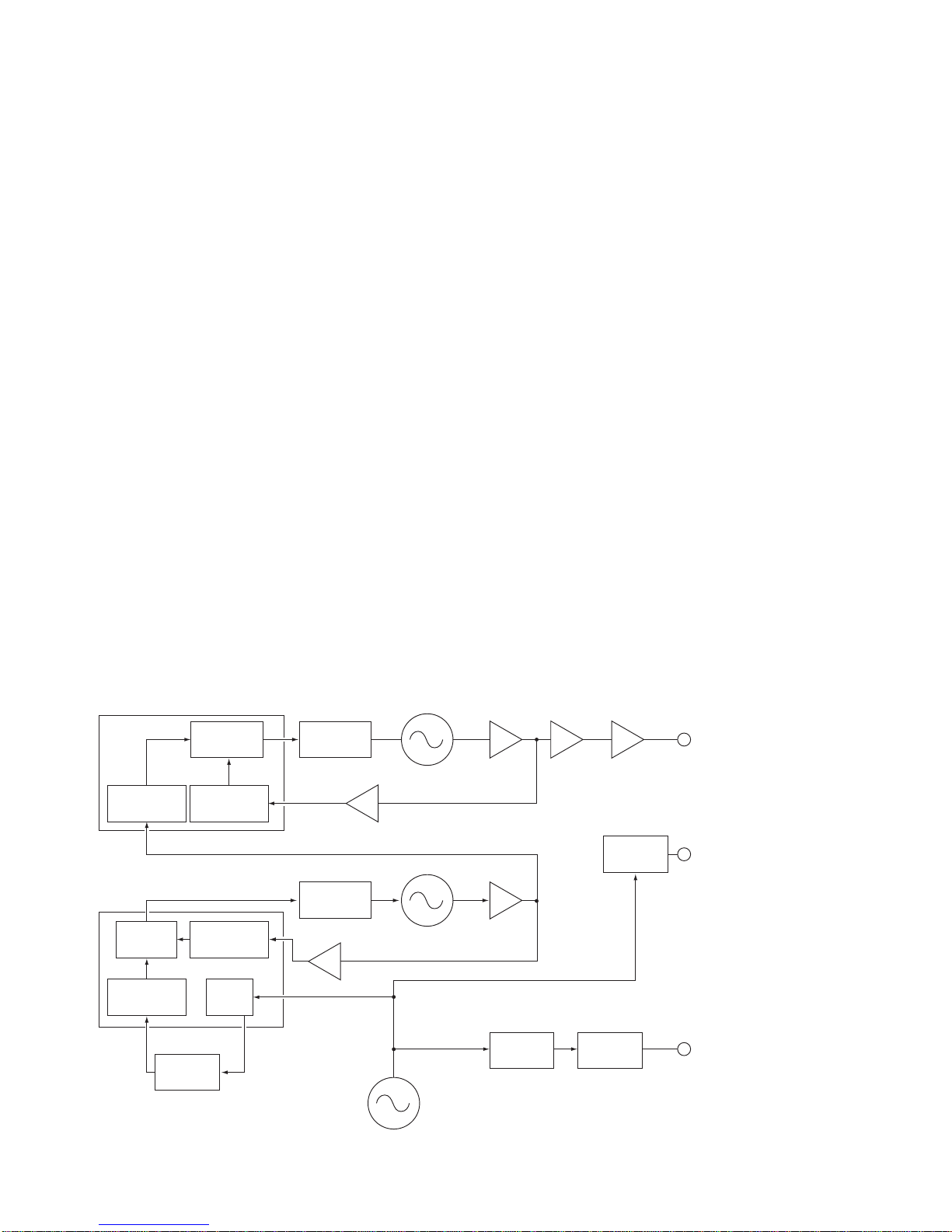

3-2-2 MODULATION CIRCUIT (MAIN UNIT)

(1) J3E AND J2B MODES

The balanced modulator is used for J3E and J2B modes to

add the audio signal to the BFO frequency and outputs the

IF signal while suppressing the BFO signal.

The AF signals from the microphone amplifier or external

audio from the modulation terminals are applied to the bal-

anced modulator (IC9, pin 1). The BFO signal from the PLL

unit is applied to IC9 (pin 10) as a carrier signal. A double

sideband signal is output from IC9 (pin 6) and is then applied

to the 9 MHz filter (FI2) to create an SSB signal.

R238 adjusts the balanced level of IC9 for maximum carrier

suppression. In J2B mode, the BFO frequency is shifted 1.7

kHz to set the transmit frequency the same as the displayed

frequency.

The SSB signal from FI2 is amplified at the 9 MHz amplifiers

(Q17–Q19) and is then applied to the mixer circuit (D52).

The switching diode (D19) is turned ON when R8 voltage

disappears.

(2) H3E AND R3E MODES

An SSB signal is applied to the IF amplifier (Q18) in the

same manner as with J3E/J2B mode. The BFO signal from

the PLL unit is amplified at the buffer amplifier (Q30) and is

then applied to the IF amplifier (Q18) as a carrier signal to

be added to an SSB signal. R211 and R212 adjust the car-

rier levels in H3E and R3E modes, respectively.