9

ICS1890

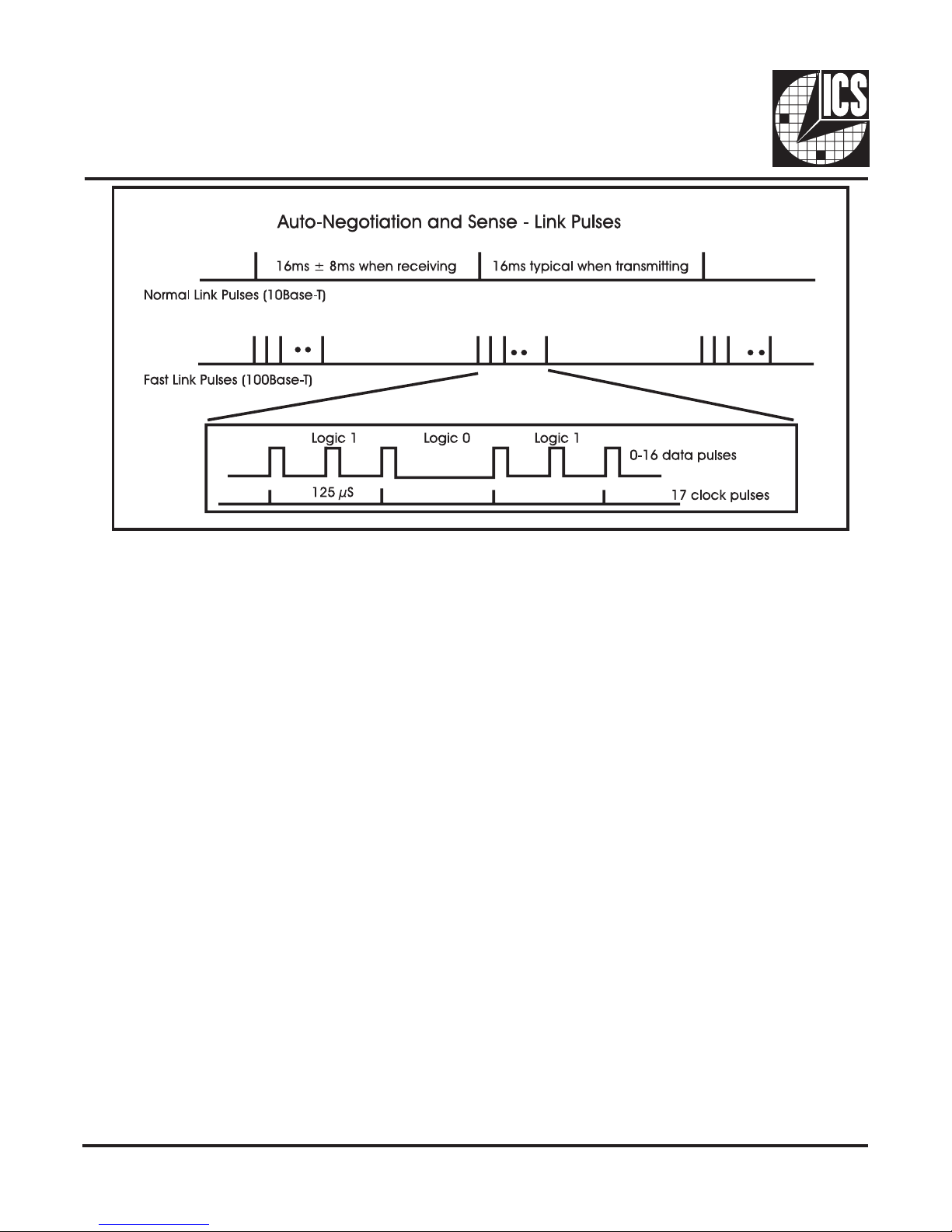

In the event that the link partner does not support auto-

negotiation, backward compatibility is guaranteed because

legacy systems will not respond to the burst (called Fast Link

Pulses). 10Base-T systems will continue to send 10Base-T

link test pulses which will be interpreted by the ICS1890 as

a 10Base-T technology only device. 100Base-TX systems

would send scrambled idle symbols, which would be interpreted

by theICS1890as a 100Base-TX only device. Auto-negotiation

is invoked at power-up, upon request by management, or

manually.

Auto-Negotiation Progress Monitor

Under normal circumstances, Auto-Negotiation is able to

effortlessly establish a connection with the link partner. There

are, however, some situations that may prevent Auto-

Negotiation from completing properly. TheAuto-Negotiation

Progress Monitor is designed to provide detailed information

to a station management entity to assist it in making a connection

in the event that Auto-Negotiation is unable to establish a

connection by itself.

During normal Auto-Negotiation operation, the device ex-

changes capability information with its link partner and then

sets the Auto-Negotiation Complete bit in the Status register

(1:5) (also available in the QuickPoll register as bit 17:4) to a

logicone toindicate thatthe informationexchange hascompleted

successfully and that Auto-Negotiation has handed off the

link startup process to the negotiated technology.

Auto-Negotiation can also accommodate legacy 10Base-T

and100Base-TX linkpartners thatdo nothave Auto-Negotiation

capability. In this case, Auto-Negotiation identifies the link

partner as not being Auto-Negotiation able by setting the

LP_AutoNeg_Able bit (6:0) to a logic zero, identifies the

legacy connection to be made by setting the single bit

corresponding to that technology in the AN Link Partner

Abilities Register (either bit 5:7 or 5:5), and finally indicates

Auto-Negotiation Complete.

The entire process, in either case, usually takes less than half

a second to complete. Typically, management will poll the

Auto-Negotiation Complete bit and then the Link Status bit to

determine when a connection has been successfully made

and then the actual type of connection can be determined by

management. This information is all contained in the QuickPoll

register.

When Auto-Negotiation fails, Auto-Negotiation Complete may

never become true or Link Status may never become good.

Station management can detect this condition and discover

why there is a failure to connect by using the detailed information

provided by the Auto-Negotiation Progress Monitor.

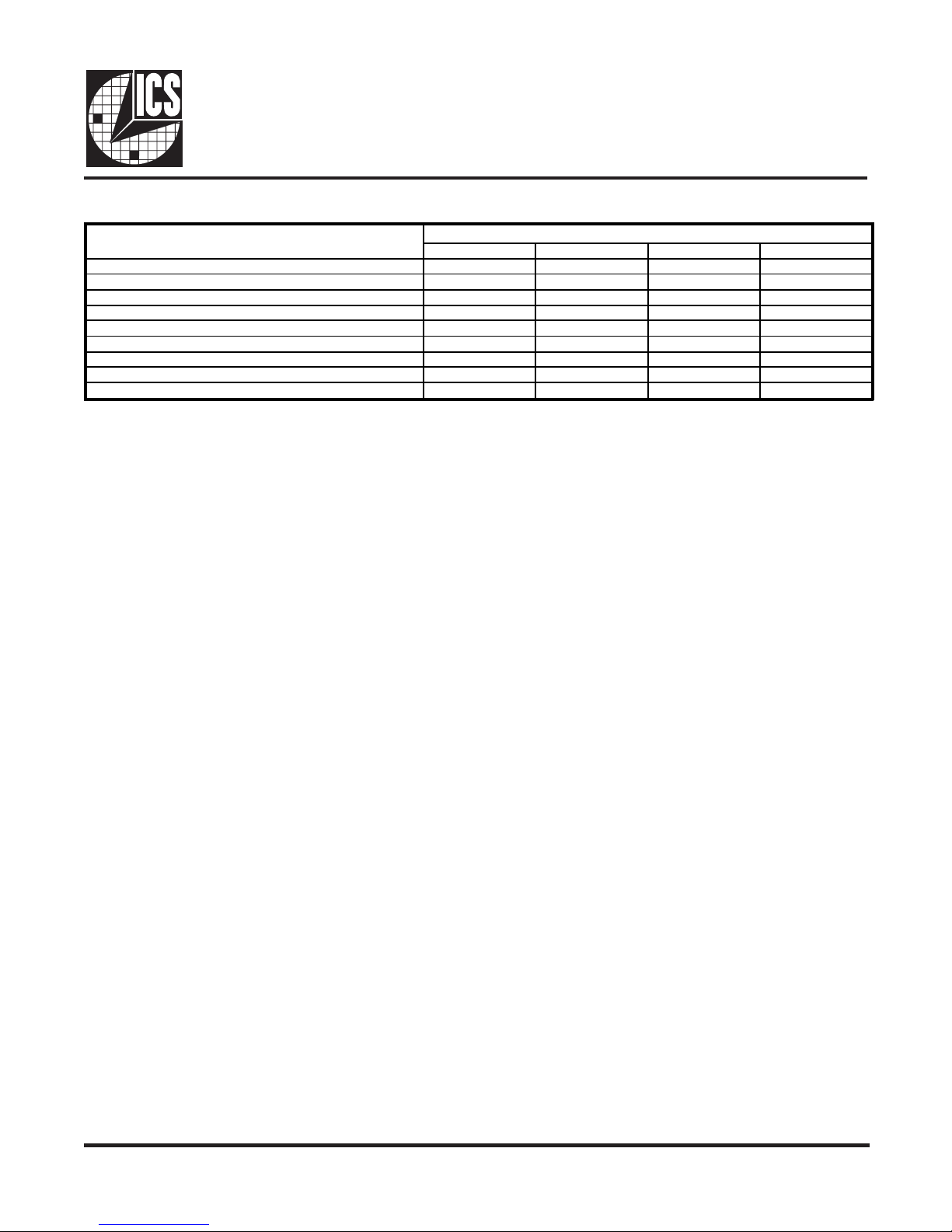

The Auto-Negotiation Progress Monitor provides four bits of

status in the QuickPoll Detailed Status register when combined

with the already present Auto-Negotiation Complete bit.

As progress is made through the Auto-Negotiation Arbitration

state machine, higher status values are locked in to the progress

monitor. The status value only is allowed to increase until

either Auto-Negotiation is completed successfully or the

progress monitor status is read by management.

After the status is read by management, the status is reset to

the current status of the Arbitration state machine. After

negotiation has completed successfully, any link failure will

cause the process to being anew.

This behavior allows management to always determine the

greatest forward progress made by the Auto-Negotiation logic.

Status Progress Monitor Status Bits

A-N Complete Bit 2 Bit 1 Bit 0

Idle 0000

Parallel Detected 0 0 0 1

Parallel Detection Failure 0 0 1 0

Ability Matched 0 0 1 1

Acknowledge Match Failure 0 1 0 0

Acknowledge Matched 0 1 0 1

Consistency Match Failure 0 1 1 0

Consistency Matched 0 1 1 1

Auto-Negotiation Completed Successfully 1 1 1 1