Industrial Micro Systems 464 User manual

'-

>

INDUSTRIAL

MICRO

SYSTEMS.

INC.

MODEL

464

64K

DYNAMIC RANDOM

ACCESS

MEMORY BOARD

***********************************.****************************************.*.

•2MHZ OR 4MHZ OPERATION •

8080

OR

Z80

OPERATION

•PARITY

CIRCUITRY

•

HIDDEN

REFRESH

(Ml

CYCLE)

•PHANTOM LINE

(pIN

67)

•

NO

WAIT

STATES

0•BANK

SELECT

LOGIC •

LOW

POWER

CONSUMPTION

V•FRONT PANEL COMPATIBLE

.6A

+8

VOLTS

•SELECTABLE PORT

ADDRESS

.ZA

+16

VOLTS

'---"

•

AVAILABLE

IN

HK.

48K.

OR

64K

.001A

-

-16

VOLTS

MOOELS

"-'

"

"-

GENERAL

PESCRIPTION

The

Model

464

Dynamic

Ram

Memory

Board

is

fully

buffered

and

uses 16K X 1

bit

dynamic memory

circuits.

The

boards

are

tested

and

burned

in

at

70

degrees

centigrade

under

diagnostic

test

to

insure

reliable

operarions.

The

464

board

may

be

ordered

as a

32K,

48K,

or

64K

memory

board.

In

each

of

these

configurations,

the

memory is

organized

into

16K

byte

banks.

Two

modes

of

operation

are

provided,

Normal Mode and Bank Mode.

In

the

normal

mode,

the

16K

byte

banks

occupy

contiguous

address space.

In

the

bank

mode

of

op~ation,

the

board

is

initially

disabled

and

each

16K

byte

bank

may

be

mapped

into

selected

quadrants

of

memory (see Bank

Selection),

The

464

board

provides

a

"Phantom

Line"

input

for

systems

with

ROM

memories which

utilize

this

feature.

The

user

may also

configure

the

board

to

accept

the

front

panel

deposit

signal,

M-WRITE.

\

INDUSTRIAL

MICRO

SYSTEMS.

INC.

D00464

REV A

8/12/80

Page

1

of

6

·--

The

464

board

features

a

parity

circuit

to

provide

increased

data

security.

A

parity

bit

is

written

during

every memory

write

such

that

the

total

number

of

"1"

bits

written

are

odd.

During

memory

reads

the

total

number

of

"1"

bits

are checked.

The

parity

error

is

set

if

the

number

of

"1"

bits

checked

are

even,

Parity

errors

during

memory reads

can

interrupt

or

stop

the

CPU. ALED

r-

indicator

on

the

board

is

lighted

to

indicate

the

error,

The

status

of

the

parity

circuit

may

be

read

J

from

the

memory

board's

I/O

Port.

CONFIGURING

THE

464

BOARD

PHANTOM LINE OACK JO)

The

phantom

signal

(pin

67)

shunt

is

etched

so

that

the

board

will

be

disabled

by

an

activated

Phantom

Line.

1£

this

is

not

desirable,

then

the

etch

connecting

the

two

pads

of

JD (PH) may

be

cut

on

the

rear

of

the

board.

aD

must

be

connected

when

using

the

464

board

with

Industrial

Micro

System

CPU

boards,)

Note:

The

Phantom

Line

affects

memory

read

operations

only.

Memory

write

operations

are

not

affected

by

the

Phantom

Line. . ,

EN

I/O

OACK JB)

-...J

THE

"EN

I/O"

(Enable I/O)

shunt

JB

must

be

installed

for

the

board

to

respond

to

I/O

commands.

This

will

be necessary

for

bank

mode

or

parity

operations.

I/O

SELECTION

OACK

JC)

The

selection

of

the

boards

I/O

address

is

done

on

jack

JC.

The

jack

is

labeled

0-7

(top

to

bottom)

for

the

respective

address

bits

(AO-A7)

of

the

I/O

address.

A

"1"

is

programmed

by remoyin¥ a

shunt.

Thus,

to

program

I/O

address

OFH

the

top

four

shunts

(0-3)

would

be

removed

("l's")

and

.J

the

bottom

four

shunts

(4-7)

would

be

installed

("O's"),

(Note

that

the

liEN

1/0"

shunt

must

be

on

for

the

board

to

respond

to

the

I/O

command.)

CPU

SELECTION

OACK

JF)

,i

The

8080

shunt

(JF)

should

be

installed

for

systems

using

8080

CPU's.

For

2-80

systems

this

shunt

should

be

removed.

FRONT

PANEL OACK JH)

If

the

464

board

is

to

be

used

with

an

"IMSAI"

front

panel,

the

shunt

JH

must

be

in

the

right-most

(FP)

position.

MEMORY

SPEED

OACK JA)

The

JA

shunt

controls

the

timing

of

the

memory

board.

The

H

position

is

for

200NS

RAMS

and

the

L

position

is

for

250NS

RAMS.

This

shunt

is

factory

installed

on

the

H

position

and normally

should

not

be

changed.

High

speed

operation

is

required

for

the

2-80

processor.

INDUSTRIAL

MICRO

SYSTEMS.

INC.

000464

REV A

8/12/80

Page

2

of

6

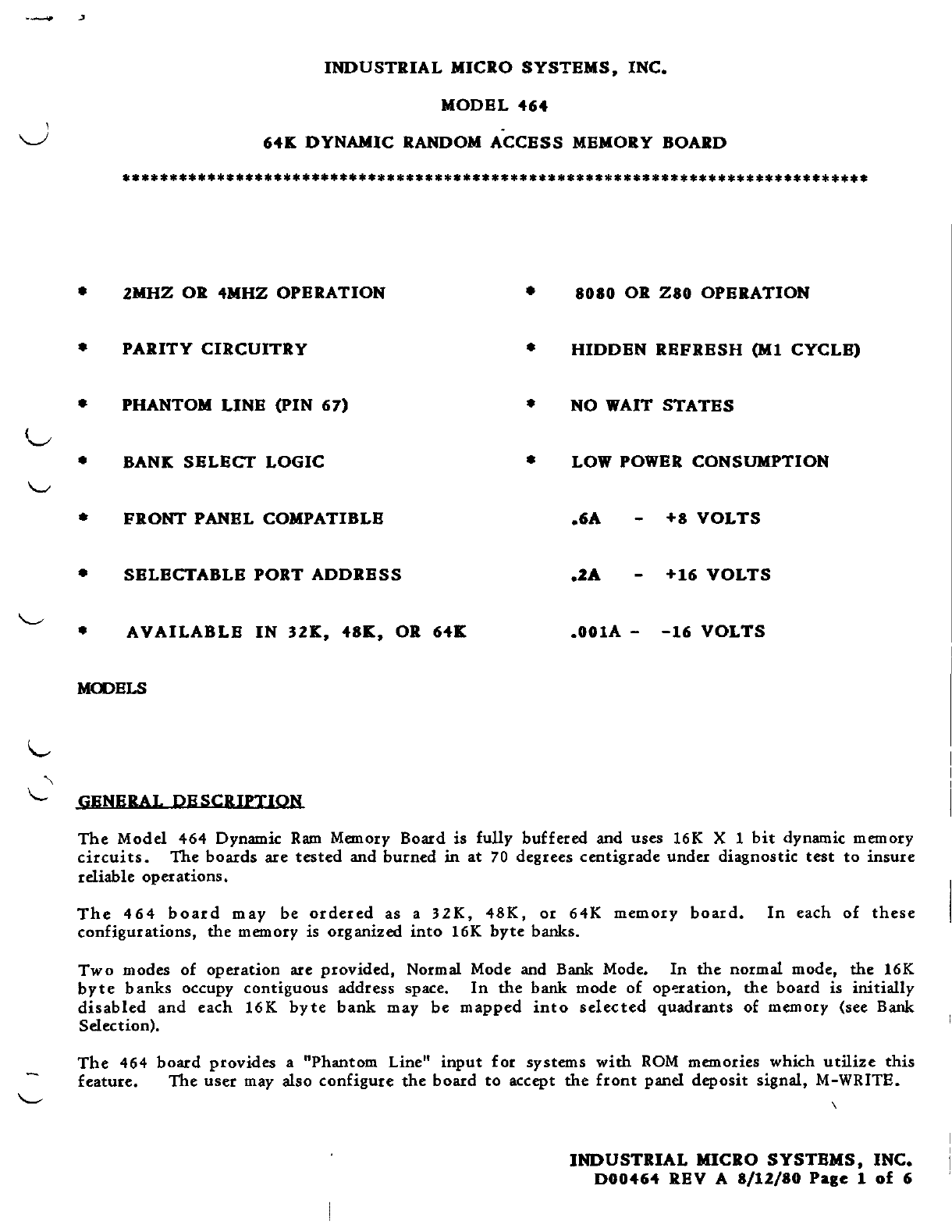

PARITY

INTERRUPT

OACK

JG)

Jack

JG

allows

selection

of

eight

different

responses

to

a

parity

error.

The

selections

are:

SHUNT

POSITION

VIl

VI2

VB

VI4

VI5

INT

NMI

RDY

S100 BUS PIN NO.

05

06

07

08

09

73

12

72

INTERRUPT

SELECTEp

VECTORED INTERRUPT 1

VECTORED INTERRUPT 2

VECTORED INTERRUPT 3

VECTORED INTERRUPT 4

VECTORED INTERRUPT 5

PINT Line

Non-maskable

INT

(Z-80

only)

PRDY Line (Parity

Error

Stops

CPU)

When

using

the

parity

error

circuit,

the

user

must

initially

write

into

all memory

locations

after

power

is

initially

applied

to

condition

all

the

parity

bits.

After

the

memory

is

initialized,

the

parity

error

circuit

must

be

reset.

The

parity

error

circuit

is

reset

by any

output

to

the

I/O

port

on

the

memory

board.

The

Power

On

Clear

signal

(POC

Pin

99

on

S100

bus)

also

resets

the

parity

error

circuit.

The

state

of

the

parity

circuit

may be sensed

by

reading

bit

"0"

of

the

I/O

port

on

the

memory

board.

A

"1"

bit

indicates

a

parity

error

has

occurred.

NORMAL/BANK

MODE

OACK

JE)

The

"bank"

mode

shunt

should

be

installed

only

if

the

board

is

to

be

used

in

the

Bank

Switched

mode.

In

this

mode

the

board

will

respond

to

all addresses

from

0000

to

FFFF

hex.

For

memories

that

are

to

be

bank selected,

this

shunt

should

be

installed.

NORMAL MODE

In

the

normal mode,

shunt

JE removed,

the

four

16K memory banks occupy

the

entire

16

bit

address

space

0000

thru

FFFF

hex.

In

this

mode, each 16K

bank

may be

controlled

individually

by an

output

to

the

board's

I/O

Port.

A

"one"

bit

disables

the

associated

bank.

Control

is

on a

bit

basis,

thus:

OUTPUT

DATA

CONTROLLED

MEMORY

BANK

(HEX)

BANK

MOPE

BIT

0

BIT

1

BIT 2

BIT

3

0000-3FFF

4000-7FFF

8000-BFFF

COOO-FFFF

(omitted

in

32K version)

(omitted

in

32K &48K

version)

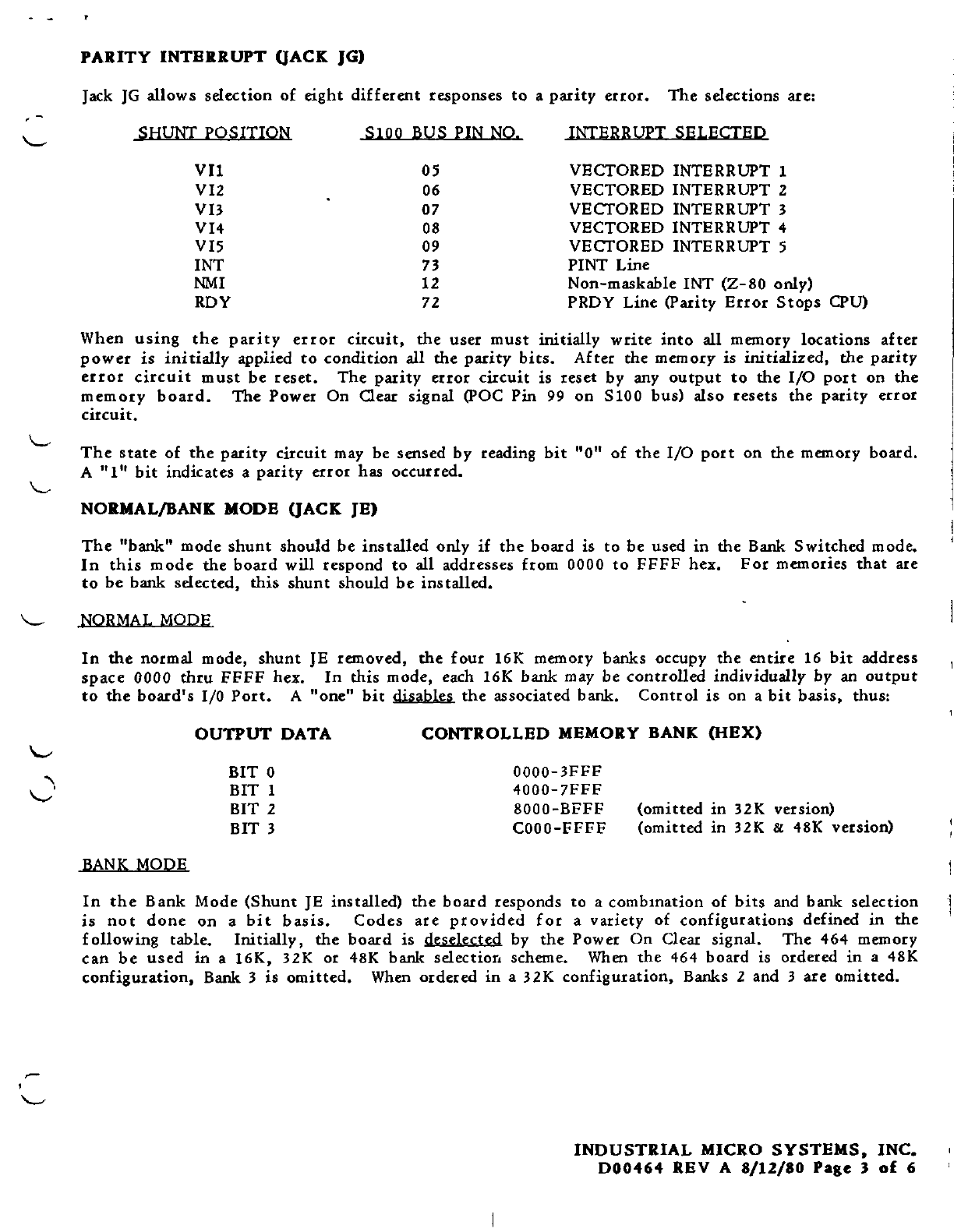

In

the

Bank

Mode

(Shunt

JE installed)

the

board

responds ro a

combmation

of

bits

and

bank

selection

is

not

done

on

a

bit

basis.

Codes

are

provided

for

a

variety

of

configurations

defined

in

the

following

table.

Initially,

the

board

is

deselected

by

the

Power

On

Clear signal.

The

464

memory

can

be

used

in

a

16K,

32K or 48K

bank

selection

scheme. When

the

464

board

is ordered

in

a48K

configuration,

Bank 3

is

omitted.

When

ordered

in

a32K

configuration,

Banks 2

and

3

are

omitted.

INDUSTRIAL

MICRO

SYSTEMS,

INC.

000464

REV

A

8/12/80

Page

3

of

6

BANK MODE TABLE

OUTPUT

DATA

o

1

2

3

4

5

6

7

8

9

A

B

C

D

B

F

MEMORY MAPPING

All

Banks

Deselected

Banks

0&1

Occupy

Addresses

Banks

2&3

Occupy

Addresses

Banks

0,

1, &2Occupy

Addresses

Banks 0&1

Occupy

Addresses

Banks

2&3Occupy

Addresses

Bank

0Occupies Addresses

Bank

0

Occupies

Addresses

Bank

1Occupies Addresses

Bank

1Occupies

Addresses

Bank

2Occupies Addresses

Bank 3Occupies

Addresses

Bank

2Occupies

Addresses

Bank 3Occupies

Addresses

Bank

3Occupies

Addresses

Bank 3

Occupies

Addresses

8000-FFFF

(32K)

8000-FFFF

(32K)

OOOO-BFFF (48K)

0000-7FFF

(32K)

0000-7FFF

(32K)

COOO-FFFF (16K)

0000-3FFF

(l6K)

0000-3FFF

(l6K)

COOO-FFFF (16K)

0000-3FFF

(l6K)

0000-3FFF

(l6K)

COOO-FFFF (16K)

4000-7FFF

(l6K)

8000-BFFF

(l6K)

COOO-FFFF

(l6K)

.-

J

STANDARD CONFIGURATION

IMS

supplies

the

464

board

configured

as

follows:

JACK

DESCRIPTION

STANDARD

CONFIGURATION

JA Memory

Speed

H

Position

Shunted

JB

En

I/O

Open

JC

I/O

Selection

All

Positions

Shunted

JD

Phantom

Line

Shunted

(E

tch)

JB

Normal/Bank Mode

Open

JF

CPU

Selection

Open

JG

Parity

Interrupt

All

Open

JH

Front

Panel

Left

Position

Shunted

.,

Four

spare

shunts

are

installed

on

the

upper

pins

of

Jack

G.

These

pins

are

all

connected

by

etch

and

serve

as a

convenient

place

to

store

spare

shunts.

Note:

464

boards

shipped

in

systems

will

normally

be

configured

to

the

system requirements.

INDUSTRIAL

MICRO

SYSTEMS

INC.

000464

REV A

8/12/80

Page

4

of

6

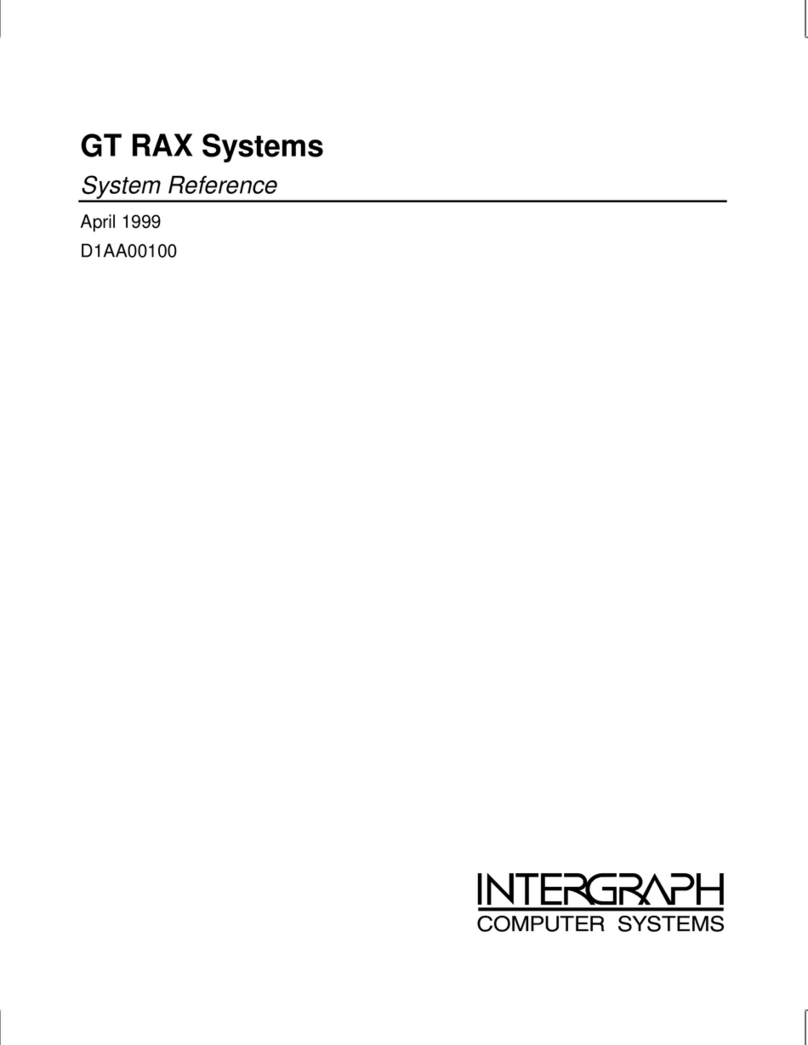

RAS2

RASl

BANK

RAS3

RAsa

AM

S.

INC.

D00464

REV

A

8/12/80

Pale

5

of

6

'7

ADDR

I--

A

MXPR

BANK

RAS3

R

SELECT

I--

A

14J

LOGIC

RAS2

04K

X 9

R

MEMORY

ARRAY

I---- A

RASI

R

'--

A

RASa R

PARITY

GEN

8

DATA

DIN

,

OUT

8

BUFFER D

OUT

8

"8

DATA

8

PARITY

IN

'-

,

CHECKER

BUFFER

I

}'4

~E.

P,

E.

1-

~

BANK

BOARD

F/F

\J

~

SELECT

SELECT

LATCH 4

LOGIC

JD -

0-

VI1

OM

0-

VI2

BIN

r.IK

(J

E)

0-

VI3

0-

VI4

D

\.8

0-

VI5

Pia

00

0-

INT

\.

LOGIC

UT

0-

NMI

WR

0S,Jc)

0-

RDY

JG

MR

MEMORY

M1

START

01

AND

02

TIMING

NC

LOGIC

WR

(IN)

BLOCK

DIAGR

UT

07

(JA)

AIT

(JF)

INDUSTRIAL

MICRO

SYSTEM

A

07-

SO

P

Dr

DO

ME

PSY

P

S0

D

PW

PHANT

D

AD

(13-00)

AI5

AI4

RFSH

v

~

c:

16

IS

o

CO,nIGM'

19ft

14

'0

I.

o0

0,:

0

0'90;9

I

I.

I/O

~

-e=J-

Jt

r--l

I'

"

'~'O

00

19

JUMKI

JfO

lOla

"o

~iO-GJ

o

ON

SEE

PG.2

I I

SEE

PG

2

'--SEE

PG

2

SEE

PG.

2

2J

SEE

PG.

2I

SEE

PG.3

I

lOP

to7

10.

lOt

10.

In

102

ID1

1009

10

"

,,"~~

~~~

7'~

.,=,

~ ~

7',.-.

0

E::::J-

~~'~

-~

~

_~

~

_~

~

-ld

u

__

"

'O~:,u

UUUUUU0

'~

l.,-.,.....JU~

-

=>-

-=- -=>- -=- -=-

-=-

_=-

-=-

_::>-

C35

o~

~D

00000000

~j

O~

-=-

-=>-

-0-

-=>- -=- -

::>-

-=-

-::l-

-=-

W

;Ir~

!13

000000000

CU~

I 2 2 4 S 6 7 • 9

C" P

~

9

fI

~

I

~f

~~

~

IHDUITIIAL

MICIO

.,nIMS

JG

a

31

,.

n

7.

cS

COO""

JH

QC

MAD.

IN

U.I.A

,

:_~

Zi

~

0LIt

Q

en.

>» _ •

_1

'0

...

..,

:'"

l<l

):

SEE

PG.2

t%lt""

<s::

>(:;

col<l

';:::0

N

CIl

";;000<

ClCll

"'..,

..

ttl

"3:

n

CIl

",.

o...

... 2:

",["I

(

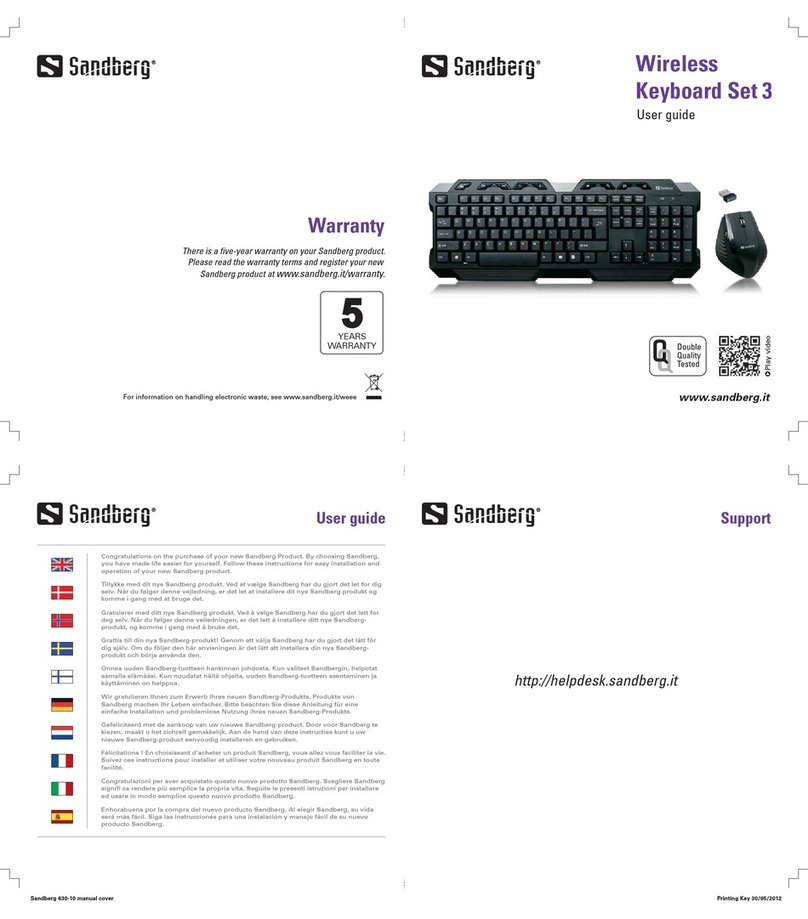

MODEL

464

STRAPPING

OPTION

LOCATIONS

(.'

( ( l

~/

(

•

~

•

"j"wa"FU"S-

ORAwN.V

gQ

W'

BS

0UT+

W£+

pw£+

T+

STEMS

1<+

...

+

L00464A

"(

\

~-----------<

(

(\

(

--

140

~I,A

14.

...

45

I 2 7

2u~Qk

WE-

"

--

1<CL-

13·

14-

1:

9"

vee

...

S

74 I10 I

IN

iTL

DElAY

LilJt:.

3

",I,.;

7

.!$&

VCt

'

1;50

tloO

"t150 "t2CO t2S,

~

"410

"I

B

13A

-=-

77

JA

HIL

:fH

156

12A

I:

~

4-

.~

9

,-----p-;t-

,+@

-;-

,:-p

~)O I8z

Q7~

5

0"'''NE-

~o

~

~

4

2~

-i

c

"il

MEM

-<.1£t

~

I

T50

CLI

TIOC

+S

140

8

f?:

,.

4-

15D

~I-t'

25

=

STA

~

I5

20

I.

6

624~

9~

1 /

A+

U-

S

0"-

'0

~/56

140 I

~

..

1I~9

~J

Q'

MeEAO-

II<+@-

1'--:--

V

~~

74

Ii

G

140

NI<.

I+~~S

~

13

J"F

RFSH-

~+

24

liD

~

Z1413

=

41&£

+s

8080

liD

13

~

02

1

2

00"\.1I

2.

prz

--

34

/S'c

3

12

'0

I

00

~74

12

p~

9

---....J?~

LV-

74

~

~

GQ

"12-

2

"I

5

IcAS

CL

~

"

P,7

4

~

J74

"'"

I90

_.

----2. QG

ICA'S'

CL

"

+S

~

v

+5

TJ50+

'3

I'

4,7K

-

1+

5

~

11

04

r

~2

+5

".

CSo

16

B

'>

IOooP':

C-

'"

"

S;~'--

rll4

!6D

/5C

,S

21G

C

II

D

~~

+5

..

A

JO~

.J±!2.

4=I •

/23

bJ

~

00)8

I'

PO

1~3

_.-132

6

~

74

[1+

27

~

V

~

CL

II

GiS

T'

CL

INDUSTRIAL

MICRO

SY:

"

+5"

.~

..

u:

I\JO\..I

E ,

........

~

av, f

16e

+s

_~

10-28-80

I

III

i

--

"

14

10

64K

DYNAMIC

RAM

I

SM

-Pip

¢

WA

PHL

PH¢

Pp¢>

5M£

5'1'UT

e07+

PWll-

PSYNC

MW~IT,

,.,...

_offtII_IIO'_.~

....

,

........

T50+

\3_

15

A1

1~1

DO'

II

RAS3-

ICAS-

04'"

JE

1

~~

~

~BANK

Z

AS

Z3

I

1100

J

RASl-

30,,373

Do

23M

121

10

A\5+

32

,.c

Jl-l+

B~

1Li

D,

O.

15 I

+5

4

A,

!l!8

5

A1>+<@

13

lZ

61'113+

~1Kt

'7

AZ

4l

00

J

<D

R~SI-

D;

a,

\1

4

D.

5

(;,

I'll

I2lZ

A

12+

33

Q,

6~11.+

\0

IDA

All+<@

18

DQ1

1~

BA11+

~

1'10

10_

18

Al0

31

17

D"

Q.

1<0

BA\O+

,12

CEO

01

Il

:3l

00

RASo-

A9+

3~

1

D,

G,

<0

BPl.9+

+5

~

CE1

'---~

AB+@

8 D a,

~

BA8+

I3B

%1-01

IcC

,

~.lK

,~

,!!

LE

OlE

e>

\5

A1

Il

~

WO

JO

1Ab 01

BDSEL+

(PH)

P"~NTOM-

'01

2

~5

D01+~

GIt244r.l'1..

~BD1+

3

~4

~

A3

DIl>0+

40

4L(ii,

~BOIO+

1Fl2

01215+

:J 8

Is

0,

~BD5+

<;;

AI

DI2I4+~

15

~BD'H

1,

0.

5

flO

11

~

BO,.

5D,nsQ(7

D12I3+

8~

~;

0,

,12

CEQ

D02~

\~

1...5

(iI. 1

BD'2+

12

D,

Q,

10

~

eel

D0H-

35

11

I1

~7

3BD1+-

~

Do

Go 2'l<01-OZ 13C

00

3b 2lr--

~Q

1'21

BDO+13 D303

15

,,=-"

~

~

1~

1'1.0

.---=

OK

CL

130 q

+5

\1

~

1510

'I

<0

D~EN-

W83f

PWR+

9

IO

l~A

10~15D

ADDR+

10WT-

PP.0C-~

PPPC--

~lEMR+

l.O!Q

POBIN+

18

Zm

16

OBIN +

1

-

~,,,

''0

32

1110-=

=

T50+

13

3<'

e4=»L

'/

1

~

00

~

5TART+

INDUSTRIAL

MICRO

SYSTEMS

.c~u

"J

DIU

E - I

....

""0'0'."

~'

I

DRAwt<_y

RJV

c

...

n

IO~::z.8'80

,RE'O'UC

64K

DYI\IAMIC

RAM

(

::...l

((

--"

L00464

AII

iAWOFuM·S

----

--

..

__

..

-

-,

,-

.((

-c'

(•

c-r j

,

11

A1

A7+

A(,,+ IS

AGo

AS+

13

I\S

AY+

II

AY

A3+

aA3

A2+

c;;

A7-

AI+

4

A1

AO+

'L

AO

J.ll'

+S

JC

IB

~.1K

+5 2SLS2S11

18

B7

l,l2!\

r-

l'

4.1K

+5

J5

~

~'6

h

1~

19

13

~

\4

4

51;,

~=B

AllOR +

+S

EN

IIIJJ

>-----05

1G

I~

55

+5

>---<:,~

Is

12

54

+5

..--

3'

l~

~

53

.

+5

f---o2

c131

52

+5

~)1

j25

51

+S

f----G

D113

Bo

POR,

SELE[,

E

C?

1

lUI

BSQlUT+ 12

145

13

SlNP+~

1\

o~

INDUSTRIAL MICRO

SYSTEMS

.c~~.

l-Jot.JE.

jj''I;o.;'

DR.WN

RV

RJV

C.VR

IO.Jt8-60

I

..

IYI.le

64K

DYNAMIC RAM

L00464

AID

3

AW

O

•

FUMS

-_

..

UPO'"l'"

(;,'jK )(

:l

MEMOR~

ARRAY

~DI0+

1'

'1

MOO+

~I~:

(LQj

19

1E

1\'"1

MDP+

1

'4

M01+ 310);"'37

50

1

'l

~

Dll+

1

14

MD5+

71D2

01.1

r.;

r'll.>

D15+

I''!

MDG>+

'"1101

QI~

01"+

H.

\A

41>-

111

3A

5~

<;,~

51>-

5B

8B

16

'JB

'31>-

15

q

15i

'"18

26

1B

<;,8

38

IC

zc

lC

3C

'1C

5C

Be

<;,c

10

3D

BD

10

5D

20

'"ID

GD

9D

I

3C

15TT15'r\

'"I

BIlS"-

__

2

BDG+

_2

BIlP+-

Z

\)04+----..&

BD7+

_2.

I>D3+

_2

BD2+

_2

BD1+

_Z

BOO+

__

2

McA5-

TyPT.Cp,.\.

CONNECTION

A.LL

"RAMS

+12.

+S

~~

19

8[

~[

V'DD

V,

05

''''

AI.

"

(iJq

17 "

As

1213

118

1Z

II'!

1iJ2

'

:1.

lOA>

pPD

~13

131\2

41

'"

00

11

5

P.\

11

AD

~~

\Jss

Vee

'IT

=

-S

+5

ICA5-

ZI

12

3

131

10 04 'I I 0 z

R~SO-

lZA

UA

IIA

1'.1151-

I

RAS2-

I

RAS3-

MC32'i2

81>-13+

1

A7.-

/>.10+

82

20

AIO

81>-12-+

10

AI

AS+

2~

21

A"

BA11+

<0

A8

A'J+

30

Z

All

BA10+

Al

M+

31

25

AS

BA':l+ 9AD

A2+ 81

21

/>.3

BAB+ 8A':l

A1+

80

2'1

Arl.

28

Al+

83

2&

A13

y,,~

+5

AD+

19

23

M

ICAS+ 1

COUNT

6ND[:4

Z

RFSH

EN

T100+ 3RoW EN =

~

II

c/>.s-

~~

I

'"

R-lV

,- _

...

-_

..

(~

l

lb'

._:;------

RAM

. (

.....f...,.

I

L00464A

(_J~toF··5

Ie

----------((

;-(

(

----/"

l'"

(

t5

~

1K

LK~

I

BDP+

010

+

VII-

V12-

'V13-

VI~

VIS-

PIN1-

NMI-

PRDY

+

RROR

L

I8

3E MDP+ ----.!J

18

St

=

2

Il

MOl

+

----.1.

Il

1Ie;, MOb+

----11

It.;

11

IS

11

D5

+

----1Q

IS

91

'1

E9l

(D

MO'1

+

------1

1'1

EE

5

8

13

M03+~

13

lZ

IZ

MOZ+

__

8

12

+5

10

II

MOl

+

----.-J.?,

11

4

10

MDO

oj-

-----'!.

10

CRI

(

~

PARITY

E

LSO

lao

14B

Rl

IO~=

1(,A

330

\~B

5)

DZ."-

~

1 -

f

21

35

)3

to

\~

lZ

IlSI',

JGo

0;

l.'iA

10

~

0------3>

101

10 \8

Il~pr

9

IZ

lioA

0--0

~

\1 o

Q-=--

~Il

-

"c

QB

o----{D

+5

~

~

>-<l

o--[]>

,jJJl

,:,

0--0

o----ID

lGA

~

4'

'-11K

>-<l

o----@

5138

I

10

15

1

14

Z

>-<l

o---{]I>

VRZ

'-

--Q

<>---{It>

11~3

'3

M

<1J

+12

10

1

35

;-

8

I

IN

0 , !

p!Zc+

B01+

BD~

BD5+

B04+

8D3+

BD2+

BD

,.,.

BDO+

tlt.;V

MEMf\!-

!>DSE

\:l-

CAS-

ADDR+

DBIN+

IOWT-

rr-r-----r--

5

.1

C2,"I,(,,8, \5,11, 1'),Z1,

I

SOV

23,28,30, 32,

3~,

3'),

~1)

~

'13,

'is,'n

VR3

-lID

~!

-I

I

¥~:

CI,

3,5,1,'),

1~,

18,

lO,

'12,

n,

1~,

31,

33,3S,qo,

42,4Q,%

+1-C31

I'5UF

Z5V

'~+5

'.J

+1

CI~_

1.1

CIO,

11,

1'l,ZQ,Z5,Zb,~8,

I50V

Q9,

53,5~,55,51D)51

l.

"!:LC%

I'5VF

Z5V

+1.C12

GNO~

15UF

GoND~

Z5V

+8V

+8V

)

INDUSTRIAL

MICRO

SYSTEMS

.c

....

"'.IOfl"..1E

I

APPRO""".?

I

DRAWN'"

"I,

-J

'I

DAU

IO-zs.eO

II

__

...

~

64K

DYNAMIC

RAM

L00464A

:0

OF 5

L"

"

.....

,

.......

""

,_

....

_

...

""

.

....,.

Table of contents