RXD-V252/V252-H

4

CIRCUIT DESCRIPTION

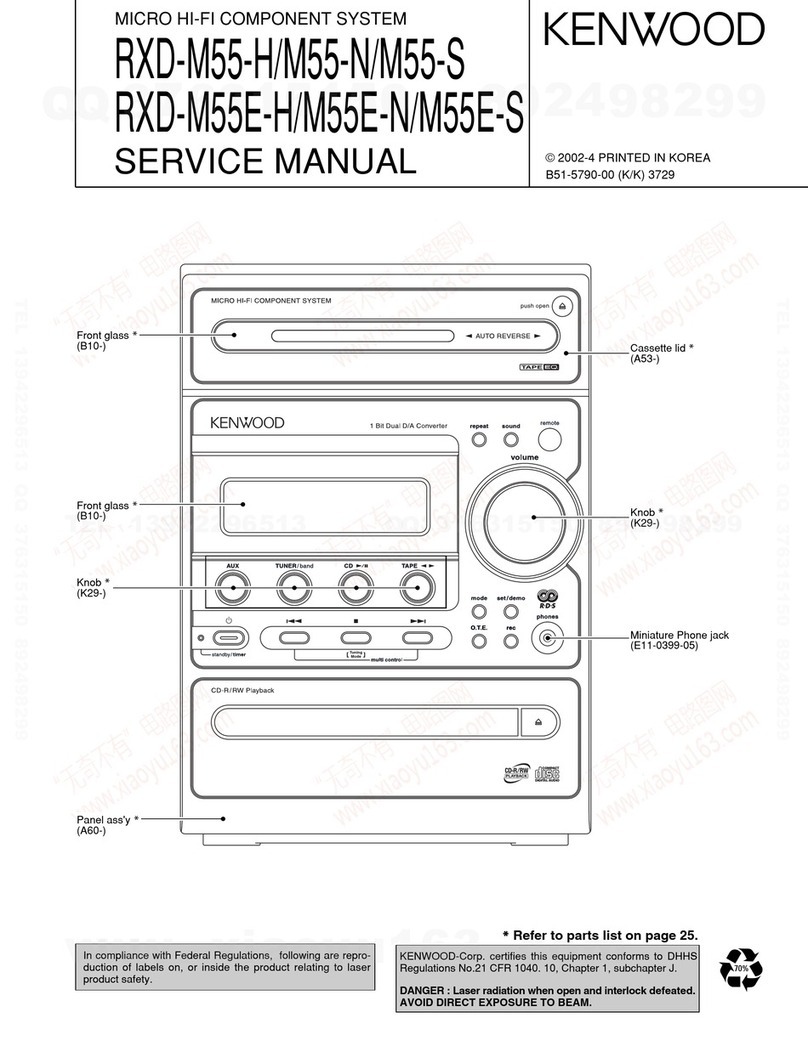

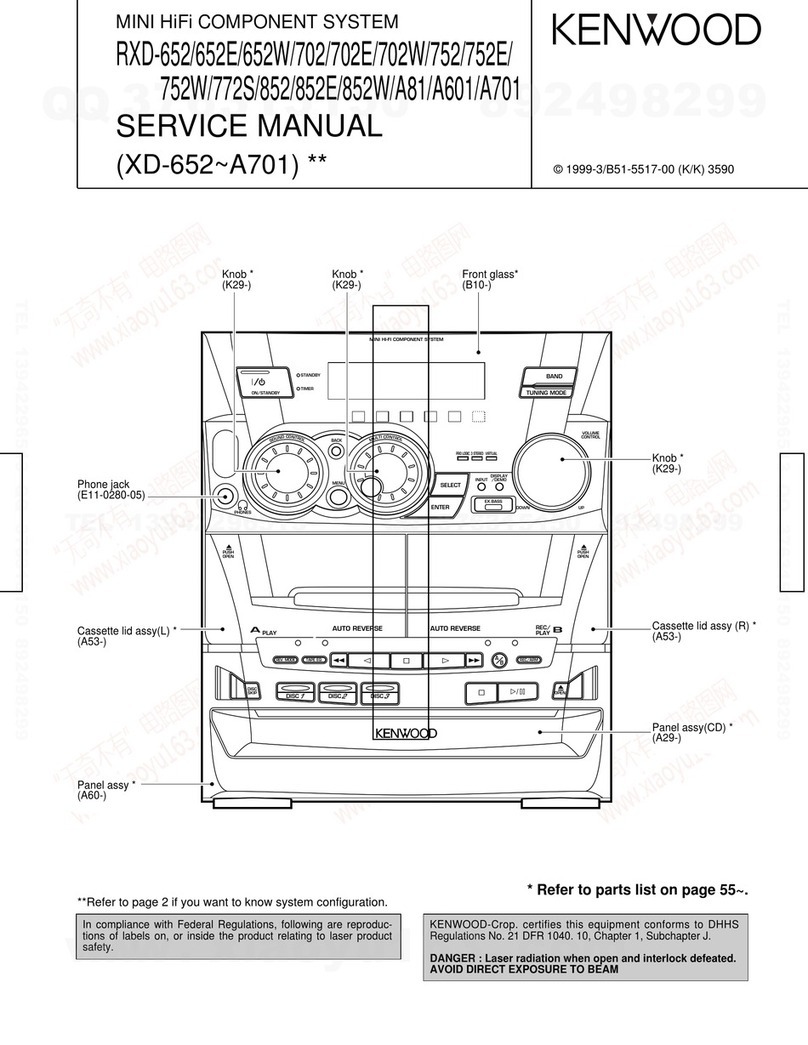

Block Diagram for MPEG1 Video/Audio Processing

RAS#

Processor LA(17:0) DRAM Interface DA(8:0)

Interface LD(7:0) Huffman DBUS(15:1)

LCS3#, LCS#(1:0) RISC Decoder DOU# DRAM

LWR# Processor 2Kx32 ROM DWE#

LOE# 2x32 SRAM CAS#

ACLK AUX(7:1) AUX

Serial ATCLK MPEG

Audio AIN Serial Audio Processor

Interface AOUT Interface

ARFS 64x32 ROM YUV(7:0)

ATFS 32x32 SRAM PCLK2X Screen

ARCLK Registers Video Output PCLK

VSYNC

HSYNC

TDM SEL-PLL(1:0) TDM

Interface TDMCLK Interface On Screen

TDMDR Display CPUCLK Misc

TDMFS DRAM DMA RESET#

Controller

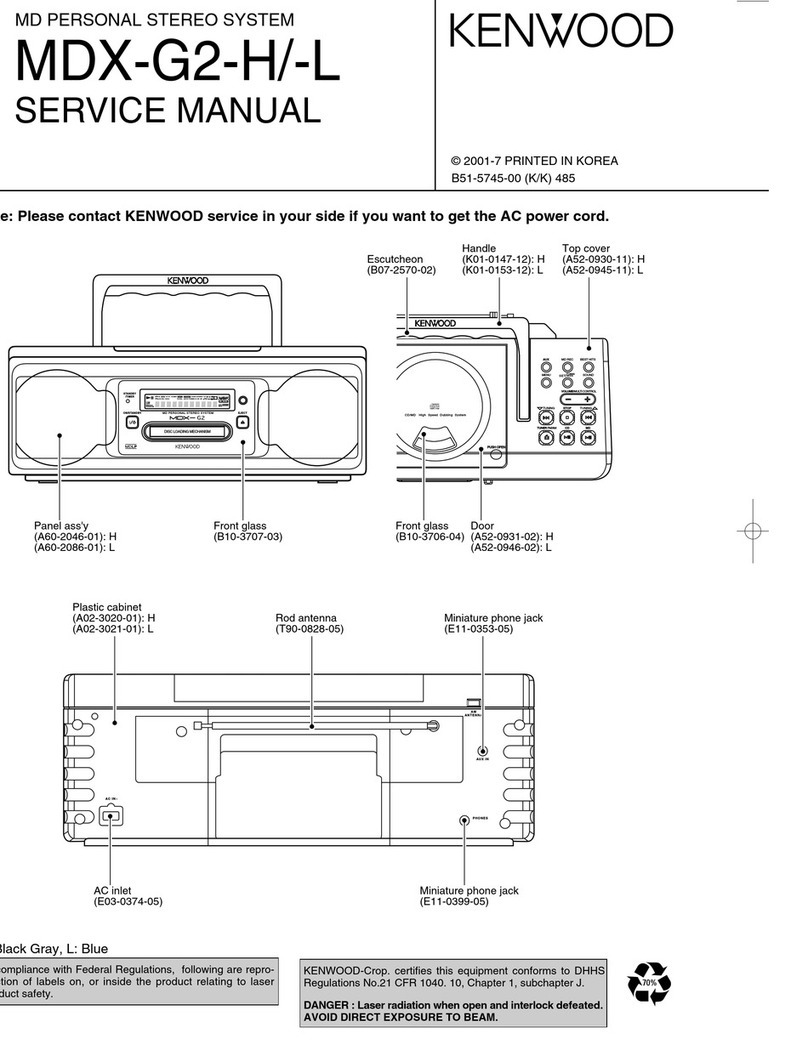

Port No. Port Name I/O Function

1,31,51 VCC3 - Supply voltage for 3.3V.

2 RAS# O DRAM row address strobe (active low).

3 DWE# O DRAM write enable (active low).

4~12 MA(0~8) O DRAM multiplexed row and column address bus.

13~28 DBUS(0~15) I/O DRAM data bus.

29 RESET# I System reset (active low).

30,50,80,100 GND - Ground.

32~39 YUV(0~7) O Y is luminance, UV are chrominance data bus for screen video interface.

YUV(0~7) for 8 bit YUV mode.

40 VSYNC I/O Vertical sync for screen video interface, programmable for rising or

falling edge.

41 HSYNC I/O Horizontal sync for screen video interface, programmable for rising or

falling edge.

42 CPUCLK I RISC and system clock input.

43 PCLK2X I/O Pixel clock: two times the actual pixel clock for screen video interface.

44 PCLK I/O Pixel clock qualifier in for screen video interface.

45~49,52,53,54 AUX(0~7) I/O Auxiliary control pins (AUX0 and AUX1are open collectors).

55~62 LD(0~7) I/O RISC interface data bus.

63 LWR# O Unused.

64 LOE# O RISC interface output enable (active low).

65,66,67 LCS(3,1,0)# O RISC interface chip select (active low).

68~79,82~87 LA(0~17) O RISC interface address bus.

81 VCC - Digital supply voltage for 5.0V.

88 ACLK I/O Master clock for external audio DAC(8.192MHz, 11.2896MHz, 12.288MHz,

16.9344MHz, and 18.432MHz).

O Dual-purpose pin. AOUT is the audio interface serial data output.

Pins SEL -PLL(1: 0) select phase-lock loop(PLL) clock frequency

89 AOUT/SEL/PLL0 I CPUCLK for the Visba : 00 = bypass PLL 01 = 54MHz PLL

10 = 67.5MHz PLL 11 = 81MHz PLL

90 ATCLK I/O Audio transmit bit clock.

O Dual-purpose pin. ATFS is the audio interface transmit frame sync.

91 ATFS/SEL/PLL1 I Pins SEL -PLL(1: 0) select phase-lock loop(PLL) clock frequency CPUCLK

for the Visba. See the SEL -PLL0 pin above for the settings.

92 DOE O Dual-purpose pin. DRAM output enable (active low)/DRAM multiplexed

row and column address bus.

93 AIN I Audio interface serial data input.

94 ARCLK I Audio receive bit clock.

95 ARFS I Audio interface receive frame sync.

96 TDMCLK I TDM interface serial clock.

97 TDMDR I TDM interface serial data receive.

98 TDMFS I TDM interface frame sync.

99 CAS# O DRAM column address strobe bank 0 (active low).

Port Function of MPEG1 Video/Audio Processing : ES3880 (ICM2)