Lattice Semiconductor CrossLink-NX User manual

CrossLink-NX PCIe Bridge Board

Multifunction Demo

User Guide

FPGA-UG-02150-1.0

February 2022

CrossLink-NX PCIe Bridge Board Multifunction Demo

User Guide

© 2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

2 FPGA-UG-02150-1.0

Disclaimers

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its

products for any particular purpose. All information herein is provided AS IS, with all faults and associated risk the responsibility entirely of the Buyer.

Buyer shall not rely on any data and performance specifications or parameters provided herein. Products sold by Lattice have been subject to limited

testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. No Lattice

products should be used in conjunction with mission- or safety-critical or any other application in which the failure of Lattice’s product could create a

situation where personal injury, death, severe property or environmental damage may occur. The information provided in this document is

proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at

any time without notice.

CrossLink-NX PCIe Bridge Board Multifunction Demo

User Guide

© 2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-UG-02150-1.0 3

Contents

Acronyms in This Document.................................................................................................................................................6

1. Introduction..................................................................................................................................................................7

1.1. Learning Objectives.............................................................................................................................................7

2. Hardware and Software Requirements........................................................................................................................8

2.1. Hardware Requirements.....................................................................................................................................8

2.2. Software Requirements ......................................................................................................................................8

3. Setting Up the Demo ....................................................................................................................................................9

3.1. Hardware Setup ..................................................................................................................................................9

3.1.1. Jumper Configuration.....................................................................................................................................9

3.1.2. Programming the FPGA................................................................................................................................10

3.1.3. Status LED.....................................................................................................................................................13

3.2. Software Setup..................................................................................................................................................14

3.2.1. Software Setup and Installation for Windows .............................................................................................14

3.2.2. Software Setup for Linux..............................................................................................................................29

4. Demo Design Overview ..............................................................................................................................................32

4.1. Theory of Operation..........................................................................................................................................32

4.2. Design Overview ...............................................................................................................................................33

4.2.1. GUI Application ............................................................................................................................................33

4.2.2. Device Drivers...............................................................................................................................................33

4.2.3. Device Hardware (FPGA Design) ..................................................................................................................34

5. Application Overview .................................................................................................................................................35

5.1. Running the PCI Express Demo Application......................................................................................................35

5.2. Using the PCI Express Demo Application User Interface...................................................................................36

5.2.1. Functionality Test Tab ..................................................................................................................................36

5.2.2. GPIO .............................................................................................................................................................36

5.2.3. I2C.................................................................................................................................................................37

5.2.4. MDIO ............................................................................................................................................................44

6. Importing and Building the FPGA Demonstration......................................................................................................47

6.1. Hardware Directory Structure...........................................................................................................................47

6.2. Building Lattice Radiant Project ........................................................................................................................47

7. Troubleshooting .........................................................................................................................................................48

7.1. SPI Flash Update................................................................................................................................................48

7.2. Driver Installation and User Interface Launch for Windows.............................................................................49

7.2.1. Problem in Driver Installation ......................................................................................................................49

7.2.2. Problem with Launching User Interface.......................................................................................................49

7.3. Driver Installation User Interface Launch for Linux...........................................................................................50

7.3.1. Problem in Driver Loading............................................................................................................................50

7.3.2. Problem with User Interface Launching.......................................................................................................51

Technical Support Assistance .............................................................................................................................................52

Revision History..................................................................................................................................................................53

CrossLink-NX PCIe Bridge Board Multifunction Demo

User Guide

© 2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

4 FPGA-UG-02150-1.0

Figures

Figure 3.1. CrossLink-NX PCIe Bridge Board Jumper Location..............................................................................................9

Figure 3.2. CrossLink-NX PCIe Bridge Board Connection....................................................................................................10

Figure 3.3. Creating a New Project from a Scan .................................................................................................................10

Figure 3.4. Radiant Programmer Window ..........................................................................................................................11

Figure 3.5. FPGA Device Settings ........................................................................................................................................11

Figure 3.6. Device Properties Window for SPI Flash Programming....................................................................................12

Figure 3.7. Programmer Menu Bar.....................................................................................................................................12

Figure 3.8. Programmer Output Window...........................................................................................................................12

Figure 3.9. Status LED .........................................................................................................................................................13

Figure 3.10. Running Disable Integrity Checks Command..................................................................................................14

Figure 3.11. Running Test Sign On Command.....................................................................................................................14

Figure 3.12. Troubleshoot Option.......................................................................................................................................15

Figure 3.13. Advanced Options...........................................................................................................................................15

Figure 3.14. Select Startup Settings....................................................................................................................................16

Figure 3.15. Restarting Windows........................................................................................................................................16

Figure 3.16. Welcome Page ................................................................................................................................................17

Figure 3.17. Destination Folder Page..................................................................................................................................18

Figure 3.18. Summary Page ................................................................................................................................................18

Figure 3.19. Application Installed .......................................................................................................................................19

Figure 3.20. Device Configuration Prompt .........................................................................................................................19

Figure 3.21. Device Driver Installation Wizard ...................................................................................................................20

Figure 3.22. Windows Security in Driver Installation..........................................................................................................20

Figure 3.23. Device Driver Installation Completed .............................................................................................................21

Figure 3.24. Device Manager..............................................................................................................................................21

Figure 3.25. Showing Device Properties .............................................................................................................................22

Figure 3.26. Hardware IDs of MDIO Device ........................................................................................................................23

Figure 3.27. Hardware IDs of I2C Device .............................................................................................................................23

Figure 3.28. Hardware IDs of GPIO Device .........................................................................................................................24

Figure 3.29. Update Driver Menu in Device Manager........................................................................................................25

Figure 3.30. Update Driver Options....................................................................................................................................25

Figure 3.31. Browse the Driver for Device..........................................................................................................................26

Figure 3.32. Windows Security in Device Manager ............................................................................................................26

Figure 3.33. Driver Installation Status Message .................................................................................................................27

Figure 3.34. Multifunction Demo Device Name Displayed in Device Manager..................................................................27

Figure 3.35. MDIO, I2C, and GPIO Device Drivers in Device Manager ................................................................................28

Figure 4.1. Relationship of the Hardware and Software Components...............................................................................32

Figure 4.2. PCIe Multifunction Demo SW Design................................................................................................................33

Figure 4.3. PCIe Multifunction FPGA Design.......................................................................................................................34

Figure 5.1. PCIe Test Application Device Info Tab ..............................................................................................................35

Figure 5.2. Functionality Test Tab.......................................................................................................................................36

Figure 5.3. GPIO Input Switch.............................................................................................................................................36

Figure 5.4. GPIO Output LEDs. ............................................................................................................................................37

Figure 5.5. I2C Bit-Rate Selection........................................................................................................................................37

Figure 5.6. I2C Address Program.........................................................................................................................................37

Figure 5.7. I2C Master Write...............................................................................................................................................37

Figure 5.8. Single Write to an Arbitrary Address of IMX258-0AQH5 Camera.....................................................................38

Figure 5.9. Sequential Write Starting from an Arbitrary Address of IMX258-0AQH5 Camera ...........................................38

Figure 5.10. I2C Master Write Procedure...........................................................................................................................39

Figure 5.11. I2C Master Read..............................................................................................................................................39

Figure 5.12. Single Read from the Held Address of IMX258-0AQH5 camera .....................................................................40

Figure 5.13. Sequential Read Starting from the Held Address of IMX258-0AQH5 Camera................................................40

Figure 5.14. I2C Master Write to Write the Register Address.............................................................................................40

CrossLink-NX PCIe Bridge Board Multifunction Demo

User Guide

© 2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-UG-02150-1.0 5

Figure 5.15. I2C Master Read ..............................................................................................................................................41

Figure 5.16. I2C Master Register Read ................................................................................................................................41

Figure 5.17. Single Read from an Arbitrary Address of MX258-0AQH5 Camera................................................................41

Figure 5.18. Sequential Read Starting from an Arbitrary Address of MX258-0AQH5 Camera...........................................41

Figure 5.19. I2C Master Register Read ................................................................................................................................42

Figure 5.20. I2C Master Register Read ................................................................................................................................42

Figure 5.21. I2C Batch Mode Read/Write ...........................................................................................................................43

Figure 5.22. MDIO Phy addr ...............................................................................................................................................44

Figure 5.23. MDIO Configuration Register Read.................................................................................................................44

Figure 5.24. MDIO Register Write.......................................................................................................................................44

Figure 5.25. MDIO Configuration through File ...................................................................................................................45

Figure 5.26. MDIO Configuration File Example...................................................................................................................45

Figure 7.1. TCK Frequency Setting......................................................................................................................................48

Figure 7.2. Port Selection....................................................................................................................................................48

Figure 7.3. User Interface with No Device Driver ...............................................................................................................49

Figure 7.4. lspci -vnm Output Image...................................................................................................................................50

Figure 7.5. Content List of Demonstration/Linux Directory. ..............................................................................................51

Figure 7.6. Content List of Software/Linux Directory .........................................................................................................51

Tables

Table 3.1. Jumper Configuration ..........................................................................................................................................9

Table 3.2. Status LED Description.......................................................................................................................................13

Table 5.1. Master Write Control Description......................................................................................................................38

Table 5.2. Registers of MX258-0AQH5 CMOS Camera.......................................................................................................38

Table 5.3. Master Register Read Control Description ........................................................................................................41

Table 5.4. Transaction Log Control Description..................................................................................................................42

Table 5.5. Batch Mode Control Description .......................................................................................................................43

Table 5.6. MDIO Batch Mode Control Description.............................................................................................................45

Table 5.7. MDIO Batch Mode Table Description ................................................................................................................45

Table 5.8. MDIO Input File Description...............................................................................................................................46

CrossLink-NX PCIe Bridge Board Multifunction Demo

User Guide

© 2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

6 FPGA-UG-02150-1.0

Acronyms in This Document

A list of acronyms used in this document.

Acronym

Definition

BAR

Base Address Register

FDSOI

Fully Depleted Silicon on Insulator

FPGA

Field-Programmable Gate Array

LED

Light-emitting diode

MIPI

Mobile Industry Processor Interface

PCIe

PCI Express

PHY

Physical Layer

SPI

Serial Peripheral Interface

USB

Universal Serial Bus

I2C

Inter-integrated Circuit

MDIO

Management Data Input Output

GPIO

General Purpose Input Output

CrossLink-NX PCIe Bridge Board Multifunction Demo

User Guide

© 2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-UG-02150-1.0 7

1. Introduction

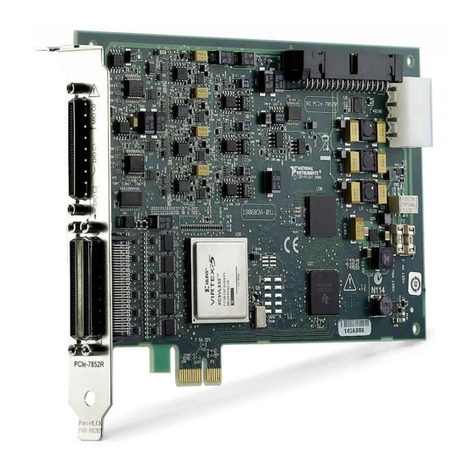

This guide describes how to setup and run the PCIe Multifunction Demo on the CrossLink™-NX PCIe Bridge Board. The

CrossLink-NX Bridge Board features the CrossLink-NX FPGA in the 400-ball caBGA package (LIFCL-40-8BG400C), which is

built on the Lattice Nexus FPGA platform using low power 28 nm FDSOI technology. The board can expand the usability

of the CrossLink-NX FPGA with 2.5 Gbps Hardened MIPI D-PHY, 5 Gbps PCIe, 1.5 Gbps programmable I/O, DDR3, USB

3.0, Ethernet, and SGMII. Board resources such as jumpers, LED indicators, push buttons, and switches are available for

user-defined applications.

This guide familiarizes you with the process of setting up your PCI Express development environment. It is assumed

that you do not have any associated tools installed on your system.

The demo discussed in this document is the PCI Express Multifunction Demo.

1.1. Learning Objectives

After completing the steps in this guide, you will be able to perform the following:

Set up the CrossLink-NX PCIe Bridge Board and become familiar with its main features

Install all applicable development tools and PCI Express demos

Establish communication between the CrossLink-NX PCIe Bridge Board through the PCI Express link

Run the PCI Express Multifunction Demo which implements three separate PCI Express functions on a single

endpoint device. Each function allows you to control a different aspect of the CrossLink-NX PCIe Bridge Board.

Use what the demo teaches you about designing Lattice PCI Express solutions.

Modify and rebuild the PCI Express Multifunction Demo.

Become familiar with the software development tools and major design flow steps employed in this kit.

Use other existing documentation in conjunction with this guide.

This document assumes that you have already installed the Lattice Radiant™ design software. This document covers

some of the basic of function of Lattice Radiant software. If you would like to learn more about Lattice Radiant

software, refer to the Lattice Radiant software Help system.

CrossLink-NX PCIe Bridge Board Multifunction Demo

User Guide

© 2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

8 FPGA-UG-02150-1.0

2. Hardware and Software Requirements

2.1. Hardware Requirements

To install the kit design and run the demo software, a computer with a PCI Express ×16, ×8, ×4, or ×1 slot is required.

The computer must also have a USB port and be able to run the Lattice Radiant Software. All other hardware and

drivers are included in the kit.

Mini-USB to USB-A cable for programming the bitstream

12 V Power Adapter

CrossLink-NX PCIe Bridge Board

2.2. Software Requirements

The following software is required to obtain the expected results for the procedures described in this guide:

Lattice Radiant Software 2.2 or later (available at the Lattice website Design Software and IP page).

CrossLink-NX Multifunction Demo for Windows 10 or Linux

Windows 10 or Ubuntu 18.04.6

Bit file for the CrossLink-NX board SPI Flash (LIFCL40_PCIe_MultiFunction.bit)

CrossLink-NX PCIe Bridge Board Multifunction Demo

User Guide

© 2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-UG-02150-1.0 9

3. Setting Up the Demo

3.1. Hardware Setup

This section covers the steps in programming the demo to the SPI memory of the CrossLink-NX PCIe Bridge Board.

3.1.1. Jumper Configuration

Install the jumpers listed in Table 3.1. Note that J31, J32, and J33 are different from the default board configuration.

Table 3.1. Jumper Configuration

Jumper Checklist

Configuration

J11, J18

Connect pins 1 and 2

J7, J6, J13, J14

Connect pins 1 and 2

J31, J32, J33

Connect pins 1 and 2

J8, J9, J10, J15, J16, J19, J20, J21, J22, J23, J25, J26, J29, J30,

J34, J35, J36, J37, J38, J39, J42

These are current measurement headers and should be kept

Open.

J51

Connect pins 2 and 4

J48

Connect pins 2 and 3

J27

Connect pins 1 and 2

J45, J46

Connect pins 1 and 2

J17

Open

Figure 3.1 shows the location of the jumpers.

J48

J51 Current

Measurement

2-Pin Header J31, J32, J33

J17

J27

J45, J46

J11, J18 J7, J6, J13, J14

Functional Jumper

Current Measurment Jumper

Figure 3.1. CrossLink-NX PCIe Bridge Board Jumper Location

CrossLink-NX PCIe Bridge Board Multifunction Demo

User Guide

© 2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

10 FPGA-UG-02150-1.0

Make sure the card is plugged into a PCIe slot or connected to the 12 V input supply. If the card is plugged into the PCIe

slot, external power is provided by the system, and SW2 should be in the up position to receive power from the PCIe

slot. If external 12 V power is provided, then SW2 should be in the down position to receive power from the external

12 V connection. Connect the board to the PC running the Lattice Radiant software with the Mini USB Type A cable as

shown in Figure 3.4.

Mini

USB

Type A

Cable 12 V Input

Supply

Connector

SW2

Figure 3.2. CrossLink-NX PCIe Bridge Board Connection

3.1.2. Programming the FPGA

To program the CrossLink-NX FPGA device:

1. Create a new project using the Lattice Radiant Programmer software. In the Getting Started dialog box, indicate

Project Name and Location as shown in Figure 3.3.

2. Select Create a new project from scan. Values are indicated in the Cable, Port, and TCK Divider Setting (0-30×)

fields.

3. Click OK.

Figure 3.3. Creating a New Project from a Scan

CrossLink-NX PCIe Bridge Board Multifunction Demo

User Guide

© 2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-UG-02150-1.0 11

4. The main interface opens as shown in Figure 3.4.

Figure 3.4. Radiant Programmer Window

5. If the Programmer settings do not match the settings shown in Figure 3.5, select these settings (Device Family and

others) manually from drop down menu.

Figure 3.5. FPGA Device Settings

To select programming settings:

1. Browse and select the Programming file LIFCL40_PCIe_Multifunction.bit from Demonstration\Bitstream

2. Click OK.

3. Double-click under Operation to open the Device Properties dialog box.

CrossLink-NX PCIe Bridge Board Multifunction Demo

User Guide

© 2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

12 FPGA-UG-02150-1.0

Figure 3.6. Device Properties Window for SPI Flash Programming

4. Select the settings as shown in Figure 3.6.

5. Click the Programming button from the menu bar shown in Figure 3.7 to start programming.

Figure 3.7. Programmer Menu Bar

When the FPGA programming is successful, the output console shows an Operation Successful message as shown in

Figure 3.8.

Figure 3.8. Programmer Output Window

If the programming operation was not successful, please refer to the troubleshooting section of this document.

CrossLink-NX PCIe Bridge Board Multifunction Demo

User Guide

© 2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-UG-02150-1.0 13

After programming, power cycle the board and check the status LEDs on the board according to Table 3.2.

3.1.3. Status LED

The three status LEDs are shown in Figure 3.9.

1 2 3

Figure 3.9. Status LED

The description of each status LED is provided in Table 3.2.

Table 3.2. Status LED Description

Sl. No

Name

Description

1

125MHz Clock present

Green Blinking when clock present

2

PCIe Link Up

Green: Lights up if PCIe link up is successful

Red: Lights up if PCIe link up is not successful

3

DONE

Green: Lights if configuration is successful

CrossLink-NX PCIe Bridge Board Multifunction Demo

User Guide

© 2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

14 FPGA-UG-02150-1.0

3.2. Software Setup

This section provides the procedure for installing software onto the host machine.

3.2.1. Software Setup and Installation for Windows

Before installing the driver, driver signature enforcement should be disabled.

3.2.1.1. Disabling Driver Signature Enforcement Permanently

To permanently disable driver signature enforcement:

1. Start the Command Prompt as administrator.

2. Enter the following lines and press Enter.

bcdedit.exe -set loadoptions DISABLE_INTEGRITY_CHECKS

Figure 3.10. Running Disable Integrity Checks Command

bcdedit.exe -set TESTSIGNING ON

Figure 3.11. Running Test Sign On Command

3. Close the Command Prompt and restart your PC.

CrossLink-NX PCIe Bridge Board Multifunction Demo

User Guide

© 2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-UG-02150-1.0 15

3.2.1.2. Disabling Driver Signature Enforcement Temporarily

To disable the driver signature enforcement temporarily on Windows 10.

Note: if Driver Signature Enforcement is already disabled, skip this section and proceed to the Driver Installation

section.

1. Press the Windows key and click the power button.

2. Press and hold the Shift key and click Restart.

3. When the Choose an option screen appears as shown in Figure 3.12, release the Shift key.

4. Click Troubleshoot.

Figure 3.12. Troubleshoot Option

5. Select Advanced options and press Enter.

Figure 3.13. Advanced Options

CrossLink-NX PCIe Bridge Board Multifunction Demo

User Guide

© 2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

16 FPGA-UG-02150-1.0

6. Select Startup Settings and press Enter.

Figure 3.14. Select Startup Settings

7. Press Enter to restart.

Figure 3.15. Restarting Windows

8. After restarting, select Option 7 to disable driver signature verification.

3.2.1.3. Driver Installation

There are two ways to install the device driver:

Install through user interface installer

Install manually

CrossLink-NX PCIe Bridge Board Multifunction Demo

User Guide

© 2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-UG-02150-1.0 17

Installing Multifunction Demo Device Driver through the User Interface Installer

The Multifunction Demo device driver can also be installed during the installation of the user interface as described in

the following section.

The Installer provides a standard packaging format for applications and a standard method for customizing the

applications. The installer helps to install the CrossLink-NX PCIe Bridge Board Multifunction Demo application in your

system.

The Framework supported version is Windows 10 use WDF 1.25 or earlier.

To install the Multifunction Demo device driver through user interface:

1. In the Demonstration\Windows10\Application folder, double click setup.exe.

2. The welcome page appears. Click Next.

.

Figure 3.16. Welcome Page

3. Provide the location where you want to install the application. Click Next.

CrossLink-NX PCIe Bridge Board Multifunction Demo

User Guide

© 2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

18 FPGA-UG-02150-1.0

Figure 3.17. Destination Folder Page

4. The installation summary page is shown. Click Install.

Note: Administrative access is required to run this command.

Figure 3.18. Summary Page

CrossLink-NX PCIe Bridge Board Multifunction Demo

User Guide

© 2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-UG-02150-1.0 19

5. Installation of the Multifunction Demo application starts. When installation of the software is complete, the drivers

are installed.

Figure 3.19. Application Installed

6. A message box appears. Click Yes.

Figure 3.20. Device Configuration Prompt

CrossLink-NX PCIe Bridge Board Multifunction Demo

User Guide

© 2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

20 FPGA-UG-02150-1.0

7. The device driver installation wizard opens. Click Next.

Figure 3.21. Device Driver Installation Wizard

8. If you receive a Windows Security prompt, select Install this driver software anyway as shown in Figure 3.22.

Figure 3.22. Windows Security in Driver Installation

9. If the driver is installed successfully, a message is displayed as shown in Figure 3.23.

Other manuals for CrossLink-NX

7

Table of contents

Popular Network Hardware manuals by other brands

McAfee

McAfee EWS-3100-00AA quick start guide

Extron electronics

Extron electronics Surface Mount Boxes SMB 101 Specifications

Ubiquiti

Ubiquiti airVision-C quick start guide

Precidia

Precidia Cell232Plus user guide

Digiever

Digiever DS-2009 Series user manual

Cambium Networks

Cambium Networks PTP 820S Technical description