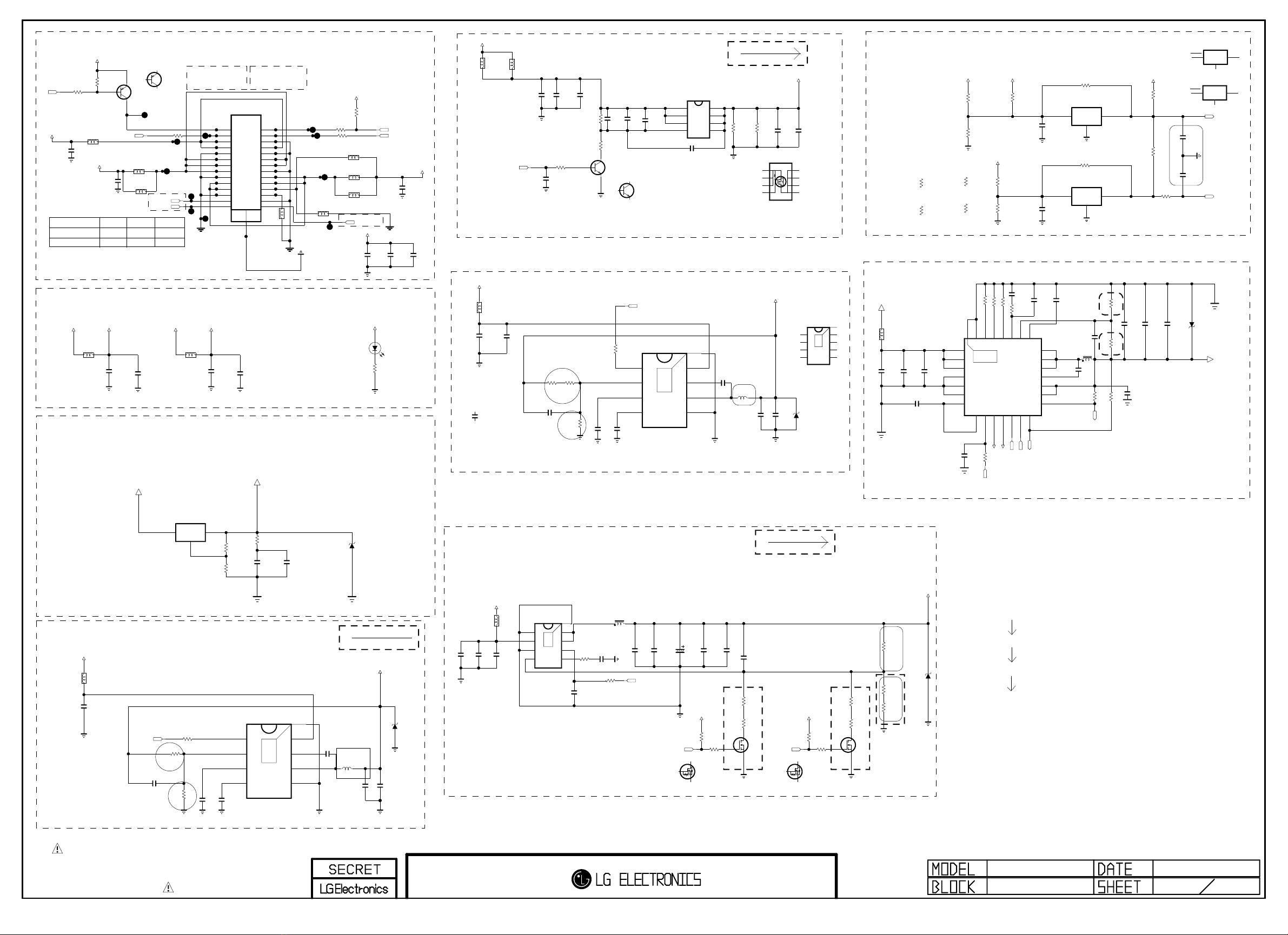

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FIRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFACTURES SPECIFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

2014-12-17LM15U

1

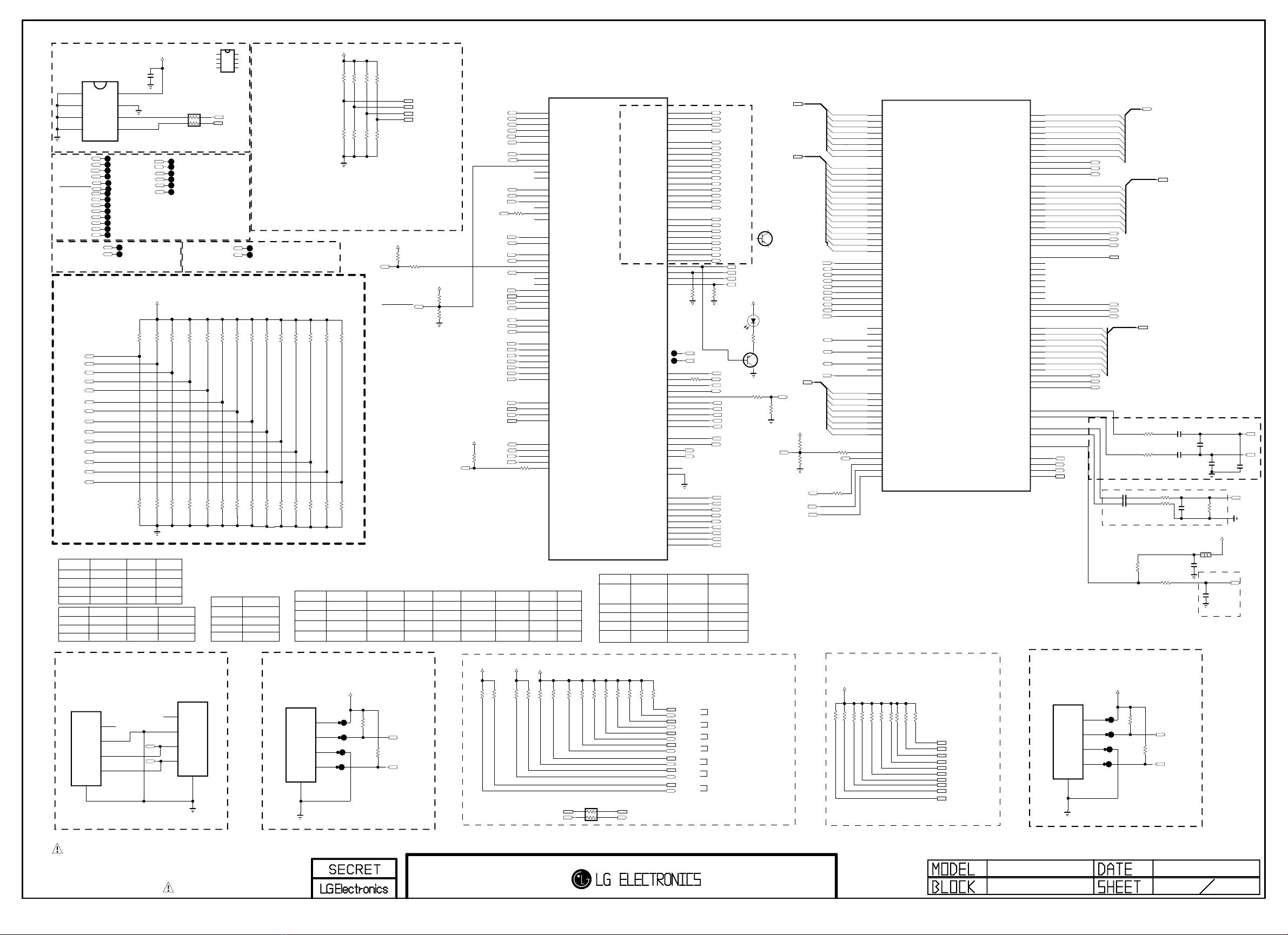

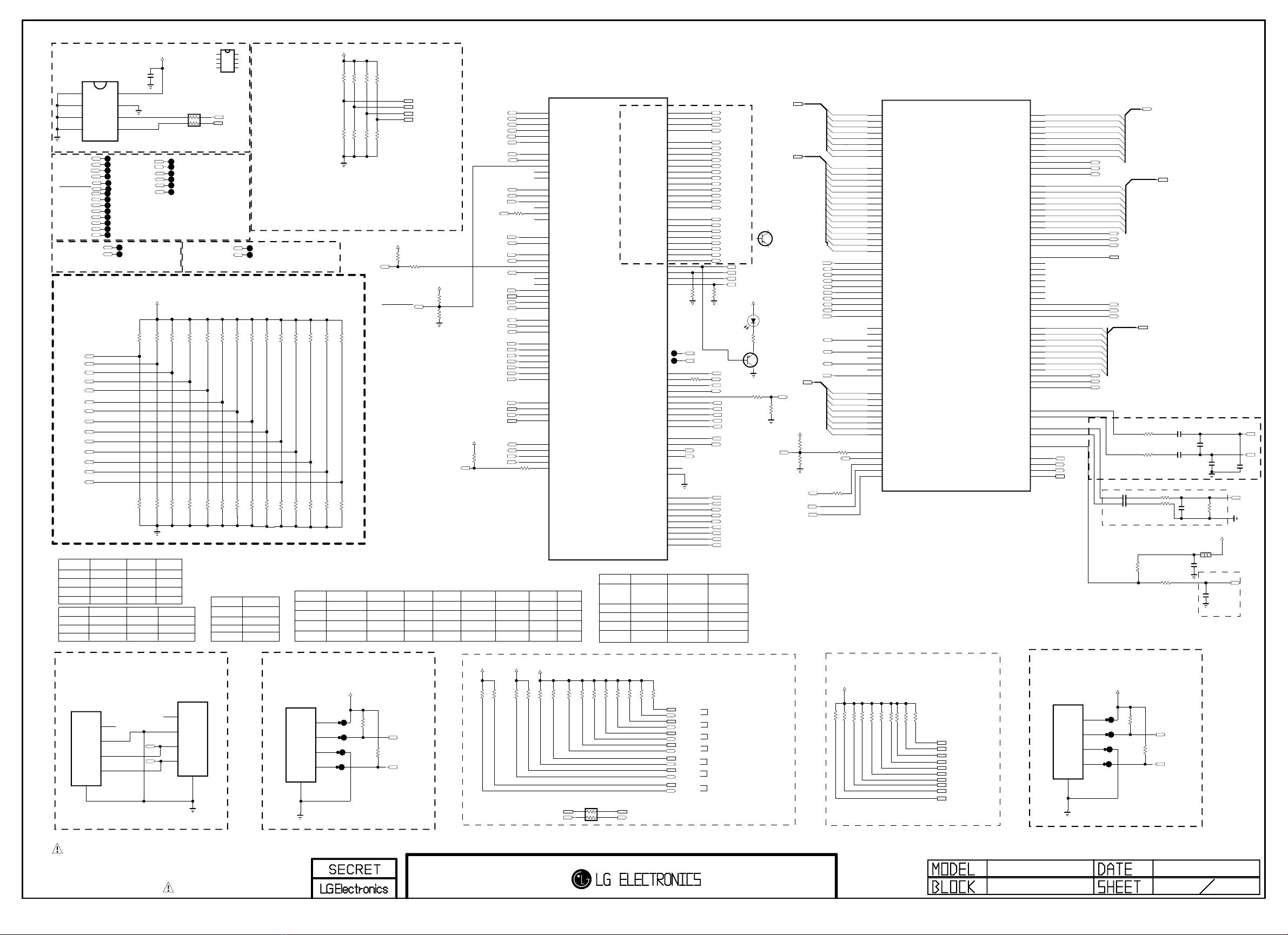

MAIN1_SYSTEM

FE_DEMOD1_TS_DATA[4]

TPI_DATA[2]

EB_ADDR[0]

FE_DEMOD1_TS_DATA[3]

EMMC_DATA[1]

FE_DEMOD1_TS_DATA[6]

EMMC_DATA[0]

EB_ADDR[1]

EMMC_DATA[2]

EB_ADDR[4]

EMMC_DATA[7]

TPI_DATA[0-7]

EMMC_DATA[6]

EMMC_DATA[3]

EB_ADDR[3]

EB_ADDR[2]

EB_ADDR[5]

EMMC_DATA[4]

EMMC_DATA[5]

EB_ADDR[6]

EB_DATA[6]

TPI_DATA[7]

FE_DEMOD1_TS_DATA[7]

EB_ADDR[10]

FE_DEMOD1_TS_DATA[1]

TPI_DATA[3]

EB_DATA[1]

EB_ADDR[9]

TPI_DATA[6]

EB_ADDR[14]

TPI_DATA[0]

TPI_DATA[5]

TPI_DATA[4]

EB_ADDR[8]

TPI_DATA[1]

FE_DEMOD1_TS_DATA[2]

EB_DATA[3]

EB_DATA[5]

EB_DATA[4]

EB_DATA[7]

EB_ADDR[13]

EB_ADDR[12]

EB_DATA[2]

EB_ADDR[7]

EB_DATA[0]

EB_ADDR[11]

FE_DEMOD1_TS_DATA[5]

FE_DEMOD1_TS_DATA[0]

TPO_DATA[1]

TPO_DATA[6]

TPO_DATA[7]

TPO_DATA[0]

TPO_DATA[2]

TPO_DATA[4]

TPO_DATA[5]

TPO_DATA[3]

I2C_SCL7

PWM_PM

USB_CTL3

BIT7

AMP_RESET_N

I2C_SCL1

USB_CTL2

TXOSD_1P

LOCKAn_Video

I2C_SDA3

DDCA_DA

USB_CTL1

BIT0

I2C_SDA3

TXVBY1_0P

BIT11

TXVBY1_6N

TPI_SOP

EB_BE_N1

BIT8

FRC_FLASH_WP

FE_DEMOD1_TS_SYNC

DDTS_RX

I2C_SDA4

I2C_SDA3

EB_ADDR[0-14]

SPI_DI_SOC

BIT2

TXVBY1_6P

TXVBY1_7N

FE_DEMOD1_TS_CLK

TXVBY1_4P

+3.3V_NORMAL

TXVBY1_2P

SOC_TX

WOL_WAKE_UP

I2C_SCL1

TXOSD_2N

I2C_SCL2

5V_DET_HDMI_2

DDCA_DA

DDTS_TX

I2C_SCL_MICOM

TXVBY1_1P

+3.3V_NORMAL

BIT9

/PCM_CE1

PWM_DIM2

TCON_I2C_EN

TCON_I2C_EN

BIT8

AMP_RESET_N

M_RFModule_RESET

EB_OE_N

/USB_OCD3

I2C_SDA6

SOC_TX

SC_DET

EMMC_CLK

BIT6

BIT7

I2C_SDA1

/USB_OCD1

I2C_SCL3

+3.3V_NORMAL

BIT0

M_RFModule_RESET

AVDD_3P3

LED1

FE_DEMOD3_TS_SYNC

SOC_RX

+3.3V_TU

EMMC_DATA[0-7]

TXOSD_3P

PCM_RESET

EB_WE_N

I2C_SDA1

BIT4

FRC_FLASH_SEL

USB_CTL2

+3.3V_LNA_TU

+3.3V_NORMAL

/USB_OCD2

+3.3V_NORMAL

HP_DET

TXOSD_0N

EMMC_CMD

TXVBY1_4N

HTPDAn_OSD

SPI_CK_SOC

RF_SWITCH_CTL

DDTS_TX

I2C_SDA6

HTPDAn_Video

L_DIM_EN

URSA_RESET_SoC

BIT10

I2C_SDA7

I2C_SDA1

TXVBY1_3N

I2C_SCL3

+3.3V_NORMAL

FE_DEMOD3_TS_DATA

I2C_SDA2

TXVBY1_2N

/USB_OCD1

TPI_VAL

I2C_SCL4

URSA9_CONNECT

SPI_DO_SOC

BIT11

IF_P

I2C_SCL5

BIT6

BIT1

CORE_VID0

I2C_SDA7

I2C_SDA_MICOM

CAM_IREQ_N

BIT1

DDTS_RX

CPU_VID0

LED0

TXVBY1_3P

FE_DEMOD3_TS_CLK

/TU_RESET1

TXVBY1_1N

EB_BE_N0

LED0

3D_EN

FE_DEMOD1_TS_VAL

FE_DEMOD1_TS_DATA[0-7]

5V_DET_HDMI_3

AV2_CVBS_DET

EB_DATA[0-7]

TXVBY1_5P

TXOSD_0P

PCM_5V_CTL

I2C_SCL3

/TU_RESET1

TXVBY1_7P

TXOSD_1N

PWM_PM

TPI_DATA[0-7]

+3.3V_NORMAL

+3.3V_NORMAL

BIT3 EMMC_STRB

TXOSD_3N

PCM_5V_CTL

I2C_SCL6

I2C_SCL6

5V_DET_HDMI_1

FE_DEMOD3_TS_VAL

SOC_RX

BIT4

DDCA_CK

BIT2

TXVBY1_5N

HTPDAn_OSD

BIT9

IF_N

BIT5

BIT10

TU_SIF

SPI_DI_SOC

CAM_WAIT_N

LED1

PWM_DIM

+3.5V_ST

/SPI_CS

TXVBY1_0N

AV1_CVBS_DET

I2C_SDA5

CAM_REG_N

/USB_OCD2

COMP1_DET

BIT5

EMMC_RST

BIT3

I2C_SCL7

RF_SWITCH_CTL

+3.3V_NORMAL

TPI_CLK

+3.3V_NORMAL

CAM_CD1_N

I2C_SCL1

TXOSD_2P

LOCKAn_OSD

IF_AGC

USB_CTL1

DDCA_CK

HTPDAn_Video

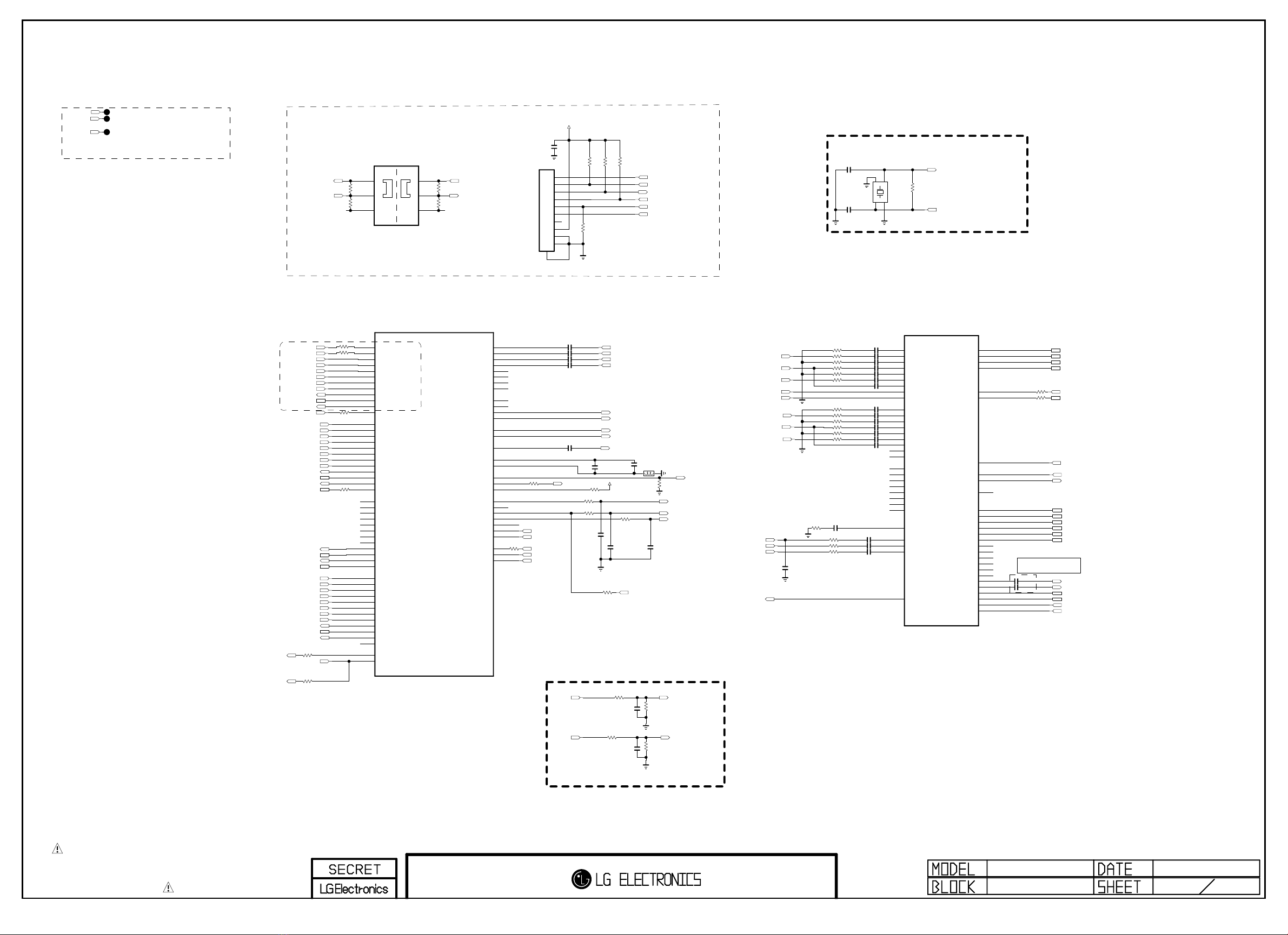

L/D_CLK_SOC

L/D_VSYNC_SOC

L/D_DI_SOC

+3.3V_NORMAL

L/D_CLK_SOC

L/D_VSYNC_SOC

L/D_DI_SOC

SPI_DO_SOC

SPI_DI_SOC

SPI_CK_SOC

/SPI_CS

FRC_FLASH_SEL

FRC_FLASH_WP

TXOSD_0P

TXOSD_0N

TXOSD_1N

TXOSD_2N

TXOSD_2P

TXOSD_3P

TXOSD_3N

TXOSD_1P

LOCKAn_OSD

URSA9_CONNECT

COMPENSATION_DONE

COMPENSATION_DONE

FAN_ON

FAN_ON

DATA_FORMAT_0_SOC

DATA_FORMAT_1_SOC

DATA_FORMAT_1_SOC

DATA_FORMAT_0_SOC

IC102-*1

BR24G256FJ-3

Rohm_NVRAM

3

A2

2

A1

4

GND

1

A0

5SDA

6SCL

7WP

8VCC

R107 10K

BIT1_0

R166 4.7K

R142

10K

R139

1.8K

P102

12507WS-04L

UART_4PIN_WAFER

1

2

3

4

5

R116 10K

BIT4_1

R124 10K

BIT8_1

R111 10K

BIT3_0

R177

10K

OPT

R122 10K

BIT7_1

R141 100

R157 4.7K

R135

1.8K

R121 10K

BIT7_0

R150 10K

R105 10K

OPT

R100 10K

OPT

R163 4.7K

R183 10K

OPT

R167

0

FRC_FLASH_SEL

C103

0.1uF

C122

100pF

OPT

R158 4.7K

OPT

R120 10K

BIT6_1

P103

12505WS-04A00

MSTAR_DEBUG_OLD

1

2

3

4

5

R132

1.8K

R144 47

R110 10K

BIT2_1

R175

22

R153 10K

C120 0.1uF

R173

10K

HTPDAn_OSD_Pull_down

C123

33pF

OPT

R133

1.8K

R161 4.7K

OPT

R104 10K

BIT0_1

R152 10K

R1910

OPT

R128

1.8K

R182 10K

R143

0

R115 10K

BIT4_0

R103 10K

BIT0_0

R172

10K

HTPDAn_Video_Pull_down

R118 10K

R136

1.8K

P101

12507WS-04L

MSTAR_DEBUG_NEW

1

2

3

4

5

R125

1.8K

R108 10K

BIT1_1

C125

0.1uF

C121 0.1uF

R164 4.7K

OPT

R151 10K

C127

0.047uF

25V

R184 10K

OPT

R101 10K

OPT

R140 100 C118 0.1uF

R179

10K

U_SPI_WP_f_SoC

R102 10K

OPT

R117 10K

OPT

R170 10K

R174 0

R134

1.8K

R178

10K

OPT

R123 10K

BIT8_0

R129

1.8K

R185 10K

R160 10K

P100

12507WS-04L

DDTS_Debug

1

2

3

4

5

R126

10K

OPT

R162 4.7K

R154 10K

OPT

R145 47

R148

1.8K

IC102

AT24C256C-SSHL-T

Atmel_NVRAM

EAN61133501

3

A2

2

A1

4

GND

1

A0

5SDA

6SCL

7WP

8VCC

R106

1.8K

R165 4.7K

OPT

R159 10K

HDMI_EXT_EDID

R171 10K

OPT

R147

1.8K

R109 10K

BIT2_0

R155

4.7K

OPT

C126

33pF

OPT

R112 10K

BIT3_1

R168

0

OPT

R146

300

OPT

R131

10K

WOL_WAKE_UP

C124

1000pF

OPT

R130

1.8K

R119 10K

BIT6_0

R1800

OPT

R1870

WOL_WAKE_UP

R149 10K

C119 0.1uF

R181 10K

NON_HDMI_EXT_EDID

R169 10K

R127

1.8K

LD100

19-21/R6C-FR1S1L/3T

VBY1_LOCK_LED

Q100

2N3906S-RTK

KEC_VBY1_LOCK_LED_TR

E

B

C

L100

PZ1608U121-2R0TF

Q100-*1

MMBT3906(NXP)

NXP_VBY1_LOCK_LED_TR

E

B

C

/TU_RESET2

R195

3.3K

VBY1_LOCK_LED

R176

1K

BIT13

BIT12

R186 10K

R189 10K

R156 10K

OPT

R188 10K

OPT

BIT13

BIT12

TPO_CLK

TPO_DATA[0-7]

TPO_SOP

TPO_VAL

AR101

33

AR100

33

IC100

LGE5331(LM15U)

PWM0/GPIO157

A16

PWM1/GPIO158

C15

PWM2/GPIO159

A15

PWM3/GPIO160

B15

PWM4/GPIO161

C14

PWM_PM/GPIO10

E4

SAR0/GPIO50

H6

SAR1/GPIO51

J6

SAR2/GPIO52

G5

SAR3/GPIO53

J5

SAR5

D1

SPI_CK/GPIO1

D2

SPI_DI/GPIO2

D3

SPI_DO/GPIO3

E2

SPI_CZ0/GPIO0

F1

SPI_CZ1/GPIO_PM6/GPIO19

E3

SPI_CZ2/GPIO_PM10/GPIO23

F2

DDCA_CK/UART0_RX/GPIO11

N5

DDCA_DA/UART0_TX/GPIO12

P5

GPIO67/TX1

C9

GPIO68/RX1

A10

GPIO69/TX2

E9

GPIO70/RX2

F9

GPIO71/TX3

F10

GPIO72/RX3

G10

GPIO76/TX4

D9

GPIO77/RX4

M7

GPIO94/TX5

P6

GPIO95/RX5

N6

GPIO62

A12

GPIO63

A13

GPIO64

C12

GPIO65

B12

GPIO66

C11

GPIO73

B10

GPIO74

C10

GPIO75

B11

GPIO81/TX2

F6

GPIO82/RX2

F5

GPIO88/SCK0

K6

GPIO89/SDA0

L7

DDCR_CK/GPIO59

C16

DDCR_DA/GPIO58

B16

VID0/GPIO55

D5

VID1/GPIO56

D4

LED0/GPIO32

H4

LED1/GPIO33

H5

WOL/GPIO57

L5

LVSYNC/VBY0M AB36

LHSYNC/VBY0P AB35

LDE/VBY1M AC36

LCK/VBY1P AC37

B0M/VBY2M AD37

B0P/VBY2P AD36

B1M/VBY3M AD35

B1P/VBY3P AE36

B2M/VBY4M AF36

B2P/VBY4P AF37

BCKM/VBY5M AF35

BCKP/VBY5P AG37

B3M/VBY6M AG35

B3P/VBY6P AH36

B4M/VBY7M AH35

B4M/VBY7P AJ36

A0M/VBY_OSD_0M AJ35

A0P/VBY_OSD_0P AK37

A1M/VBY_OSD_1M AK36

A1P/VBY_OSD_1P AK35

A2M/VBY_OSD_2M AL35

A2P/VBY_OSD_2P AM36

ACKM/VBY_OSD_3M AM37

ACKP/VBY_OSD_3P AM35

A3M/LOCKN AJ33

A3P/HTPDN AJ34

A4M/OSD_LOCKN AJ32

A4P/OSD_HTPDN AJ31

GPIO_PM0/GPIO13 AD5

GPIO_PM2/GPIO15 AD6

GPIO_PM3/GPIO16 AE2

GPIO_PM4/GPIO17 AE3

GPIO_PM7/GPIO20 AF4

GPIO_PM8/GPIO21 AG5

GPIO_PM9/GPIO22 AG6

GPIO_PM13/GPIO26 AH6

GPIO_PM17/GPIO30 AJ5

GPIO_PM18/GPIO31 AJ4

GPIO_PM1/GPIO14 K5

GPIO_PM5/GPIO18 L6

GPIO_PM11/GPIO24 M5

GPIO_PM12/GPIO25 M6

AV_LNK/GPIO9 L4

TEST J15

GPIO112/SPI1_DI A18

GPIO111/SPI1_CK B18

GPIO114/SPI2_DI C17

GPIO113/SPI2_CK B17

GPIO110/VSYNC_LIKE C18

GPIO115/DIM0 D18

GPIO116/DIM1 E18

GPIO117/DIM2 F18

GPIO118/DIM3 E17

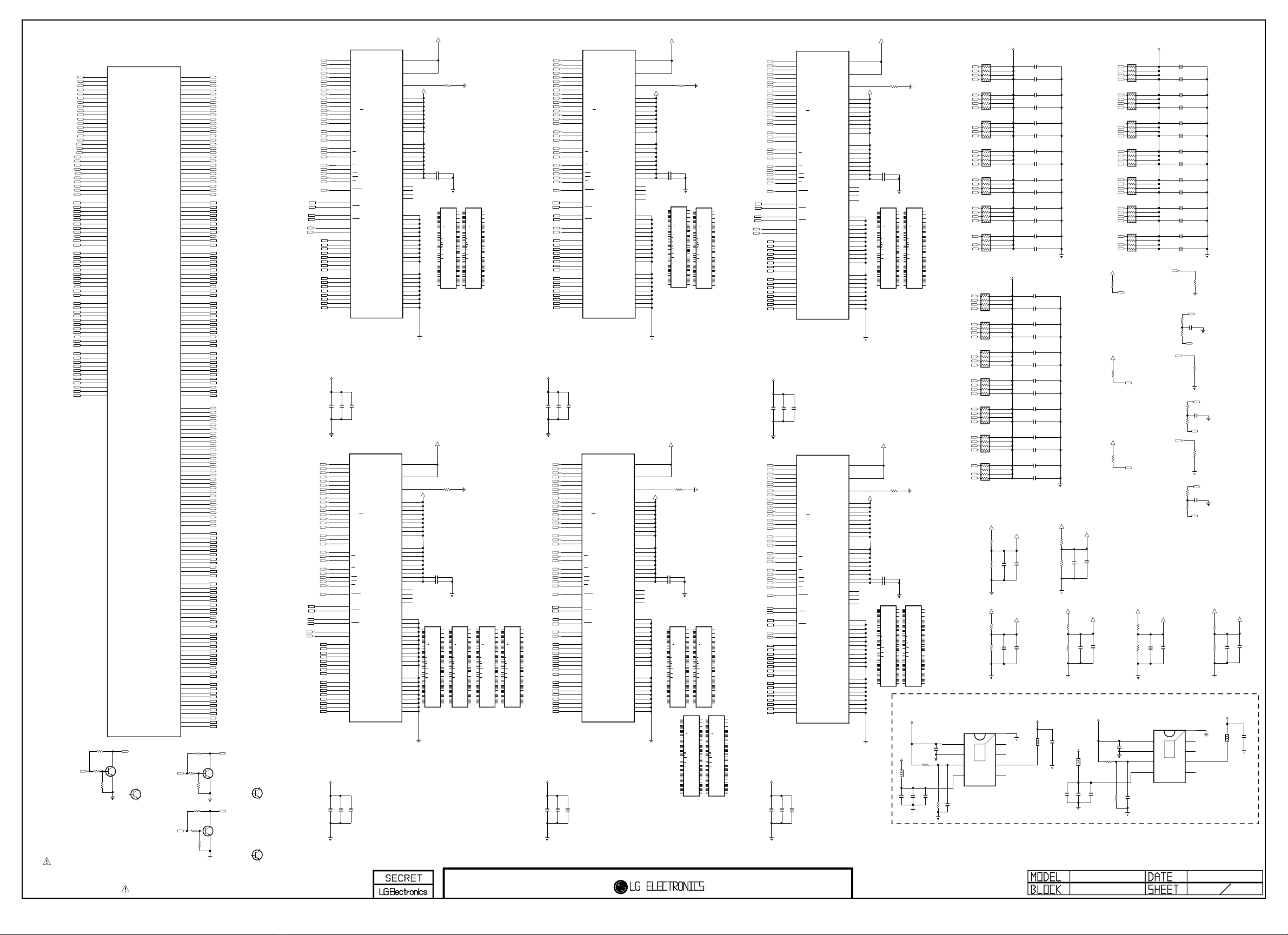

IC100

LGE5331(LM15U)

PCMDATA[0]/GPIO152

AT13

PCMDATA[1]/GPIO153

AT9

PCMDATA[2]/GPIO154

AR13

PCMDATA[3]/GPIO124

AT17

PCMDATA[4]/GPIO125

AR16

PCMDATA[5]/GPIO126

AT16

PCMDATA[6]/GPIO127

AR21

PCMDATA[7]/GPIO128

AT18

PCMADR[0]/GPIO151

AU10

PCMADR[1]/GPIO150

AT14

PCMADR[2]/GPIO148

AR10

PCMADR[3]/GPIO147

AT19

PCMADR[4]/GPIO146

AR18

PCMADR[5]/GPIO144

AU19

PCMADR[6]/GPIO143

AT11

PCMADR[7]/GPIO142

AT12

PCMADR[8]/GPIO136

AT20

PCMADR[9]/GPIO134

AU14

PCMADR[10]/GPIO130

AU16

PCMADR[11]/GPIO132

AR20

PCMADR[12]/GPIO141

AR12

PCMADR[13]/GPIO137

AU13

PCMADR[14]/GPIO138

AR19

PCMIRQA/GPIO140

AU20

PCMOEN/GPIO131

AT21

PCMIORD/GPIO133

AR15

PCMCEN/GPIO129

AU17

PCMWEN/GPIO139

AR11

PCMCD/GPIO156

AR17

PCMRST/GPIO155

AU11

PCMREG/GPIO149

AR14

PCMIOWR/GPIO135

AT15

PCMWAIT/GPIO145

AT10

NAND_ALE/GPIO194

D7

NAND_WPZ/GPIO193

F7

NAND_CEZ/EMMC_CMD/GPIO188

G7

NAND_CLE/GPIO190

E6

NAND_REZ/EMMC_CLK/GPIO191

F8

NAND_WEZ/GPIO192

E7

NAND_RBZ/EMMC_RSTN/GPIO195

E8

NAND_CEZ1/GPIO189

D6

NAND_DQS/GPIO196

D8

NAND_AD0/EMMC_D6/GPIO226

A6

NAND_AD1/EMMC_D7/GPIO225

C6

NAND_AD2/EMMC_D2/GPIO224

A7

NAND_AD3/EMMC_D1/GPIO223

B7

NAND_AD4/EMMC_D0/GPIO199

C7

NAND_AD5/EMMC_D3/GPIO198

B8

NAND_AD6/EMMC_D4/GPIO197

C8

NAND_AD7/EMMC_D5/GPIO227

B9

PCM2_CD/GPIO123

AM4

PCM2_CE/GPIO119

AP4

PCM2_IRQA/GPIO120

AL5

PCM2_WAIT/GPIO121

AN4

PCM2_RESET/GPIO122

AL4

TS1DATA_[0]/GPIO187 AL6

TS1DATA_[1]/GPIO186 AM6

TS1DATA_[2]/GPIO185 AP8

TS1DATA_[3]/GPIO184 AN7

TS1DATA_[4]/GPIO183 AM5

TS1DATA_[5]/GPIO182 AM7

TS1DATA_[6]/GPIO181 AN5

TS1DATA_[7]/GPIO180 AN6

TS1CLK/GPIO177 AL7

TS1VALID/GPIO179 AP5

TS1SYNC/GPIO178 AP6

TS0DATA_[0]/GPIO166 AP10

TS0DATA_[1]/GPIO167 AN10

TS0DATA_[2]/GPIO168 AM8

TS0DATA_[3]/GPIO169 AM10

TS0DATA_[4]/GPIO170 AM11

TS0DATA_[5]/GPIO171 AM12

TS0DATA_[6]/GPIO172 AN8

TS0DATA_[7]/GPIO173 AM9

TS0CLK/GPIO176 AN11

TS0VALID/GPIO174 AN9

TS0SYNC/GPIO175 AP9

TS2DATA_[0]/GPIO200 AM14

TS2DATA_[1]/GPIO204 AP15

TS2DATA_[2]/GPIO205 AN12

TS2DATA_[3]/GPIO206 AN15

TS2DATA_[4]/GPIO207 AN14

TS2DATA_[5]/GPIO208 AM16

TS2DATA_[6]/GPIO209 AN13

TS2DATA_[7]/VSENSE/GPIO210 AM15

TS2CLK/GPIO203 AP13

TS2VALID/GPIO201 AP12

TS2SYNC/GPIO202 AM13

TS3DATA_[0]/GPIO211 AM18

TS3DATA_[1]/GPIO212 AP16

TS3DATA_[2]/GPIO213 AM19

TS3DATA_[3]/GPIO214 AN18

TS3DATA_[4]/GPIO215 AP19

TS3DATA_[5]/GPIO216 AN20

TS3DATA_[6]/GPIO217 AP18

TS3DATA_[7]/GPIO218 AN19

TS3CLK/GPIO221 AN17

TS3VALID/GPIO219 AM17

TS3SYNC/GPIO220 AN16

VIFP AP1

VIFM AP2

SIFP AN2

SIFM AN1

IF_AGC AP3

TGPIO0/GPIO162 AR2

TGPIO1/GPIO163 AM2

TGPIO2/GPIO164 AK5

TGPIO3/GPIO165 AK6

URSA_RESET_SoC

T2

UHD

NVRAM

4_Division

RS232C_Debug

11

T ATSC

11

Mstart Debug

High

ANALOG SIF

Default

DVB

I2C PULL UP

BIT6

BR/PH

OLEDLCD

I2C for tuner&LNB

FOR HDMI2.0

BR

Division

BIT11

I2C for LCD Module

01

Display

CN/HK

ISDB INT

T2/C PIP

11

T2/C/S2

Default

CHIP CONFIG

00

20140701 version

JP

LM15U HW Option

NON_EXTERNAL

BIT5

Close to MSTAR

TW/COL

LM15U only

ISDB PIPDefault

Low

Model

I2C for tuner

JP

DDTS_Debug

High

T2/C PIP

I2C for Micom

KR

Value Mode Description

4’b1000 SB51_ExtSPI 51 boot from SPI

4’b1001 HEMCU_ExtSPI ARM boot from SPI

4’b1010 HEMCU_ROM_EMMC ARM boot from ROM; outer storage is eMMC

4’b1011 HEMCU_ROM_NAND ARM boot from ROM; outer storage is NAND

4’b1100 DBUS for test only

4’b0000 SB51_ExtSPI + Authentication 51 boot from SPI with ARM authentication

4’b0001 SB51_ExtSPI + Authentication HEMCU_ExtSPI + Authentication

4’b0011 HEMCU_ROM_NAND + Authentication ARM boot from ROM with authentication;

00

T2/C/S2 PIP

CN/HKBIT(2/3)

LM15U+URSA

BIT10

URSA11

BIT(0/1)

EXTERNAL

Write Protection

- Low : Normal Operation

- High : Write Protection

BIT9

EU/CIS

10

DTV_IF

EU

ISDB EXT

North.AM

CI+

Sri Lanka

01

Support

NONE

JP

AJJA

I2C for URSA9 (URSA9 Only)

GPIO PULL UP

KR

ATSC NIM+T2

T2/C/S2

10

TW/COL

Resolution

01

BIT(7/8)

AJJA

ATSC

A0’h

T/C

NON_Division

CHIP_CONFIG[3:0]

{LED1, SPI_DI,LED0, PWM_PM}

T/C

I2C for NAVRAM

URSA11-P

Close to MSTAR

FHD

BIT4

T2/C

10

I2C for Main Amp / Woofer AMP

EXTERNAL EDID

URSA9

00

Low

V-BY-ONE

B/E(FRC)

ATSC+T2

US

LM15U+URSA9

ATSC PIP

OLED LM15U_ONLY

BIT12

BIT13

New CI PathOld CI Path

VID VID Enable VID Disable

Reserved

Copyright © 2015 LG Electronics. Inc. All rights reserved.

Only for training and service purposes