- 9 - LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Only for training and service purposes

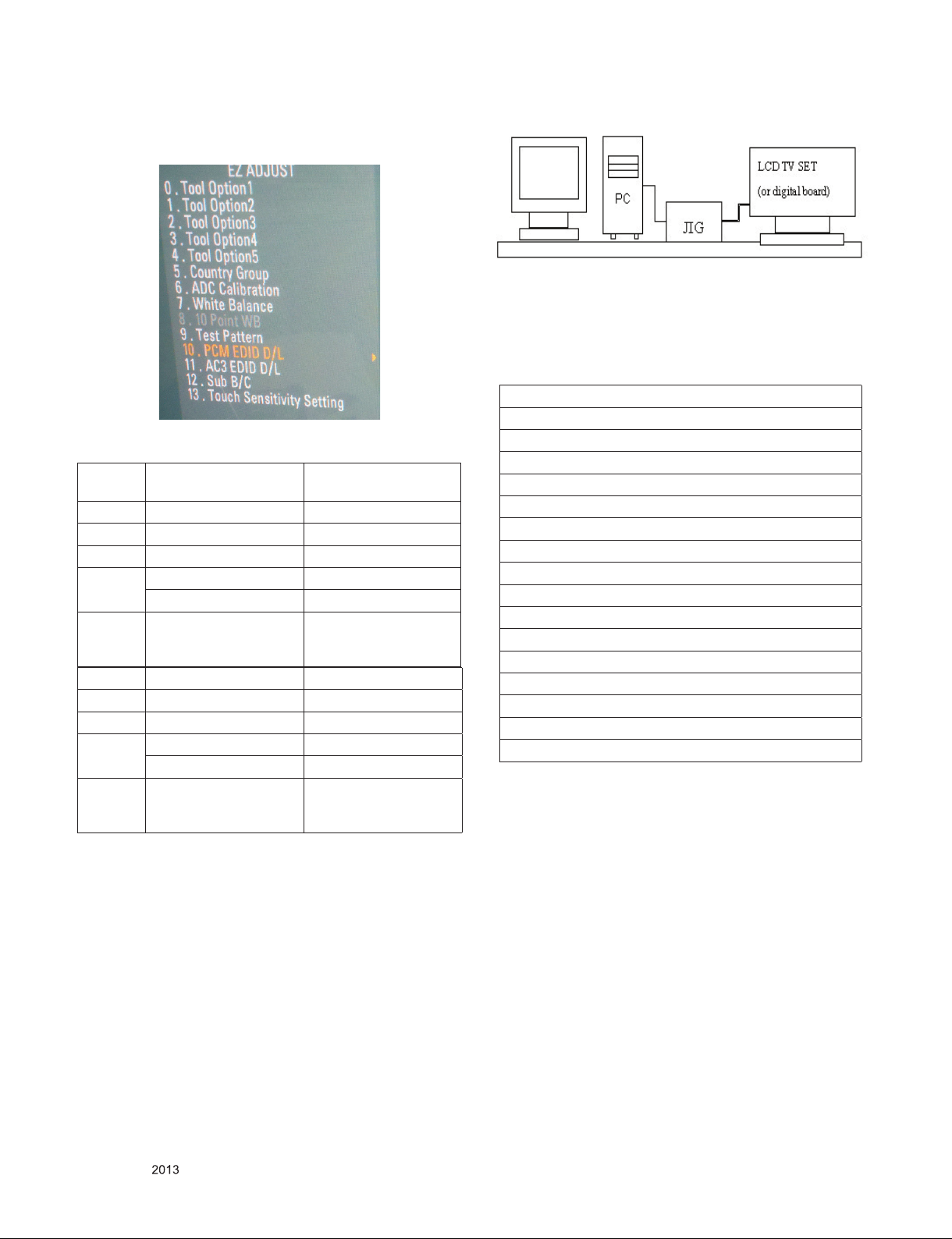

■ White Balance Adjustment

If you can’t adjust with inner pattern, then you can adjust

it using HDMI pattern. You can select option at “Ez-Adjust

Menu – 7. White Balance” there items “NONE, INNER,

HDMI”. It is normally setting at inner basically. If you can’t

adjust using inner pattern you can select HDMI item, and

you can adjust.

In manual Adjust case, if you press ADJ button of service

remocon, and enter “Ez-Adjust Menu – 7. White Balance”,

then automatically inner pattern operates. (In case of

“Inner” originally “Test-Pattern. On” will be selected in The

“Test-Pattern. On/Off”.

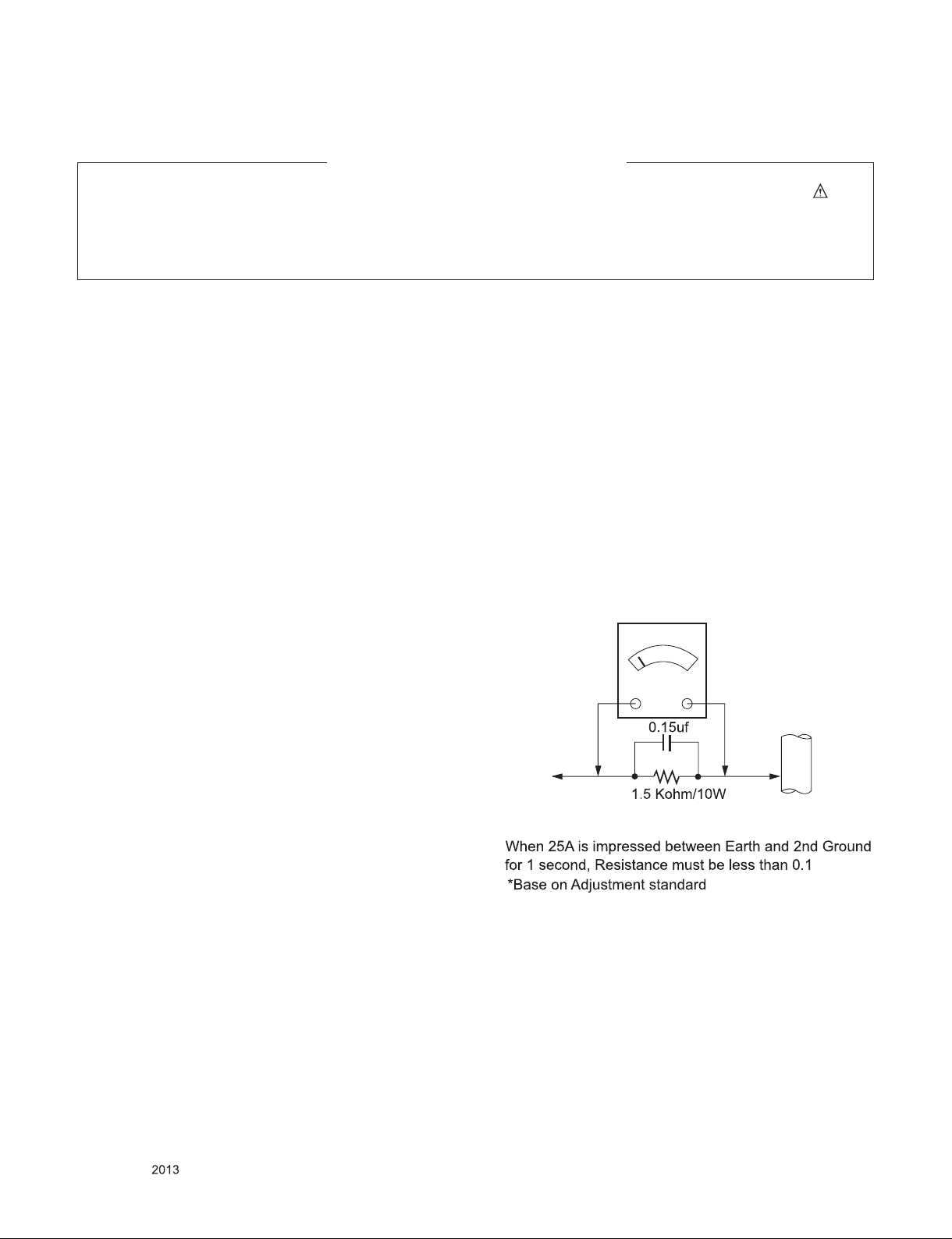

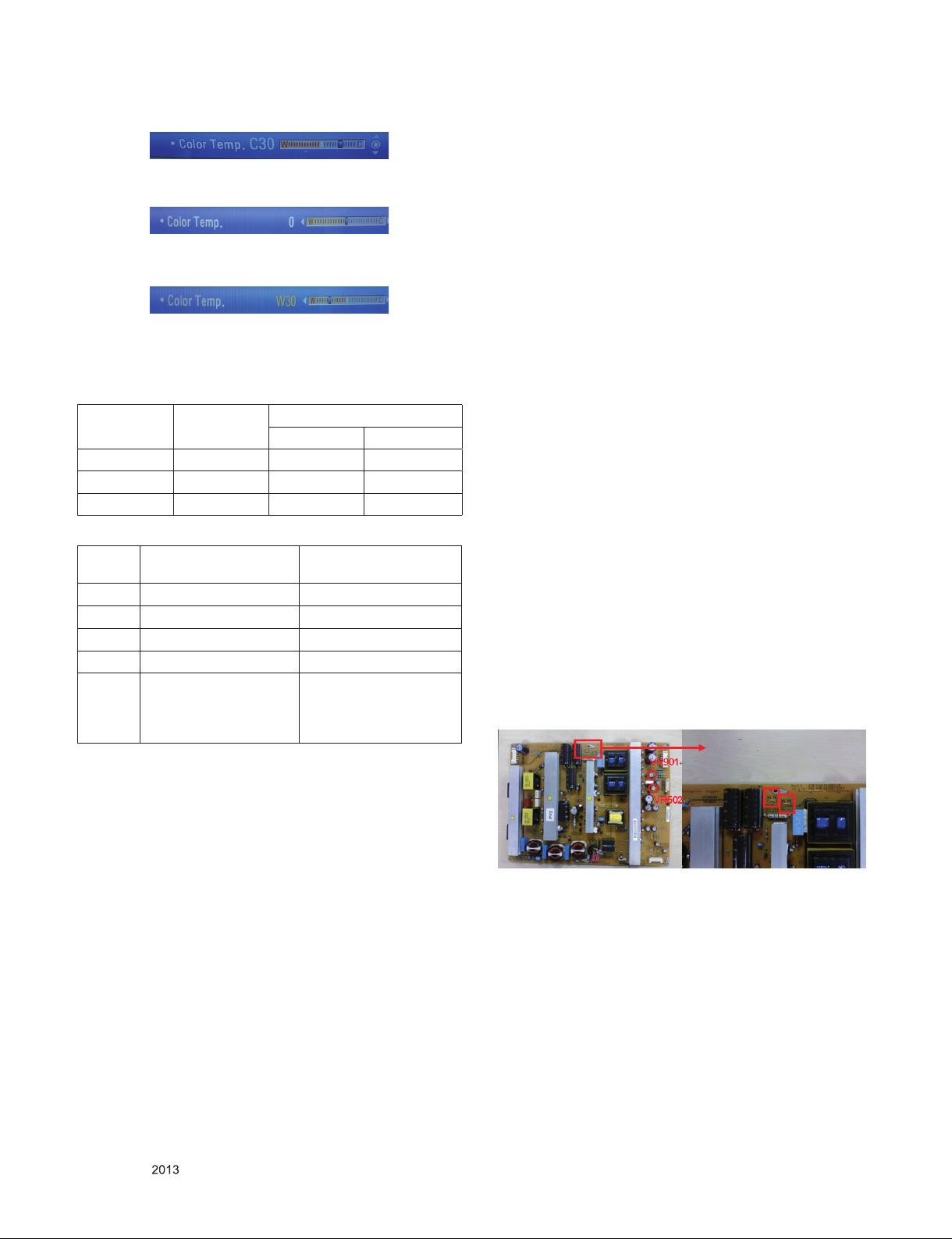

● Connect all cables and equipments like Pic.5)

● Set Baud Rate of RS-232C to 115200. It may set 115200

orignally.

● Connect RS-232C cable to set

● Connect HDMI cable to set

■ RS-232C Command (Commonly apply)

● “wb 00 00”: Start Auto-adjustment of white balance.

● “wb 00 10”: Start Gain Adjustment (Inner pattern)

● “jb 00 c0” :

● …

● “wb 00 1f”: End of Adjustment

* If it needs, offset adjustment (wb 00 20-start, wb 00 2f-

end)

● “wb 00 ff”: End of white balance adjustment (inner pattern

disappear)

■Adjustment Mapping information

● When Color temperature (White balance) Adjustment

(Automatically)

- Press “Power only key” of service remocon and operate

automatically adjustment.

- Set BaudRate to 115200.

● You must start “wb 00 00” and finish it “wb 00 ff”.

● If it needs, then adjustment “Offset”.

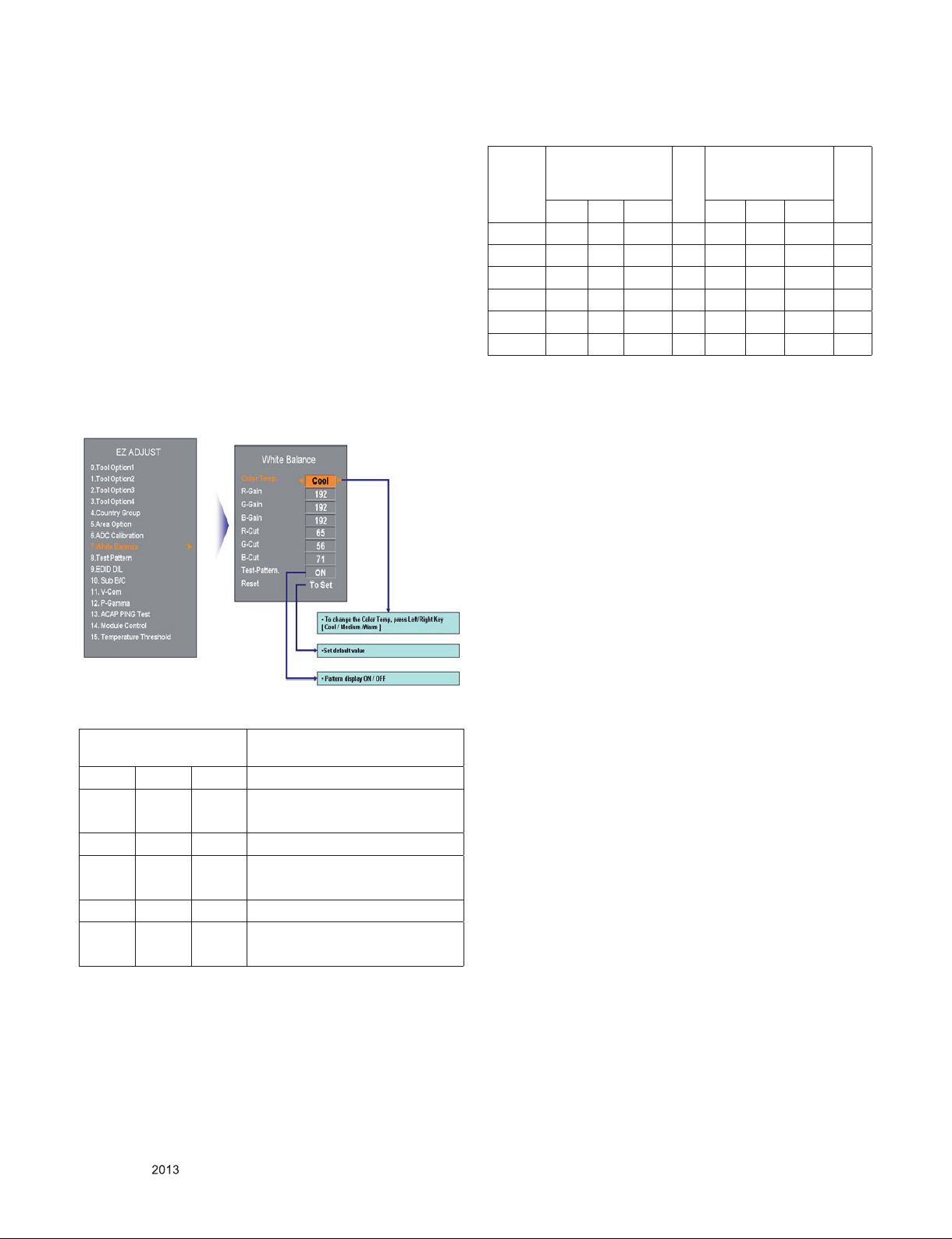

■ White Balance Adjustment (Manual adjustment)

● Test Equipment: CA-210

- Using PDP color temperature, Color Analyzer (CA-210)

must use CH 10, which Matrix compensated (White, Red,

Green, Blue compensation) with CS-2100. See the

Coordination bellowed one.

● Manual adjustment sequence is like bellowed one.

- Turn to “Ez-Adjust” mode with press ADJ button of service

remocon.

- Select “10.Test Pattern” with CH+/- button and press

enter. Then set will go on Heat-run mode. Over 30

minutes set let on Heat-run mode.

- Let CA-210 to zero calibration and must has gap more

10cm from center of PDP module when adjustment.

- Press “ADJ” button of service remocon and select

“7.White-Balance” in “Ez-Adjust” then press “►” button of

navigation key. (When press “►” button then set will go to

full white mode)

- Adjust at three mode (Cool, Medium, Warm)

- If “cool” mode

Let B-Gain to 192 and R, G, B-Cut to 64 and then control

R, G gain adjustment High Light adjustment.

- If “Medium” and “Warm” mode Let R-Gain to 192 and R,

G, B-Cut to 64 and then control G, B gain adjustment

High Light adjustment.

- All of the three mode

Let R-Gain to 192 and R, G, B-Cut to 64 and then control

G, B gain adjustment High Light adjustment.

- With volume button (+/-) you can adjust.

- After all adjustment finished, with Enter (■ key) turn to

Ez-Adjust mode. Then with ADJ button, exit from

adjustment mode

* Attachment: White Balance adjustment coordination and

color temperature.

● Using CS-1000 Equipment.

- COOL : T=11000K, ∆uv=0.000, x=0.276 y=0.283

- MEDIUM : T=9300K, ∆uv=0.000, x=0.285 y=0.293

- WARM : T=6500K, ∆uv=0.000, x=0.313 y=0.329

RS-232C

COMMAND

[CMD ID DATA]

M

I

N

CENTER

(DEFAULT)

M

A

X

Cool Mid Warm Cool Mid Warm

R Gain jg Ja jd 00 184 192 192 192

G Gain jh Jb je 00 187 183 159 192

B Gain ji Jc jf 00 192 161 95 192

R Cut 64 64 64 127

G Cut 64 64 64 127

B Cut 64 64 64 127

RS-232C COMMAND

[CMD ID DATA]

Meaning

wb 00 00 White Balance adjustment start.

wb 00 10 Start of adjust gain

(Inner white pattern)

wb 00 1f End of gain adjust

wb 00 20 Start of offset adjust

(Inner white pattern)

wb 00 2f End of offset adjust

wb 00 ff End of White Balance adjust

(Inner pattern disappeared)