Microchip Technology dsPIC33F Family User manual

Other Microchip Technology Media Converter manuals

Microchip Technology

Microchip Technology MCP1640 User manual

Microchip Technology

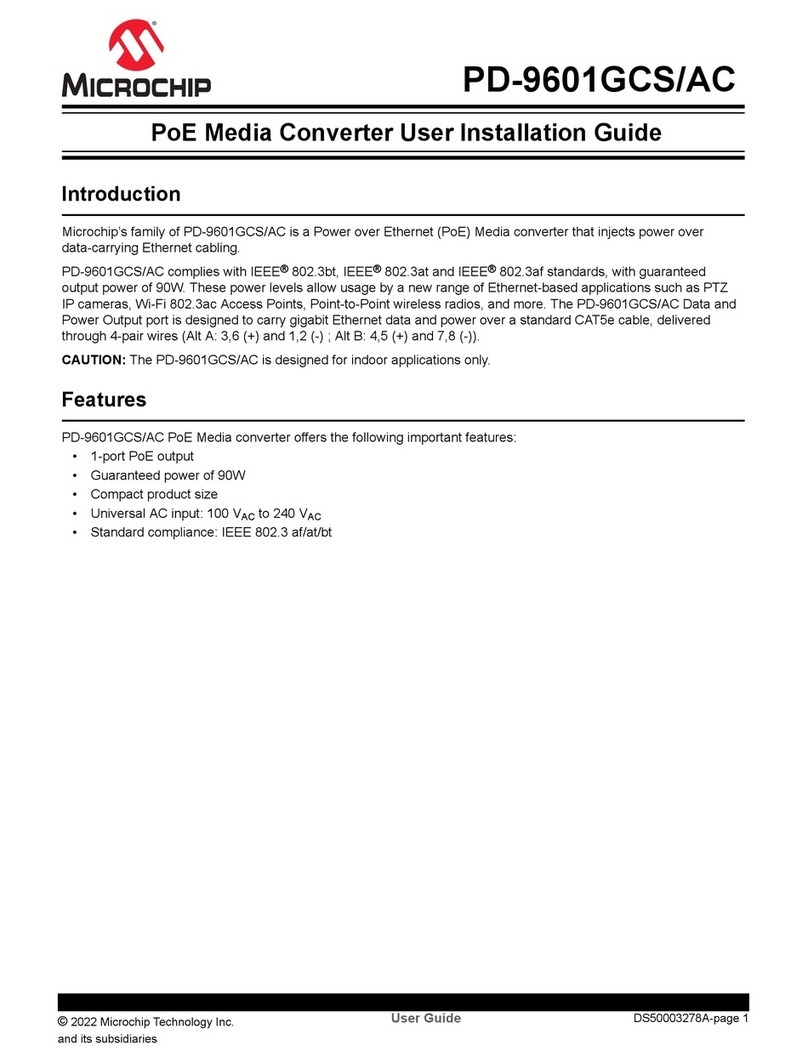

Microchip Technology PD-9601GCS/AC Troubleshooting guide

Microchip Technology

Microchip Technology KEELOQ HCS300 User manual

Microchip Technology

Microchip Technology Audio Digital-to-Analog Converter User manual

Microchip Technology

Microchip Technology KEELOQ HCS300 User manual

Microchip Technology

Microchip Technology MCP2120 User manual

Microchip Technology

Microchip Technology MCP4921 User manual

Microchip Technology

Microchip Technology TB3209 User manual

Microchip Technology

Microchip Technology TC7129 Operating and maintenance instructions

Microchip Technology

Microchip Technology MCP1630 NiMH User manual

Microchip Technology

Microchip Technology MCP1661 Guide

Microchip Technology

Microchip Technology TC110 User manual

Microchip Technology

Microchip Technology MCP16301 User manual

Microchip Technology

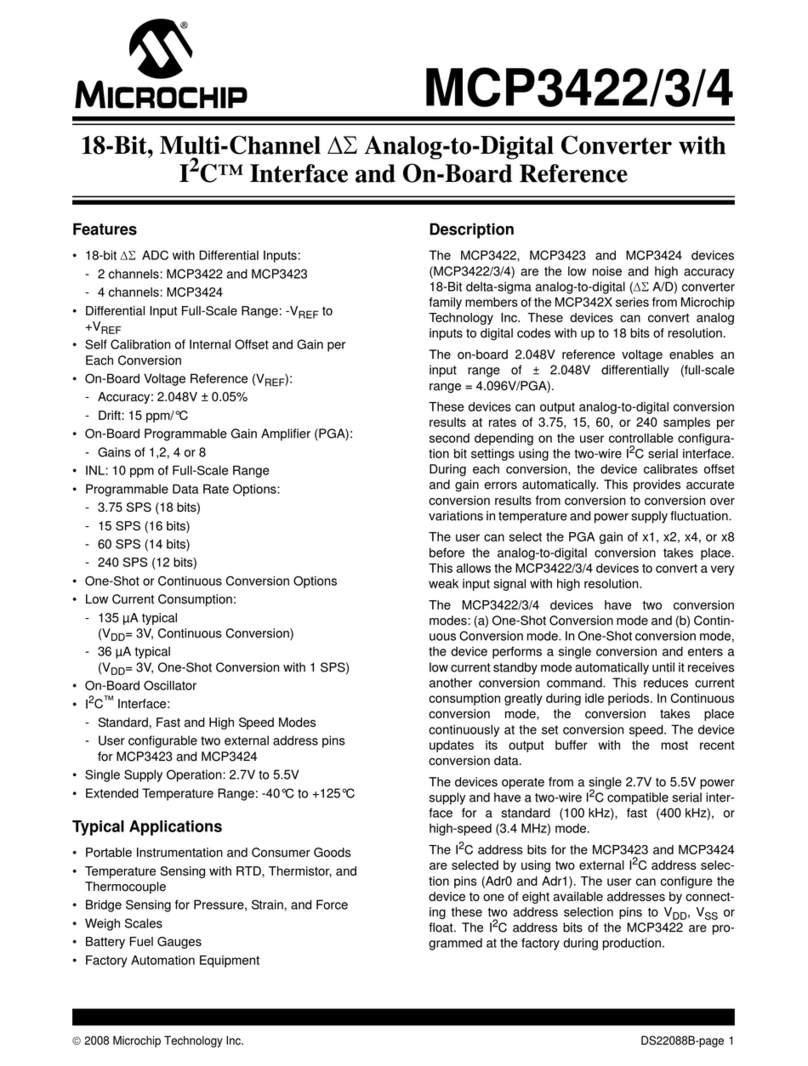

Microchip Technology MCP3422 User manual

Microchip Technology

Microchip Technology MCP1630 NiMH User manual

Microchip Technology

Microchip Technology TC1047A User manual

Microchip Technology

Microchip Technology MCP16251 Guide

Microchip Technology

Microchip Technology MCP19111 User manual

Microchip Technology

Microchip Technology PIC32 Family User manual

Microchip Technology

Microchip Technology PIC24F User manual