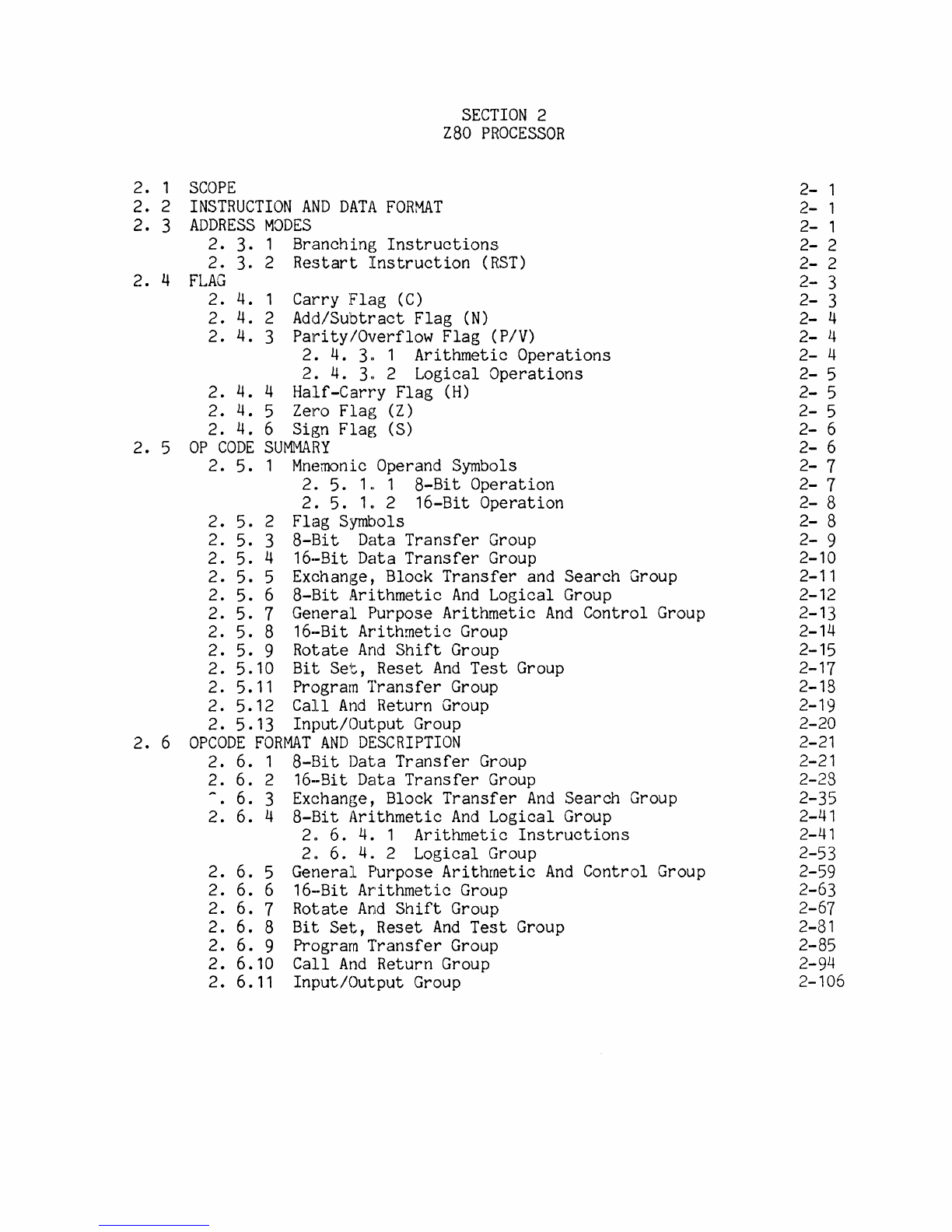

SECTION

5

SERIAL

I/O

INTERFACE

5. 1

SCOPE

5-

1

5. 2

CONFIGURING

THE

SERIAL

I/O

PORT

5-

1

5. 2. 1 Terminal/Communication Configuration

5-

1

5. 2. 2 Programmable

Timer

Configuration

5-

1

5. 2. 2. 1

BAUD

Rate Configuration

5-

5

5. 2. 3 Clock Configurations

5-

5

5. 2. 4

EIA

RS·-232-C

Configuration

5-

6

5. 2. 5

TTL

Conflguration

5-

6

5. 2. 6 Current.

Loop

Operation

5-

1

5. 2. 1

Interrupt

Configuration

5-

1

5. 3

PROGRAMMING

THE

SERIAL

I/O

INTERFACE

5-

9

5. 3. 1

Initialization

5-

9

5. 3. 2 Clock Set

5-

9

5.

3.

3 Control

~lord

Programming

5-

9

5

..

3. 3. 1

Mode

Instruction

5-11

5.

3.

3. 2

Command

Instruction

5-11

5. 3. 4

Status

Word

Format 5-13

5

..

3. 4. 1

Parity

Error 5-13

5. 3. 4. 2 Overrun Error 5-14

5

..

3. 4. 3 Framing Error 5-14

5. 4

DATA

COMMUNICATION

5-14

5. 4. 1

Asynchl"onous

Transmission 5-14

5. 4. 2 Asynchronous Receive 5-14

5.

4. 3 Synchronous Transmission 5-15

5. 4. 4 Synchronous

Rece

i

ve

5-15

5. 5

TIMER

INTERFACE

5-17

5.5.

1

JJJode

Definitions

5-18

5

..

5. 1. 1

HODE

0 -

Interrupt

On

Tenninal Count 5-19

5..

5.

1. 2

MODE

1 - Progralmnable

One

Shot 5-20

5. 5. 1. 3

MODE

2 - Rate Generator 5-21

5. 5. 1. 4

MODE

3 - Square

Wave

Generator 5-22

5.

5.

1. 5

MODE

4 - Software Triggered Strobe 5-23

5. 5. 1. 6

MODE

5 - Hardware Trigger Strobe 5-24

5. 5. 2

On-The--FlY

Readout 5-25

5. 5. 3

BAUD

Rate Generator 5-25

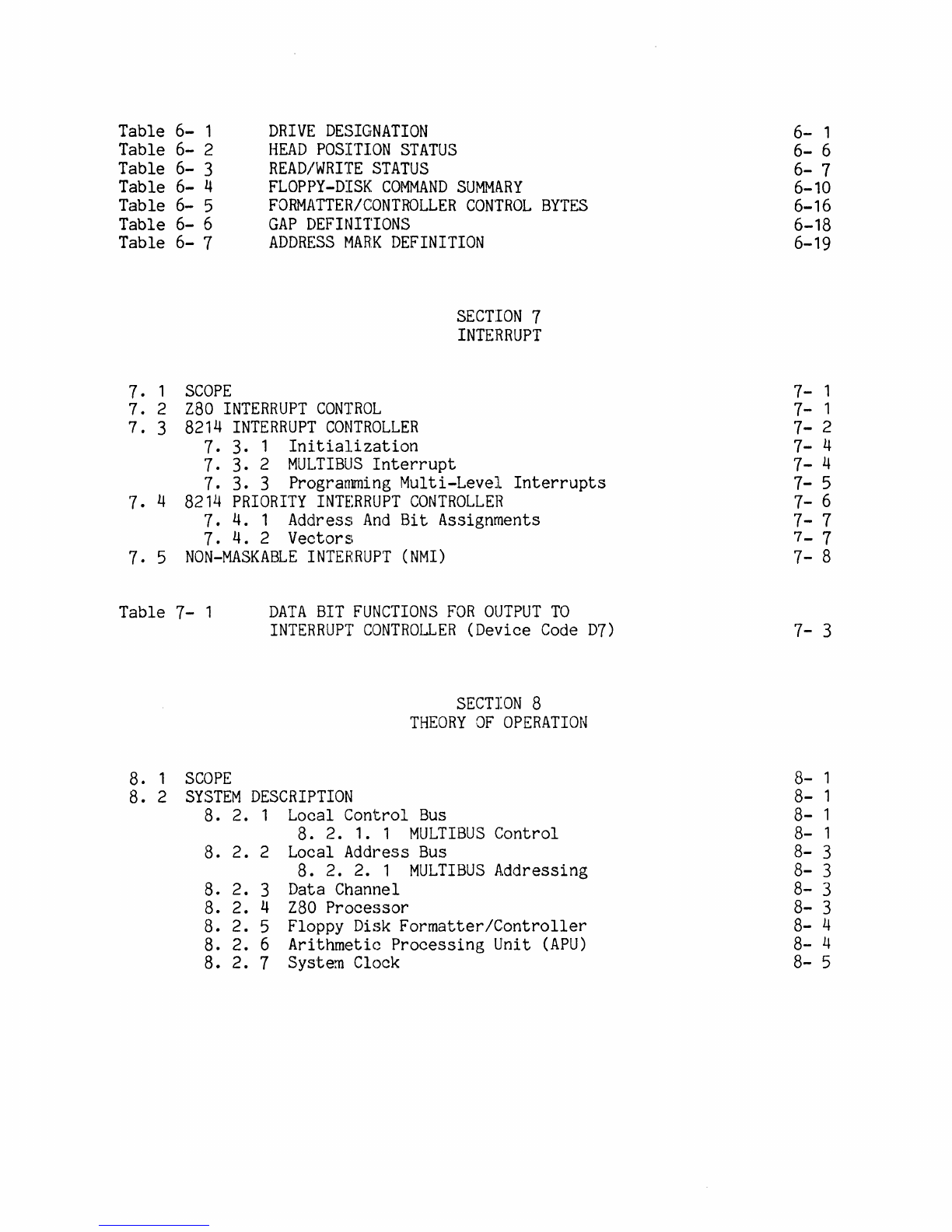

Figure

5-

Figure 5- 2

Figure

5-

3

Figure 5- 4

Figure

5-

5

Figure

5-

6

Figure

5-

1

Figure 5- 8

Figure

5-

9

Figure 5-10

Figure 5-11

Figure 5-12

Figure 5-13

CONTROL

WORD

SEQUENCE

MODE

INSTRUCTION

CONTROL

WORD

FORMAT

COMMAND

INSTRUCTION

CONTROL

WORD

FORMAT

STATUS

WORD

FORMAT

SYNC

CHARACTER

TRANSMISSION

8253

INTERVAL

TIMER

CONTROL

WORD

FORMAT

MODE

0

TIMING

DIAGRAM

MODE

1

TIMING

DIAGRAIJJ

MODE

2

TIMING

DIAGRAM

MODE

3

TIMING

DIAGRAM

MODE

4

TllV1ING

DIAGRAM

MODE

5

TIMING

DIAGRAM

BAUD

RATE

GENERATOR

ROUTINE

5- 8

5-10

5-12

5-13

5-16

5-17

5-19

5-20

5-21

5-22

5-23

5-24

5-26