National Semiconductor LMK03000C User manual

Other National Semiconductor Evaluation Board manuals

Popular Evaluation Board manuals by other brands

Microchip Technology

Microchip Technology SOT23-3 user guide

Texas Instruments

Texas Instruments DIR9001 user guide

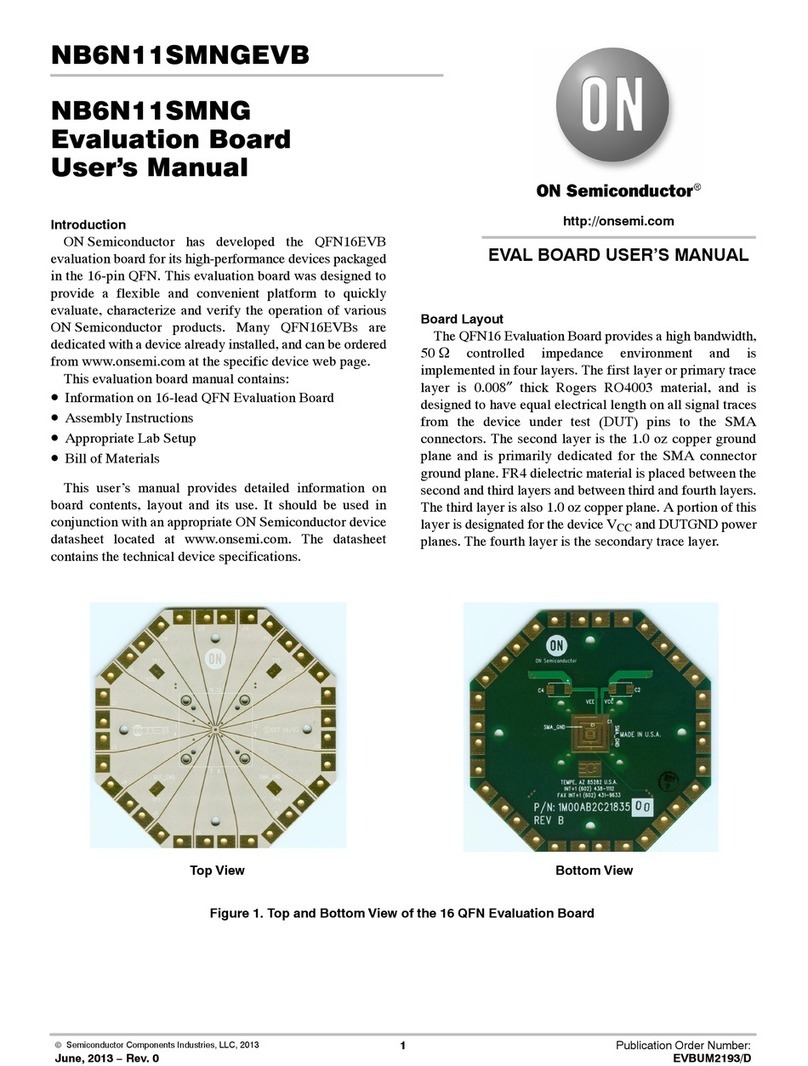

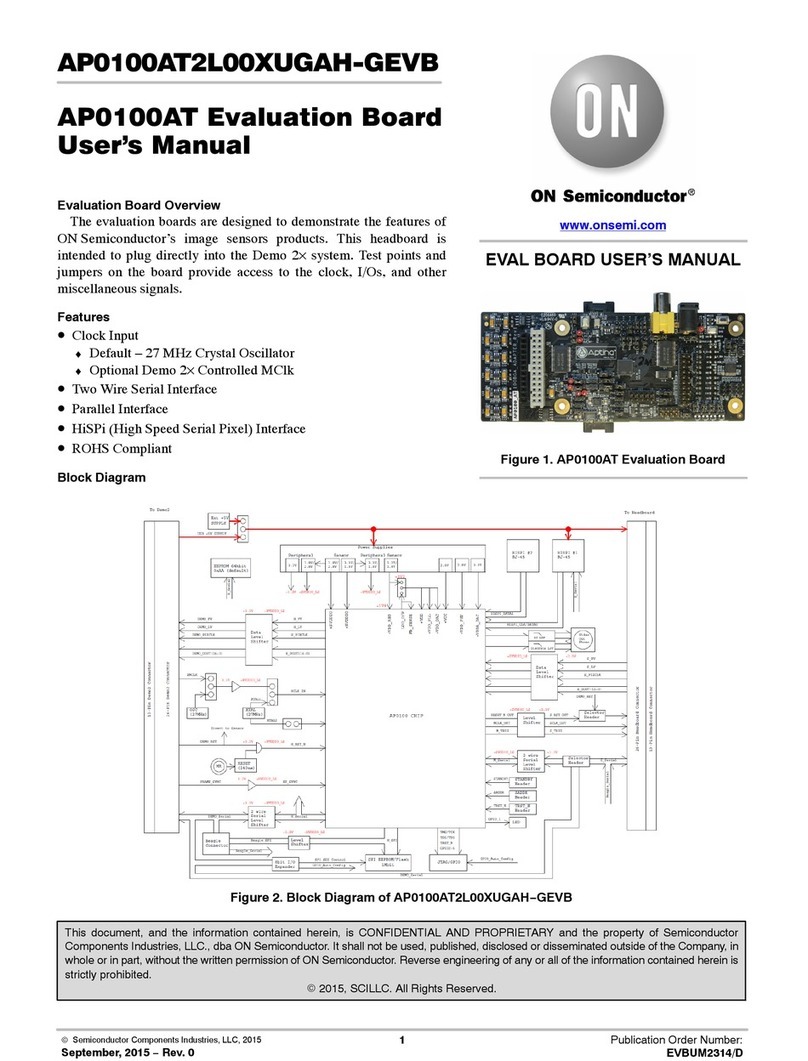

ON Semiconductor

ON Semiconductor AP0100AT2L00XUGAH-GEVB user manual

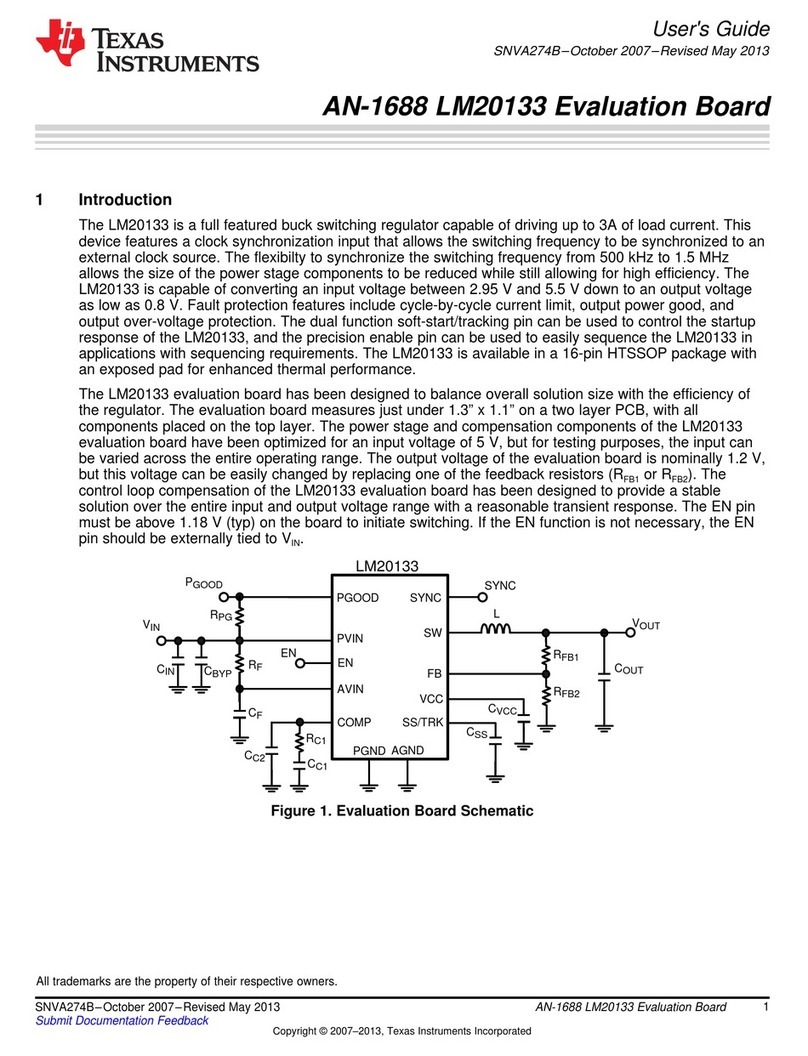

Texas Instruments

Texas Instruments LM20133 user guide

Texas Instruments

Texas Instruments PGA308 user guide

Fujitsu

Fujitsu SK-96380-120PMC user guide

Texas Instruments

Texas Instruments TPS79801DCQEVM-434 user guide

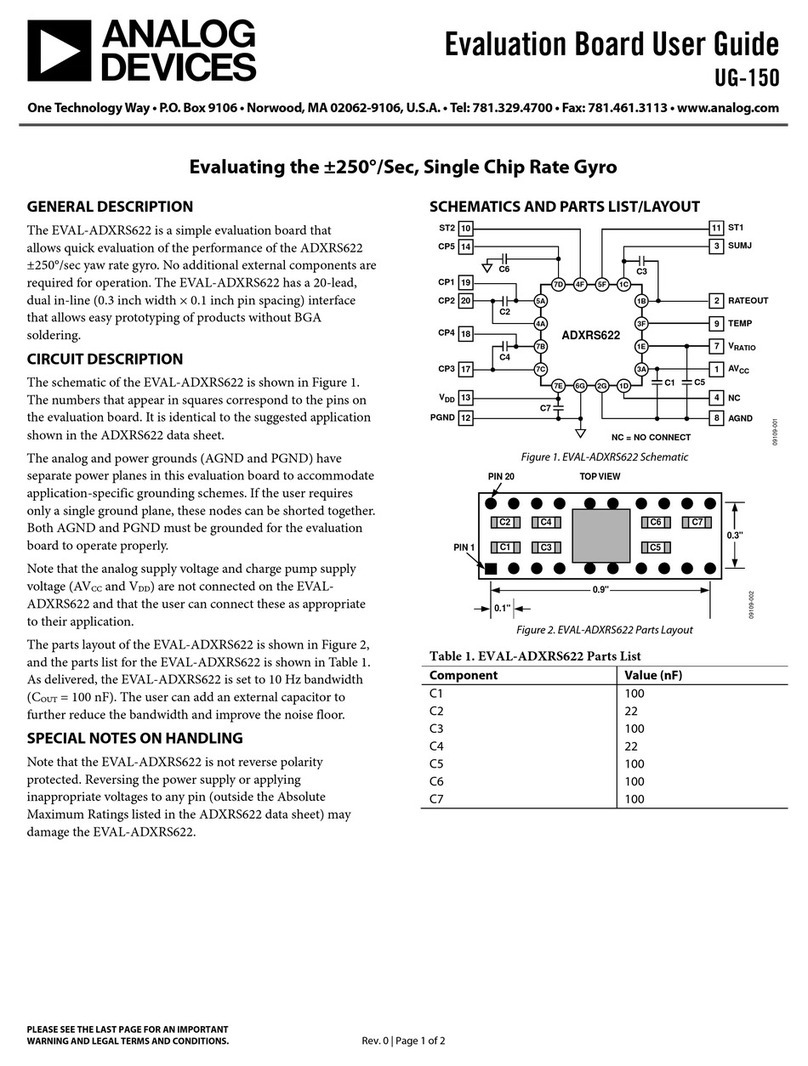

Analog Devices

Analog Devices UG-102 user guide

Texas Instruments

Texas Instruments TPD1E04U04 user guide

Analog Devices

Analog Devices ADA4432-1BCP-EBZ user guide

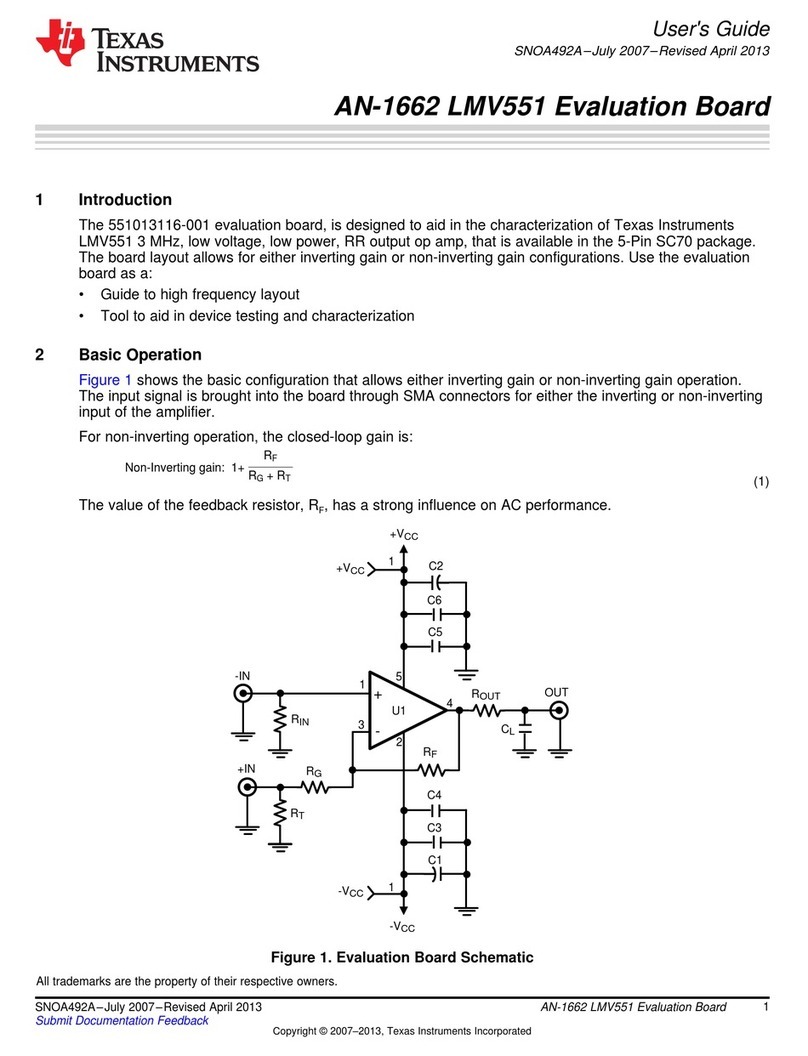

Texas Instruments

Texas Instruments AN-1662 LMV551 user guide

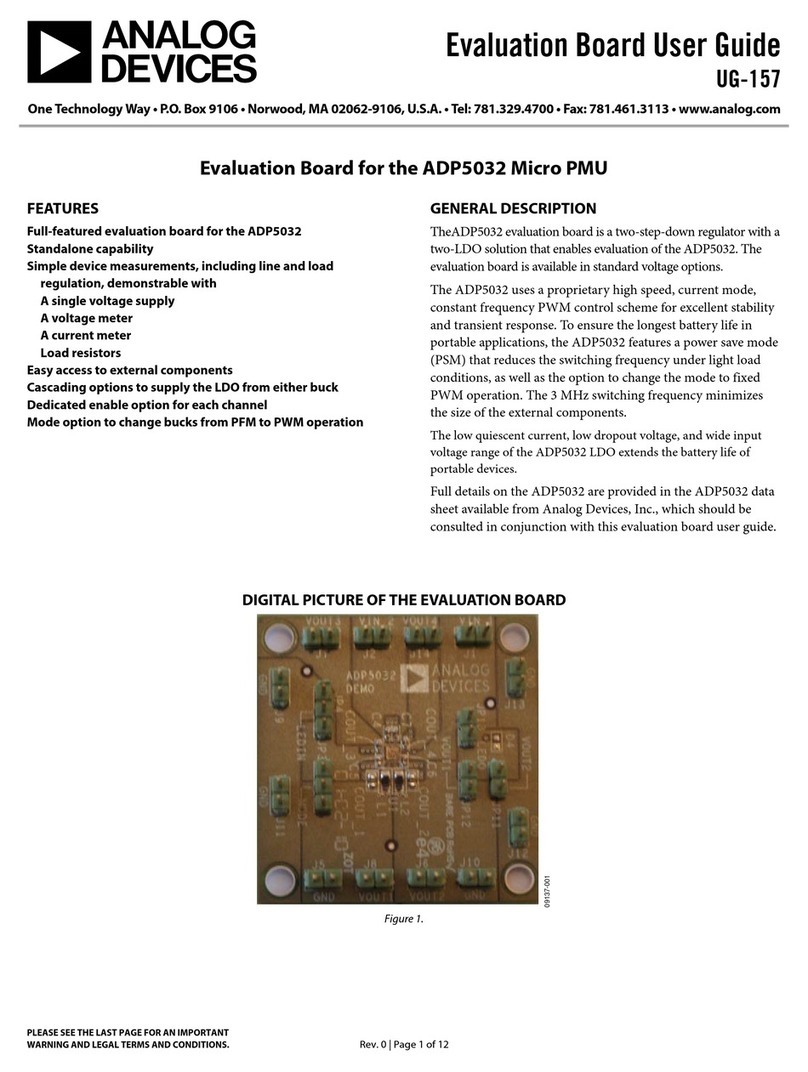

Analog Devices

Analog Devices UG-157 user guide