7

This only applies to games which were originally made for the NES itself. Many developers

have produced games since which have been released freely on the Internet. Downloading

these is acceptable. As for original NES games, using them will remain illegal until either the

developers grant permission for their use or the copyright expires, which is 75 years after

they were made.

Nintendo are very much against emulation. The company acted against the developers of

UltraHLE [24], an emulator for their Nintendo 64 console, which they claimed violated

copyright. Nintendo’s objection was understandable as the console was still in use when

UltraHLE was released. The presence of Nintendo 64 emulators represented a threat to

Nintendo’s income however, many believe that the law should make an exception for

systems which are no longer in production and from which Nintendo no longer make any

money. Despite emulation’s ability to keep old games alive Nintendo refuse to release the

copyright on old games so their use remains illegal.

For more information on the legal issues of emulation, the reader is directed to Nintendo’s

own FAQ on the subject [25]. This is highly biased and ignores the legal uses of emulation.

For a detailed response and clarification on this, the reader should look at [26].

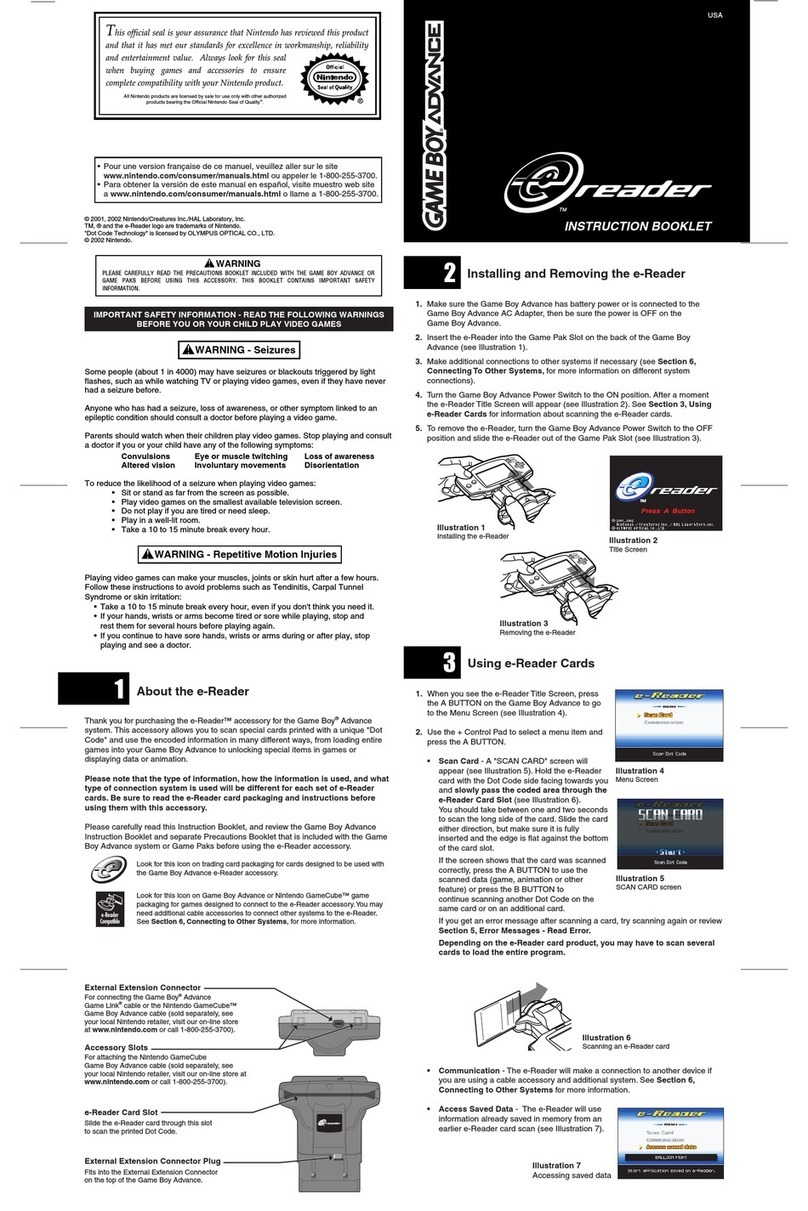

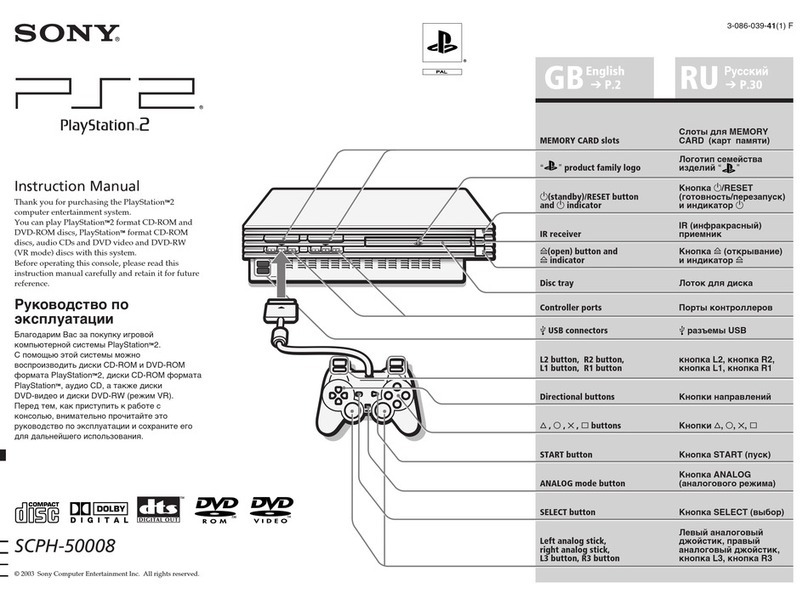

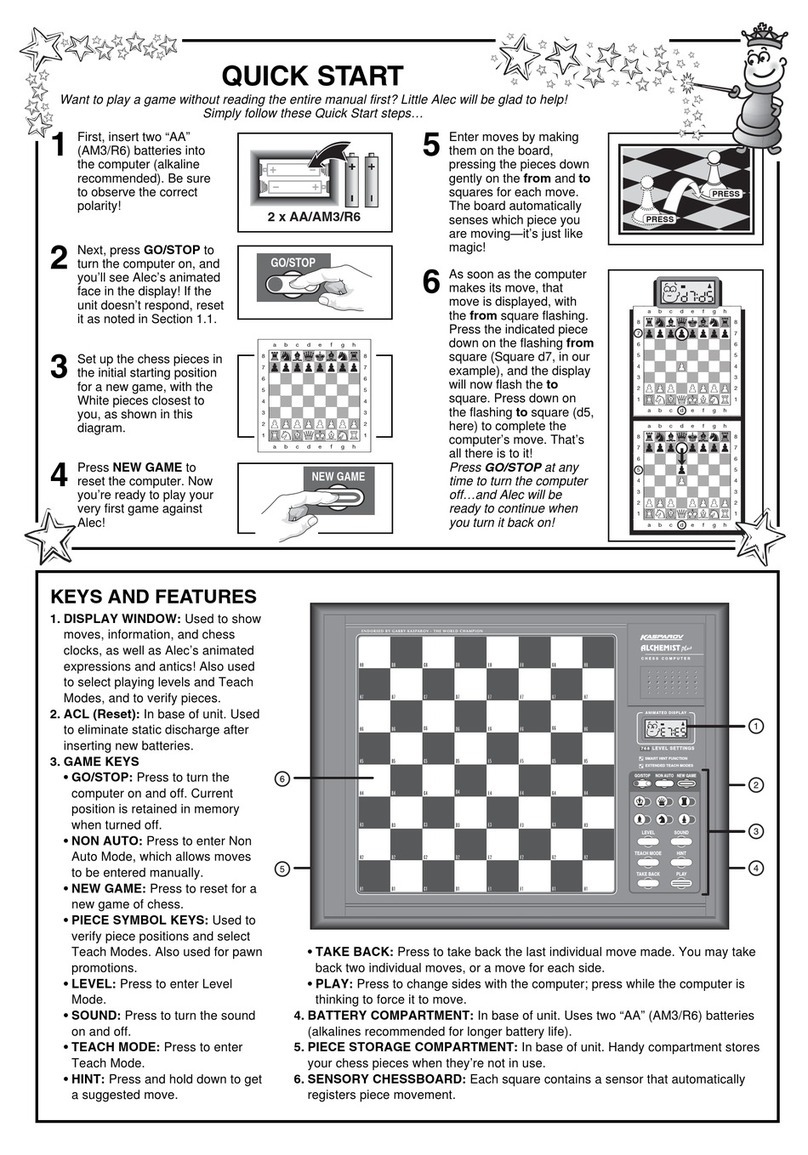

1.5 NES Hardware Overview

Hiroshi Yamauchi’s instructions to

design a console which would be

cheaper than the competition resulted in

Nintendo deciding to use an outdated

Central Processing Unit (CPU).

Although a 16-bit processor would have

coped with ease, to keep the price low

they decided to use a variant of the 8-bit

6502 processor, developed by MOS

technology in 1975. The chip would be

sufficient to run the programs but would

be unable to generate the graphics

required so the company decided to use

a second chip as a dedicated Picture

Processing Unit (PPU), responsible for

calculating and displaying the graphics.

Figure 1-4 shows the top of the

motherboard with the CPU and PPU

indicated.

Nintendo designed the basic features required from the chips but found it difficult to find a

company willing to produce such highly customised chips for the low price they were looking

for. Ricoh agreed to manufacture the chips after Nintendo guaranteed them a three-million

chip order. By the end of 1986 Nintendo was Ricoh’s largest customer, accounting for

between 60 and 70 percent of the company’s semiconductor sales [10]. The functionality of

the CPU is discussed in Part 2, that of the PPU is discussed in Part 3.

Both chips feature their own internal memory, in the form of RAM. Games were usually

stored on ROM chips within the game cartridges, which could be accessed by the CPU when

the cartridges where inserted into the system. The hardware used for games is discussed in

Part 4.

The NES used memory mapped I/O to allow the processor to communicate with the other

components, the PPU and the input devices. Memory mapped I/O is a technique where data

PPU CPU

Figure 1-4. The NES motherboard [27].