14579-040 (PXIe System)

R1.5, January 2021 I

1 Safety ....................................................................................................................... 1

1.1 Safety Symbols used in this document.............................................................................. 1

1.2 General Safety Precautions ............................................................................................... 1

1.3 References and Architecture Specifications...................................................................... 2

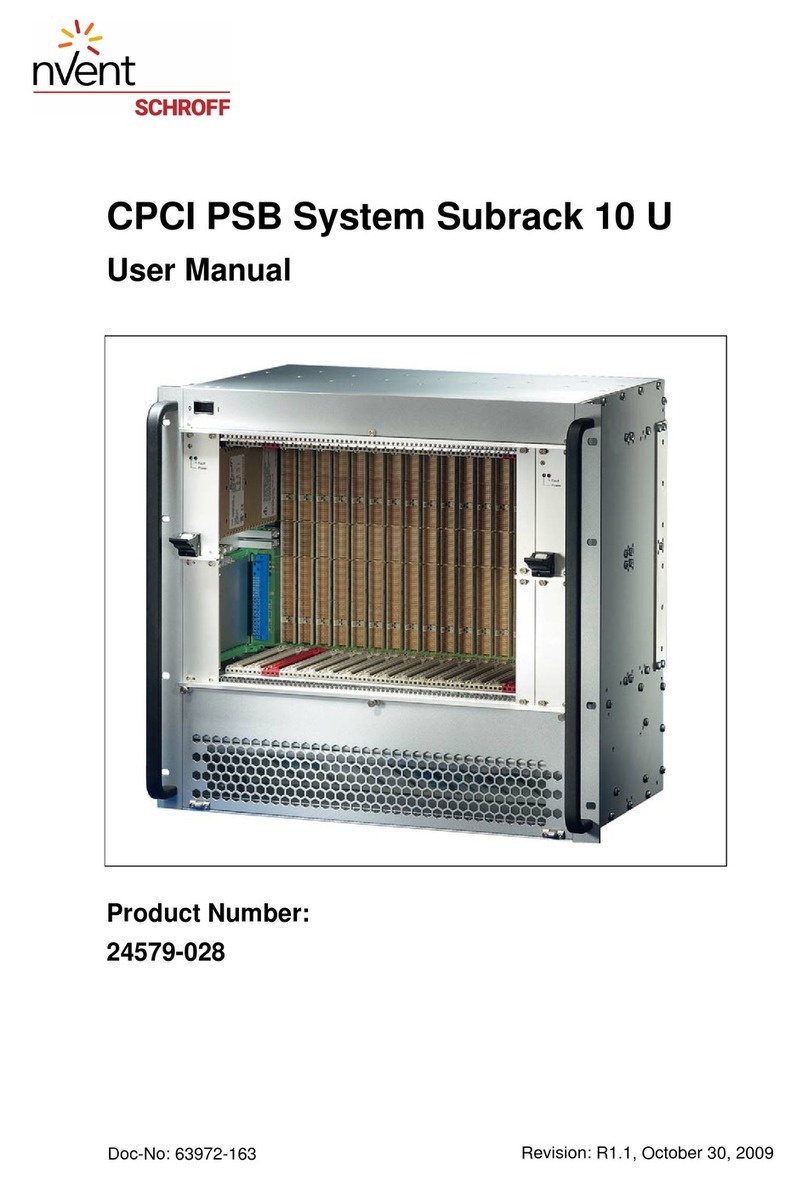

2 Product Overview ..................................................................................................... 3

2.1 Key features ...................................................................................................................... 3

2.2 System Overview............................................................................................................... 4

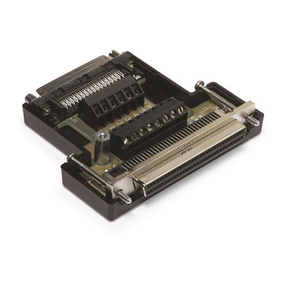

3 18 Slot PXIe Backplane (23007-518) .......................................................................... 5

3.1 Backplane Topology .......................................................................................................... 6

3.2 PCIe-to-PCI bridge ............................................................................................................. 7

3.3 PCIe Switch........................................................................................................................ 7

3.4 System Synchronisation Clocks ......................................................................................... 8

3.4.1 Clock specifications............................................................................................ 9

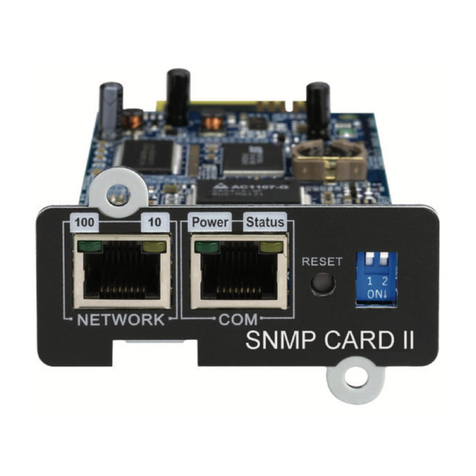

3.5 Schroff PXIe Chassis Management Module (CMM) ........................................................ 10

3.5.1 Chassis status LED............................................................................................ 11

3.6 PXI Trigger Bus ................................................................................................................ 12

3.7 Power Supply................................................................................................................... 13

3.7.1 Available electrical power................................................................................ 14

3.7.2 Per slot power.................................................................................................. 15

3.7.3 Grounding/Earthing ......................................................................................... 15

3.8 Power-on behaviour........................................................................................................ 16

3.9 Voltage monitoring ......................................................................................................... 16

4 Cooling ................................................................................................................... 17

4.1 Temperature Settings...................................................................................................... 18

4.1.1 Maximum cooling ............................................................................................ 18

5 System Controller ................................................................................................... 19

5.1 Fan Speed and Trigger Bridge settings ............................................................................ 20

5.2 General Installation Guidelines ....................................................................................... 21

5.2.1 Unpacking ........................................................................................................ 21

5.2.2 Ensuring Proper Airflow................................................................................... 21

5.3 Initial Operation .............................................................................................................. 21

6 Service.................................................................................................................... 22

6.1 Technical support and Return for Service Assistance ..................................................... 22

6.2 Scope of Delivery............................................................................................................. 23

6.3 Accessories...................................................................................................................... 23

6.4 Spare Parts ...................................................................................................................... 23

7 Technical Data ........................................................................................................ 24

8 Dimensions............................................................................................................. 25