Copyright Notice

Copyright 1994 Ocean Information Systems,Inc.

All rights reserved.

Ocean Information Systems,Inc.

688 Arrow Grand Circle

Covina,CA 91722

Printed in theHong Kong

All of the information contained in this manualis copyrighted and all rights reserved. No part of this

document, in whole or in part, may be reproduced or copied in any form without prior consent in writing

from Ocean Information Systems,Inc.

_____________________________________________________________________________________

Limited Warranty

Buyer agrees that if this product hasany defects,Ocean Information Systems, Inc. (OISI) is only obligated

to replace or refund the purchaseprice for a period of one yearfrom date of purchase. OISI is not liable for

any loss, direct or indirect, that may be incurred as a result of any defects. The warranty does not cover any

loss or damage caused by shipping, improper installation or maintenance, or any repairs made by anyone

other than an authorized Ocean service center.

_____________________________________________________________________________________

Limitations of Liability

While the information in this manual has been carefully reviewed and is believed to be accurate, OISI

assumesno responsibility in the event that any inaccuraciesare found. In no event shallOISI be held liable

for any loss or expenses whether directly or indirectly caused by the support materials provided with this

product. It is further acknowledged that OISI is under no obligation to update the manualor to notify

purchasersof any forthcomingupdates.

_____________________________________________________________________________________

Trademarks

AMD is a registered trademark of Advanced Micro Devices

AMI is a trademark of American Megatrend,Inc.

Fasmath is a registered trademark of Cyrix Corporation

Intel i386, i486, i486SX, i486DX, i486DX2 and Intelare registered trademarksof IntelCorporation.

MS-DOS, Xenix, Windows and Microsoft are registered trademarks of Microsoft Corporation.

MR BIOS is a trademark of Microid Research, Inc.

Novell is a registered trademark of Novell, Inc.

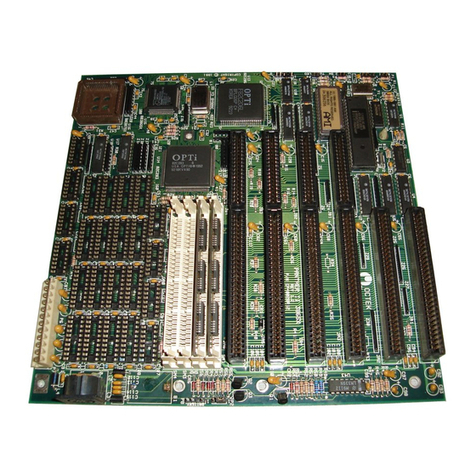

Octek is a registered trademark of Ocean Information Systems,Inc.

OPTi is a registered trademark of OPTi Inc.

Unix is a registered trademark of American Telephone and Telegraph Company Bell Laboratories.

VESA and VL-Bus are registered trademarks of Video Electronic Standard Association.

XT, AT, PS/2, OS/2, & IBM are registered trademarksof InternationalBusiness MachinesCorporation.

All other brand and product namesmentioned in this manualare trademarks orcopyrights of their

respective holders.