MachOne™

Integrated PCI Audio Processor

OPTi®

912-3000-042 Page 1

Revision: 1.0

The information contained within this document is subject to change without notice. OPTi Inc. reserves the right to make changes in this manual at any time as well as in the products it

describes, at any time without notice or obligation. OPTi Inc. assumes no responsibility for any errors contained within. In no event will OPTi Inc. be liable for any damages, direct, indirect, inci-

dental or consequential resulting from any error, defect, or omission in this specification. OPTi and OPTi Inc. are registered trademarks of OPTi Inc. OPTiFM is a trademark of OPTi Inc. All

other trademarks and copyrights are the property of their respective holders. Copyright © 1997 OPTi Inc.

1.0 Overview

The OPTi MachOne™ is a single chip PCI audio processor

that taps the power and performance of the 132MB/sec PCI

bus without sacrificing essential legacy support for the huge

installed base of Sound Blaster™ compatible applications.

With strict adherence to ISA 1.0 and PCI 2.1 PnP standards,

the MachOne delivers the highest assurance of system and

operating system compatibility. The MachOne is ideal for

desktop, notebook, mobile, and embedded applications

requiring a high level of integration and uncompromising

sound quality.

The MachOne’s PCI bus master interface ensures extremely

low system overhead for audio data transfers, freeing the use

of system memory for downloadable MIDI patchsets or

Microsoft DirectMusic™ samples. By utilizing both 3V and

5V, the MachOne delivers the optimal balance between

power consumption and performance.

Hi-Fidelity

OPTi’s third-generation 16-bit Sigma-Delta codec provides

high quality analog-to-digital and digital-to-analog conver-

sions. The Sigma Delta codec is integrated with a low distor-

tion complex mixer and a 3D stereo expander which

dramatically enhances the audio experience with only stan-

dard speakers. Digital audio output provides support for digi-

tal speakers or external mixers, and a General Purpose I/O

port is provided for external audio controllers.

In addition to the 20 OPTiFM™ voices, the MachOne archi-

tecture provides powerful audio software enhancements,

including wavetable, and 3D positioning acceleration—mak-

ing the MachOne an ideal gaming platform. The Digital Game

Port Timer improves overall system performance by offload-

ing from the CPU.

Expandability

The MachOne is an ideal building block for advanced audio

solutions. The MPU-401 port supports external MIDI devices,

such as keyboards. Two sets of asynchronous I/O ports sup-

port Zoom Video, hardware wavetable, speaker phone, Digi-

tal CD-In, DSP data and more.

Mobile Application

The MachOne supports both ACPI and APM which makes it

an ideal audio solution for mobile applications. The MachOne

supports the industry-standard AC-LINK; an ideal docking

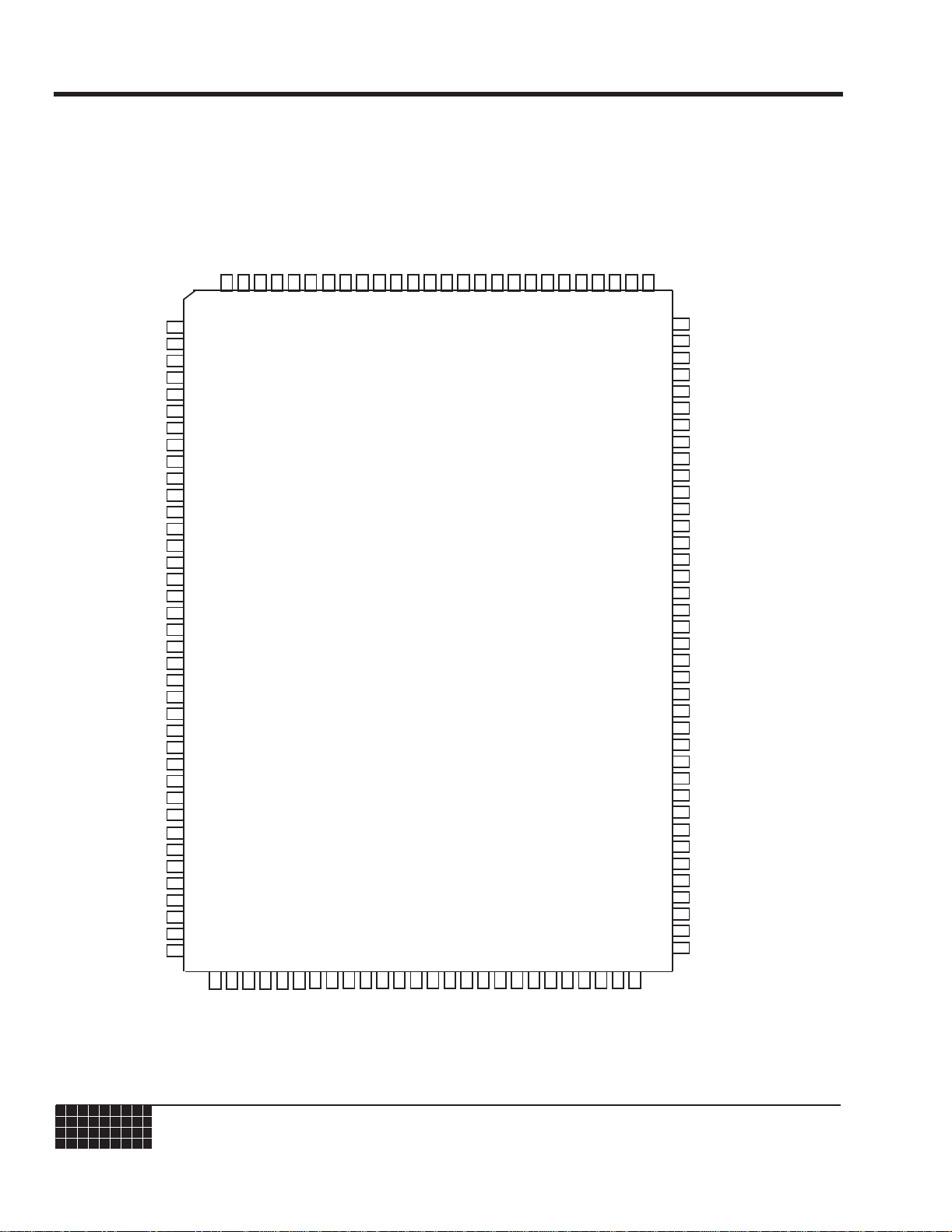

station interface. The small audio footprint of the MachOne

128-pin LQFP package saves valuable real estate which is

prized in space constrained notebook designs.

Integration

The high level of integration of the MachOne eliminates the

requirement for additional memory, codecs, 3D, and other

discrete components. This minimizes the design effort as well

as the total cost of design implementation.

The combination of PCI, outstanding legacy SB Pro Compati-

bility, smallest audio footprint, and Notebook optimization

extensions make the MachOne the ideal audio solution for

desktop, notebook, mobile, and embedded applications

requiring a high level of integration and uncompromising

sound quality.

2.0 Features

• 32-bit PCI Bus Master, PCI 2.1 compliant.

• Integrated sound controller compatible with Sound Blaster

(SB) Pro, Ad Lib, and Microsoft Windows Sound System

(WSS).

• SB Pro/ WSS Compatibility

- Support distributed DMA, virtual DMA with stream scat-

ter/gather buffer control.

- Support Serial IRQ and Drive-back IRQ.

• Support stream scatter/gather buffer to improve PCI bus

bandwidth.

• ISA 1.0 and PCI 2.1 Plug and Play compatible.

• Built-in AC-97 compatible Codec.

• Supports optional external AC-97 Codec through

AC-LINK.

• Full duplex operation: Record and playback simulta-

neously.

• Support IMA ADPCM, µ-Law, A-Law decompression.

• High-quality 20-voice, 52-operator, enhanced OPTiFM

music synthesizer.

• Built-in 16-bit Sigma-Delta Stereo codec.

• Built-in 7-channel mixer: 5 stereo channels and 2 mono

channels.

• 64-step master volume control.

• QSound 3D Sound Enhancement.

• Integrated MIDI UART with FIFO for both input and output

with MPU-401 interface.

• Integrated dual game port with Digital Game Port Inter-

face.