Warning

FOR YOUR SAFETY PLEASE READ THE FOLLOWING TEXT CAREFULLY

This appliance

is

supplied with a moulded three pin mains plug for your safety and conve-

nience.

A 3

amp

fuse

is

fitted in this plug.

Should thefuse need to be replaced please ensure that

the

replacement fuse has a rating of

3

amps

and that it

is

approved by ASTA

or

BSI

to

BS1362.

Check for the ASTA

mark~

or

the

BSI

mark~

on

the

body of the fuse.

Ifthe plug contains a removable fuse cover you must ensure that

it

is

refitted when the fuse

is

replaced.

Ifyou lose the fuse cover the plug must not be used until a replacement cover

is

obtained.

A replacement fuse cover can be purchased from your local Panasonic Dealer.

IF

THE FITTED MOULDED PLUG

IS

UNSUITABLE FOR THE SOCKET OUTLET

IN

YOUR HOME THEN THE FUSE SHOULD

BE

REMOVED AND THE PLUG CUT OFF

AND DISPOSED OF SAFELY.

THERE

IS

A DANGER

OF

SEVERE ELECTRICAL SHOCK

IF

THE CUT OFF PLUG

IS

INSERTED INTO ANY

13

AMP SOCKET.

Ifa new plug

is

to be fitted please observe

the

wiring code as shown below.

Ifin any doubt please consult a qualified electrician.

Important

The

wires in this mains lead are coloured

in

accordance with the following code:

Blue: Neutral

Brown: Live

As the colours of thewires in the mains lead of this appliance may not correspond with

the

coloured markings identifying the terminals in your plug, proceed as follows:

The

wire which

is

coloured BLUE must be connected to

the

terminal in the plug which

is

marked with the letter N

or

coloured BLACK.

The

wire which

is

coloured BROWN must be connected

to

the terminal in the plug which

is

marked with the letter L

or

coloured RED.

Under no circumstances should either of these wires be connected to the earth terminal of

the three pin plug, marked with the letter E

or

the Earth Symbol

~

.

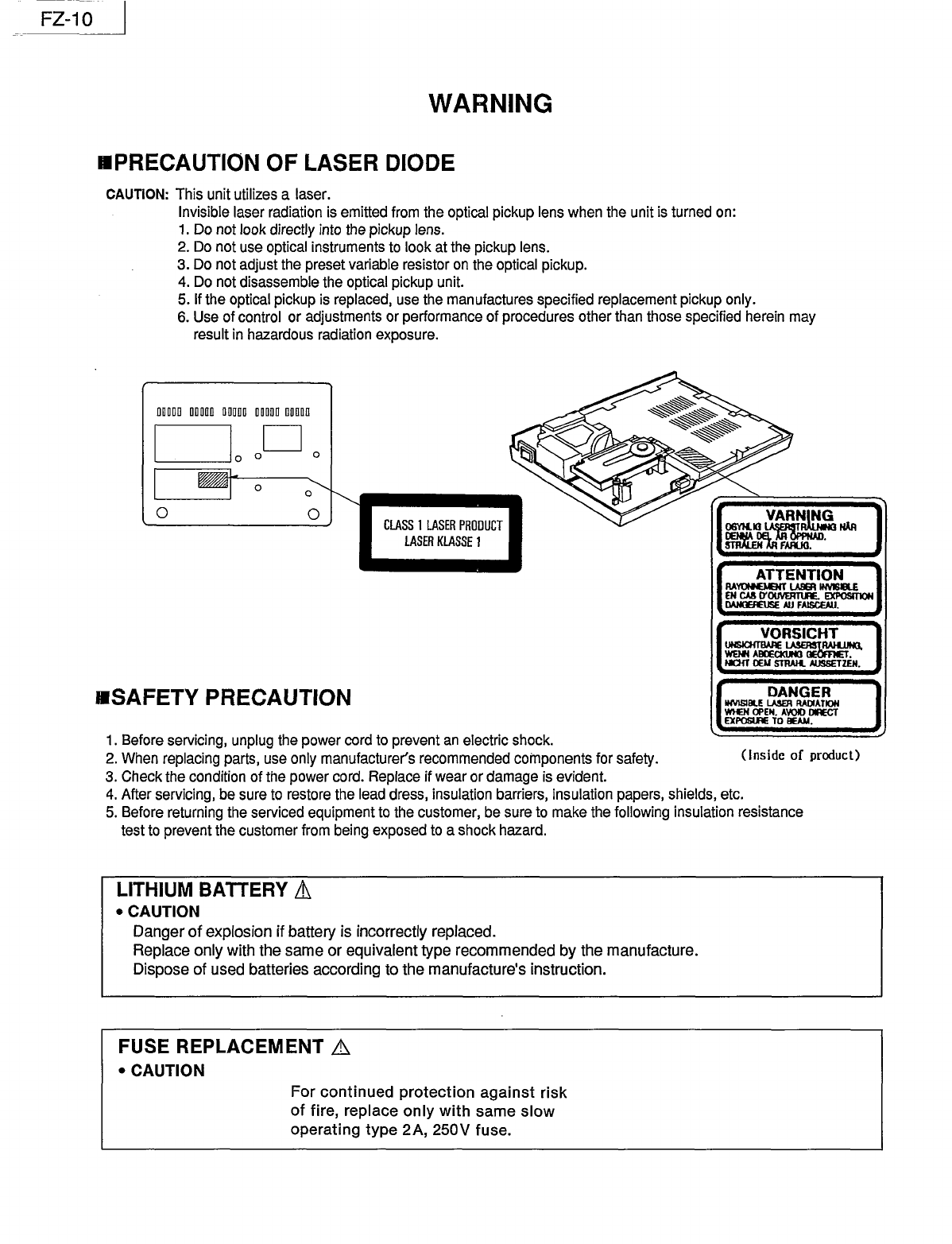

■

How

to

replace

the

fuse

Open

the fuse compartment with a screwdriver and

replace the fuse.

This equipment

is

produced to

BSS00/1983.

The

unit

is

in the standby condition when the AC power

supply cord

is

connected.

The

primary circuit

is

always "live" as long asthe power

cord

is

connected to

an

electrical outlet.

Fuse

FZ-10