o Limiting the Locking Range

If the quartzJock range is too wide, it will

overlap with strong adjacent broadcasting fre-

quencies and result in considerable tuning diffi-

culties. A DC amplifier is therefore used as a

limiter (limiter action by NFB circuit zenerdiodes)

which restricts the voltage applied to the variable

capacitancediode, thereby limiting the quartz-lock

range.

A DC voltage appears at pin no.13 of the IF

system IC (PA3007-A) when the antenna input

ievel drops below 5pV, or when the tuned fre-

quency has been detuned by more than t100kHz.

This DC voltage (FM muting signal) is applied to

the gate of Q2 (FET) via a Schmitt circuit, result-

ing in the FET being turned on, and the quartz-

Iock circuit being turned off.

Multiplex Decoder

The recently developed multiplex decoder IC

(PA4006-A) combines MPX decoding with muting

functions in a single IC, thereby handling the

functions of the more conventional MPX IC

(PA1001 A) and AF MUTING IC (PA1002-A).

Distortion ratings and S/N ratio have been

further improved by incorporating a chopper type

MPX decoder. The chopper type switching circuit

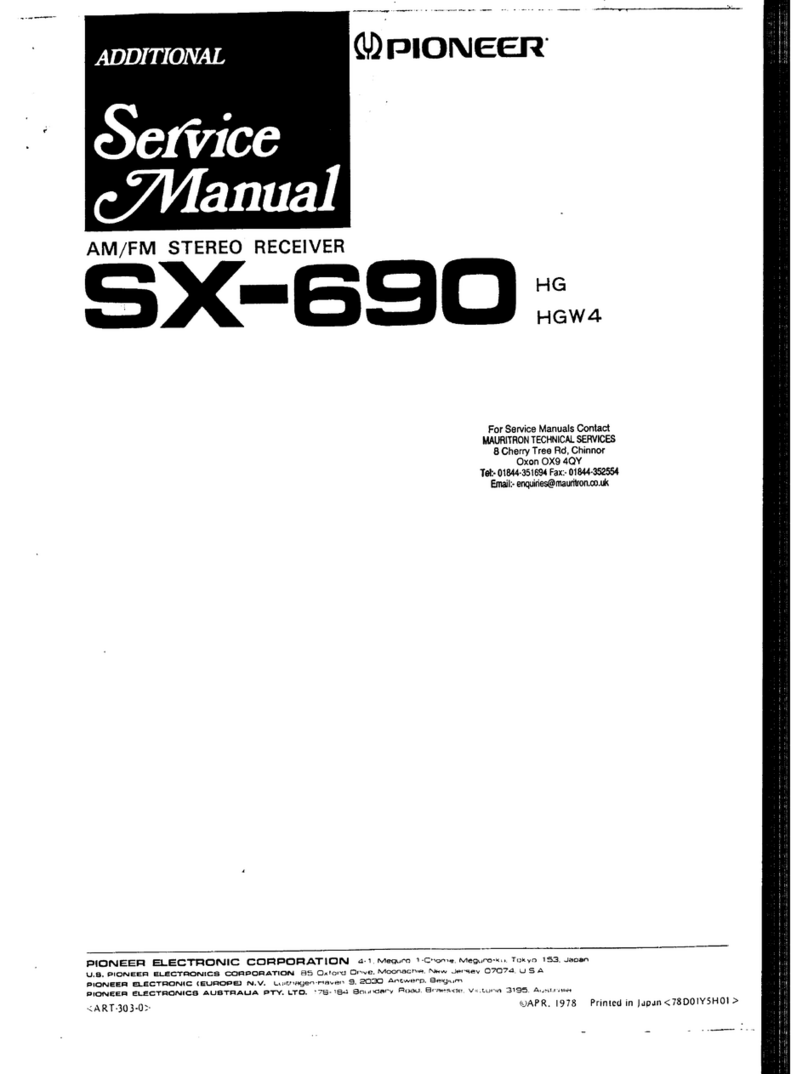

(see Fig. 4-2) operates by switching the signal

either to ground or to the through circuit, thereby

eliminating the generation of unwanted noise or

distortion. Furthermore, since the PA4006--4 fea-

tures DC direct-coupled switching with the detec-

tor, there is no deterioration in separation at the

Iow frequency end.

Besides the decoder and muting circuits, the

PA4006-.4 also incorporates the pilot signalcancel-

ler, stereo auto selector, VCO killer circuit, MU'l

amplifier. and MUT control circuit.

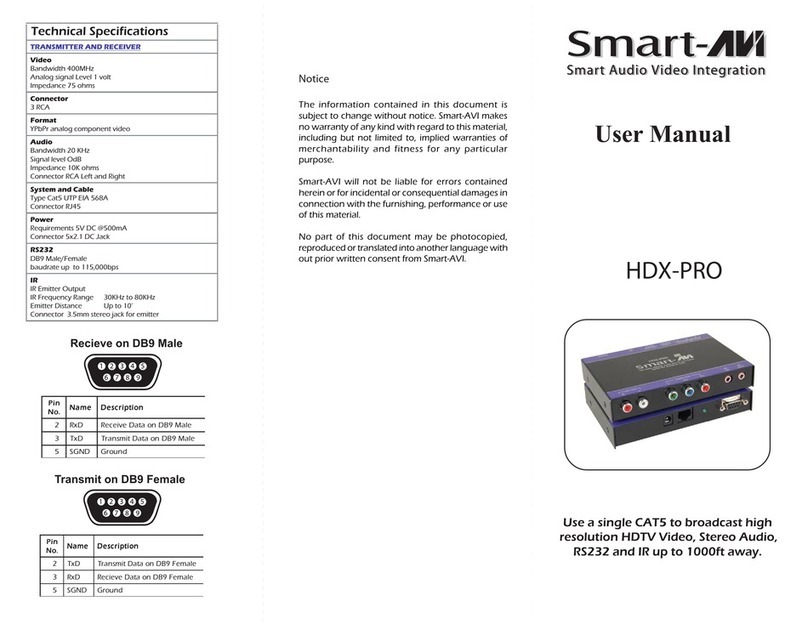

Composite

signal

Inprt Output

JUIIUUUIJUIJU'

.}. I

switchins

,in"r'r

S/ --'I

nL

Fig.4-2 ChopperTypeSwitchingCircuit

4.2AMTUNER

SECTION

The AM tuner section consists of a 2-ganged

tuning capacitor plus an IC (HA1197) which con-

tains a 1-stageRF amplifier, converter, 2-stage

IF

amplifier, detector, and AGC circuit.

The AM STEREO OUT terminal on the rear

panel is for connecting to an AM stereo broadcast

decoder adaptor. The signal appearing at this ter-

minal is the converter output passed via a buffer

(emitter-follower) stage.

sx-39clo

4.3AUDIO

SECTION

PhonoEqualizer

Amplif

ier

Fig. 4-3 shows the basic configuration of the

circuit. An S-N ratio of 86dB (at 2.5mV input,

IHF-A) has been achieved by using a ultra-low-

noise PNP transistor (2SA978) at the first stage,

and reducing the signal source resistance and

equalizer element impedance. High voltage gain is

provided in the following stage by a bootstrap cir-

cuit. The output stage is a complementary sym-

metrical SEPP circuit. The high voltage utility

factor of the SEPP circuit provides a high maxi-

mum output voltage. Dynamic range of the

equalizer amplifier is therefore wide and overload

input level at 0.005% distortion is 300mV (rms at

lkHz).

tNHMrl

ToneControl

Fig. 4-4 shows the basic configuration of the

circuit. This circuit is an NFB type tone control

with IC(HA12017P).

Tonecontrol (BASS,

TREBLE) isaccomplished

by providing the tone amplifier NFB circuit with

a frequency selective characteristic. The capaci-

tance

of C7-C4 arechanged

by theTURNOVER

switches

(by addinganother capacitorsin parallel)

to provideselectionof the frequency.

The NFB circuit is changedto a flat frequency

characteristicwhen the TONE switchin the OFF

oosition.

Fig.

4-3 Phono

Equalizer

Amplif

ier

Tone

Control