Renesas HD151TS207SS User manual

Other Renesas Computer Hardware manuals

Renesas

Renesas M3T-SSOP42B-450 User manual

Renesas

Renesas RX72T User manual

Renesas

Renesas HD74LV2GT14A User manual

Renesas

Renesas H8SX series User manual

Renesas

Renesas Asynchronous SH7145F Installation and operating instructions

Renesas

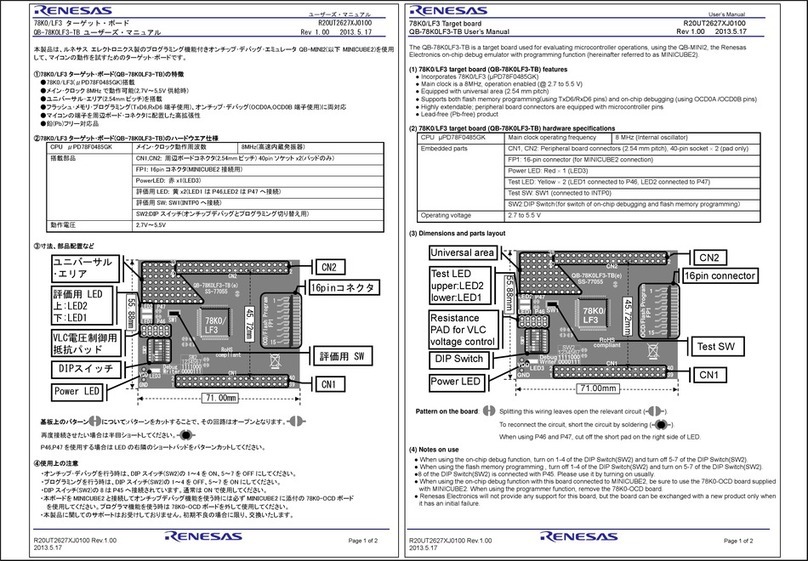

Renesas 78K0/LF3 User manual

Renesas

Renesas PROM Programming Adapter PCA7448 User manual

Renesas

Renesas H8SX1664 User manual

Renesas

Renesas M306K9T2-CPE User manual

Renesas

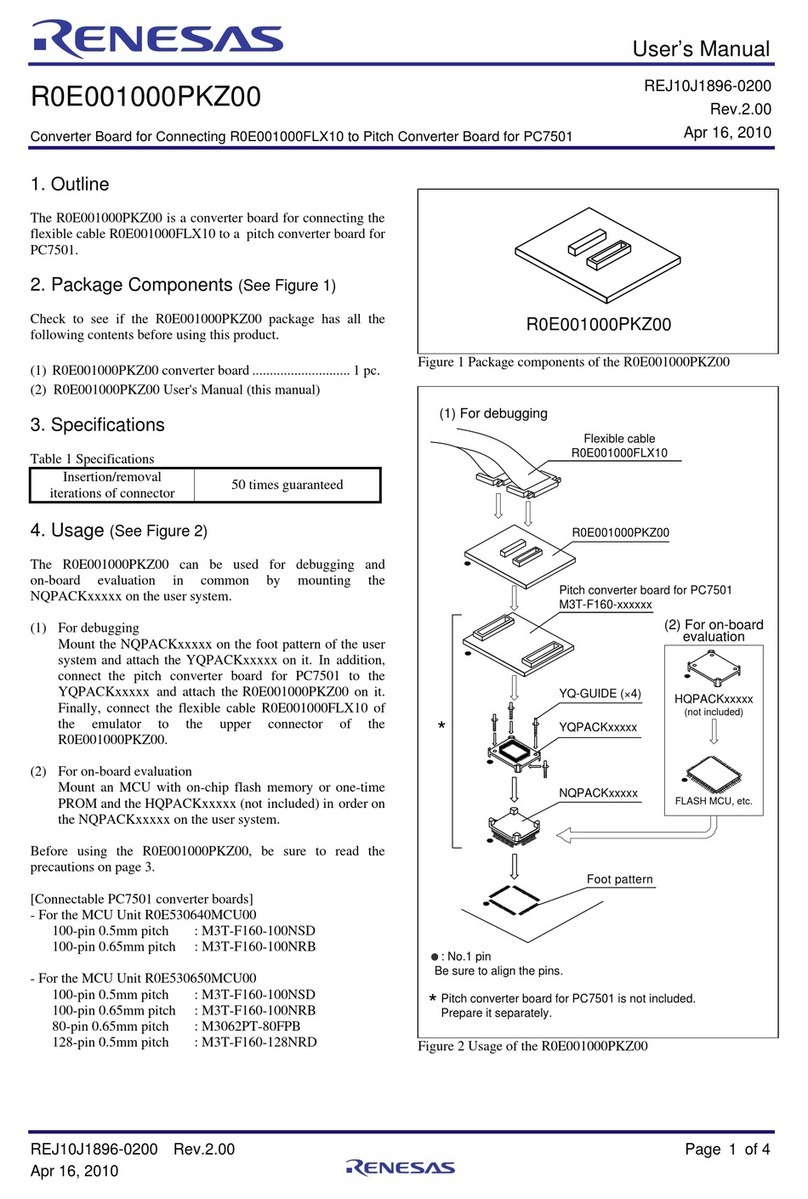

Renesas R0E001000PKZ00 User manual

Renesas

Renesas REG10J0020-0200 User manual

Renesas

Renesas M3T-FLX-DCT613 User manual

Renesas

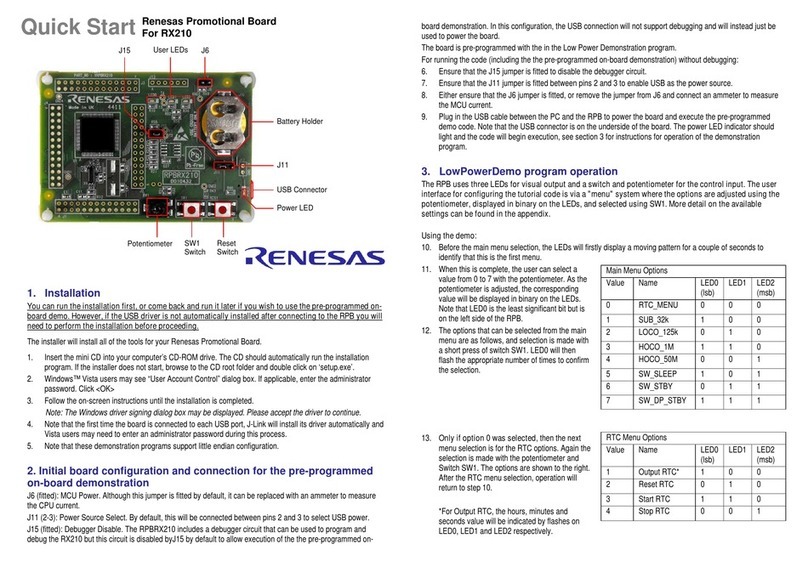

Renesas Promotional board User manual

Renesas

Renesas Converter Board M3T-100LCC-QSD User manual

Renesas

Renesas HD74UH04 User manual

Renesas

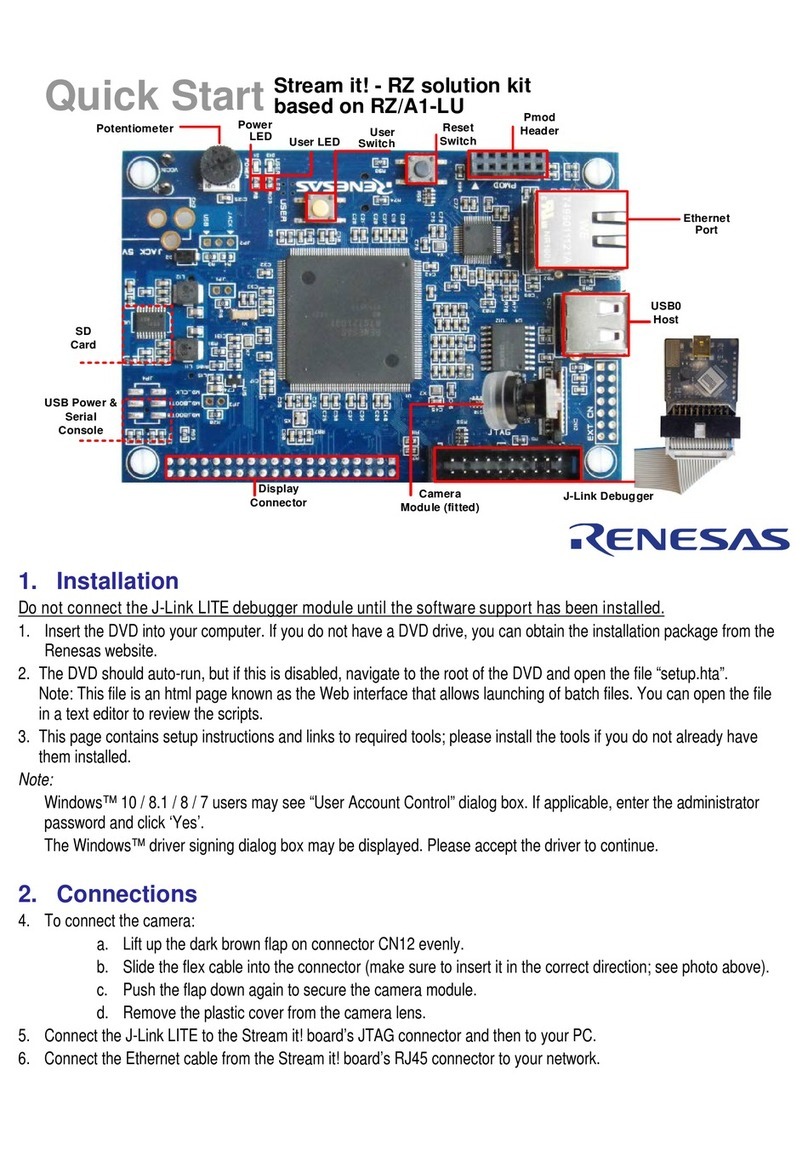

Renesas Stream it User manual

Renesas

Renesas M3T-100LCC-80QSB User manual

Renesas

Renesas H8S series User manual

Renesas

Renesas F-ZTAT H8 Series User manual

Renesas

Renesas RL78/I1D Installation and operating instructions

Popular Computer Hardware manuals by other brands

EMC2

EMC2 VNX Series Hardware Information Guide

Panasonic

Panasonic DV0PM20105 Operation manual

Mitsubishi Electric

Mitsubishi Electric Q81BD-J61BT11 user manual

Gigabyte

Gigabyte B660M DS3H AX DDR4 user manual

Raidon

Raidon iT2300 Quick installation guide

National Instruments

National Instruments PXI-8186 user manual