36 Thornwood Dr. –Ithaca, NY 14850 © 2019 Kionix –All Rights Reserved

tel: 607-257-1080 – fax:607-257-1146 894-12874-1907311402-0.17

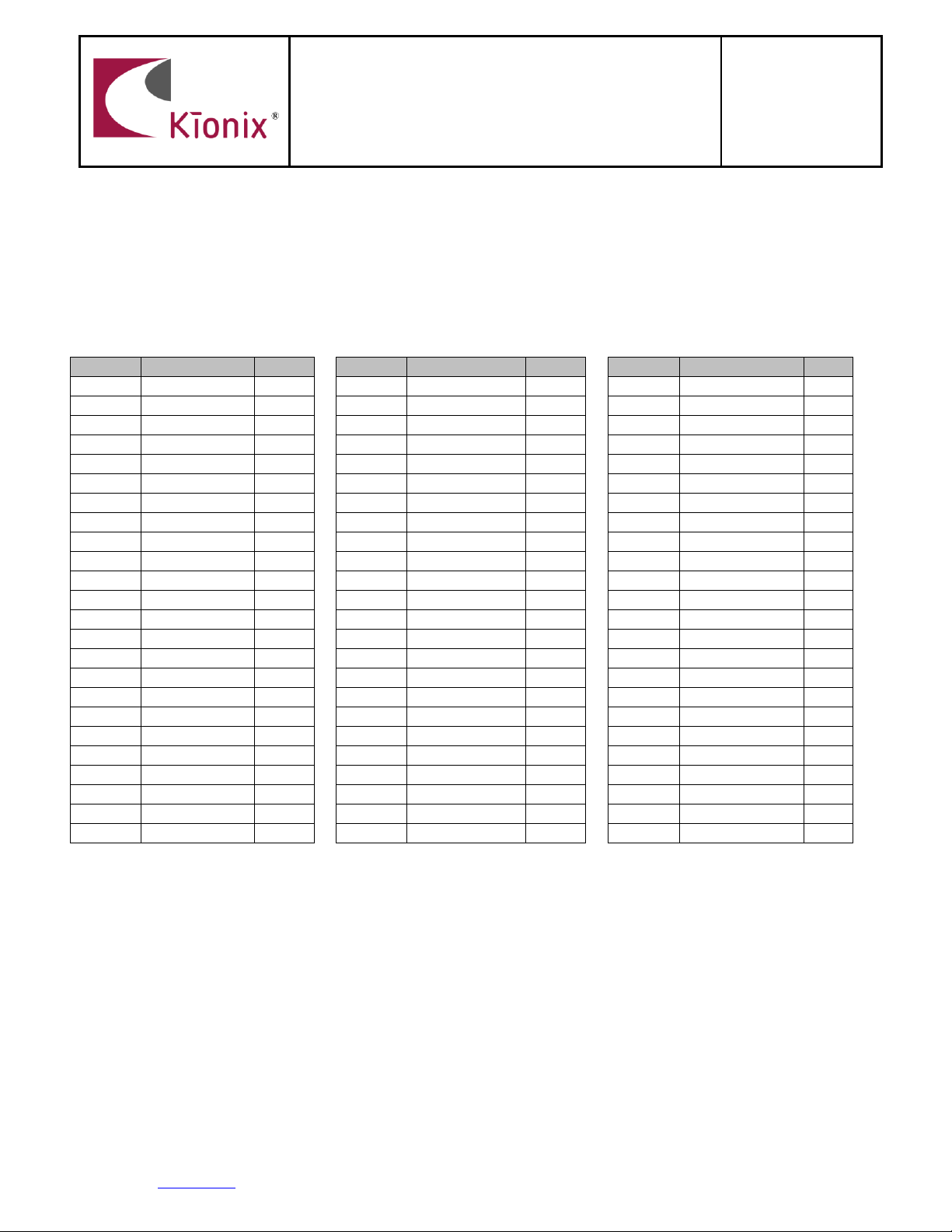

1.16 TAP /DOUBLE-TAP CONTROL REGISTERS (0X2A –0X31) ................................................................................................. 33

TDTRC ...................................................................................................................................................................................... 33

TDTC ........................................................................................................................................................................................ 34

TTH .......................................................................................................................................................................................... 34

TTL ........................................................................................................................................................................................... 34

FTD........................................................................................................................................................................................... 35

STD........................................................................................................................................................................................... 35

TLT ........................................................................................................................................................................................... 35

TWS.......................................................................................................................................................................................... 36

1.17 FREE FALL CONTROL REGISTERS (0X32 –0X34)................................................................................................................ 36

FFTH......................................................................................................................................................................................... 36

FFC ........................................................................................................................................................................................... 36

FFCNTL..................................................................................................................................................................................... 37

1.18 TILT ANGLE CONTROL REGISTERS (0X37 –0X39)............................................................................................................. 38

TILT_ANGLE_LL ........................................................................................................................................................................ 38

TILT_ANGLE_HL ....................................................................................................................................................................... 38

HYST_SET ................................................................................................................................................................................. 38

1.19 LP_CNTL1 (0X3A)............................................................................................................................................................. 39

1.20 LP_CNTL2 (0X3B)............................................................................................................................................................. 39

1.21 WAKE-UP &BACK-TO-SLEEP THRESHOLD AND COUNTER SETUP REGISTERS (0X49 –0X4D) ........................................... 40

WUFTH, BTSWUFTH, BTSTH .................................................................................................................................................... 40

BTSC......................................................................................................................................................................................... 40

WUFC....................................................................................................................................................................................... 40

1.22 SELF_TEST (0X5D)............................................................................................................................................................ 41

1.23 OUTPUT BUFFER REGISTERS (0X5E –0X63) ..................................................................................................................... 42

BUF_CNTL1 .............................................................................................................................................................................. 42

BUF_CNTL2 .............................................................................................................................................................................. 43

BUF_STATUS_1 and BUF_STATUS_2 ....................................................................................................................................... 44

BUF_CLEAR .............................................................................................................................................................................. 44

BUF_READ ............................................................................................................................................................................... 44

1.24 ADVANCED DATA PATH CONTROL REGISTERS (0X64 –0X76) .......................................................................................... 45

ADP_CNTL1.............................................................................................................................................................................. 45

ADP_CNTL2.............................................................................................................................................................................. 46

ADP_CNTL3.............................................................................................................................................................................. 47

ADP_CNTL4, ADP_CNTL5, ADP_CNTL6 .................................................................................................................................... 47

ADP_CNTL7, ADP_CNTL8, ADP_CNTL9 .................................................................................................................................... 48

ADP_CNTL10............................................................................................................................................................................ 48

ADP_CNTL11............................................................................................................................................................................ 48

ADP_CNTL12, ADP_CNTL13..................................................................................................................................................... 49

ADP_CNTL14, ADP_CNTL15, ADP_CNTL16, ADP_CNTL17 ....................................................................................................... 49

ADP_CNTL18............................................................................................................................................................................ 49

ADP_CNTL19............................................................................................................................................................................ 49

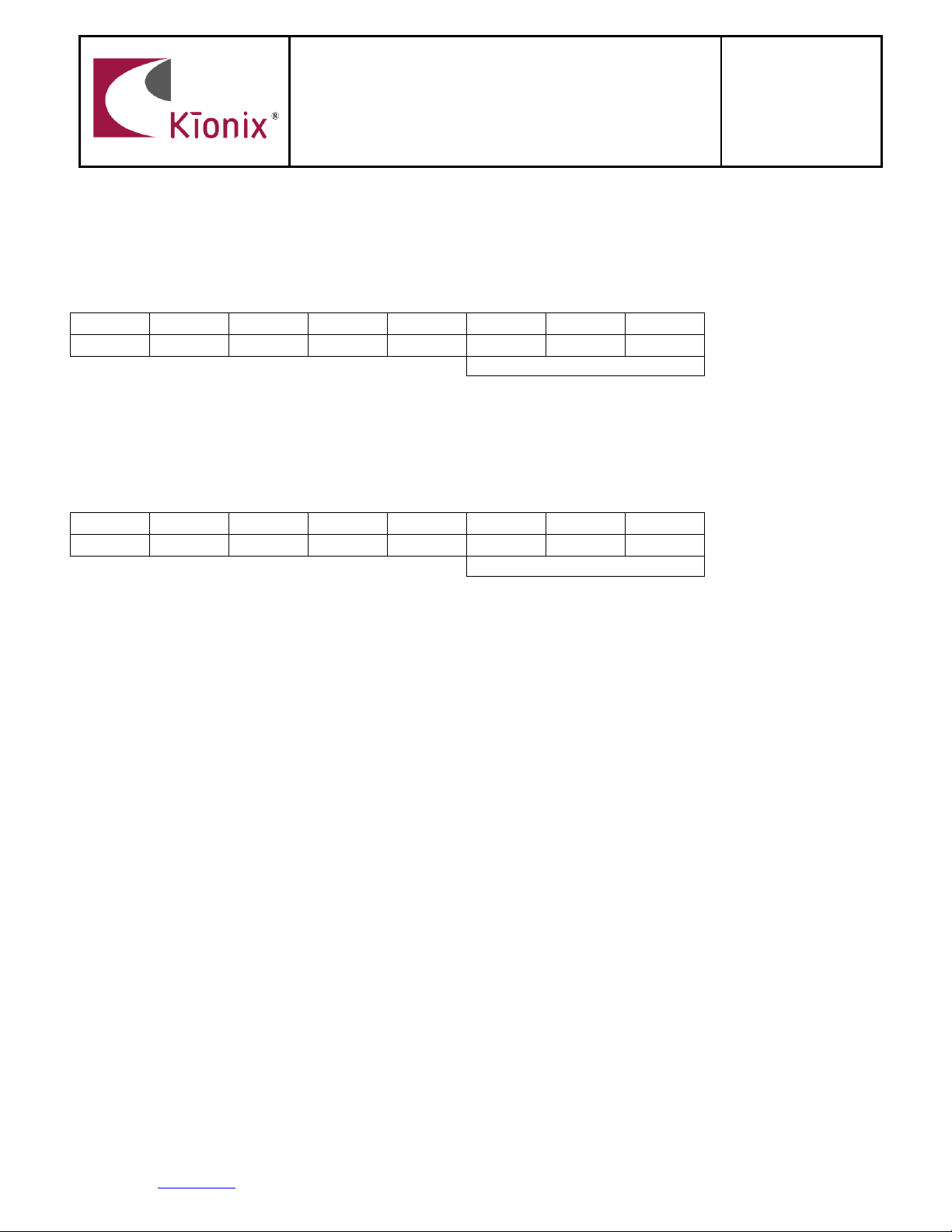

2EMBEDDED APPLICATIONS .............................................................................................................................................. 50

2.1 ORIENTATION DETECTION FEATURE......................................................................................................................................... 50

Hysteresis................................................................................................................................................................................. 50

Device Orientation Angle (Tilt Angle) ...................................................................................................................................... 51

Tilt Timer.................................................................................................................................................................................. 51

2.2 MOTION INTERRUPT FEATURE DESCRIPTION ............................................................................................................................. 52

Enabling / Disabling................................................................................................................................................................. 52