3/24

・Audio Interface

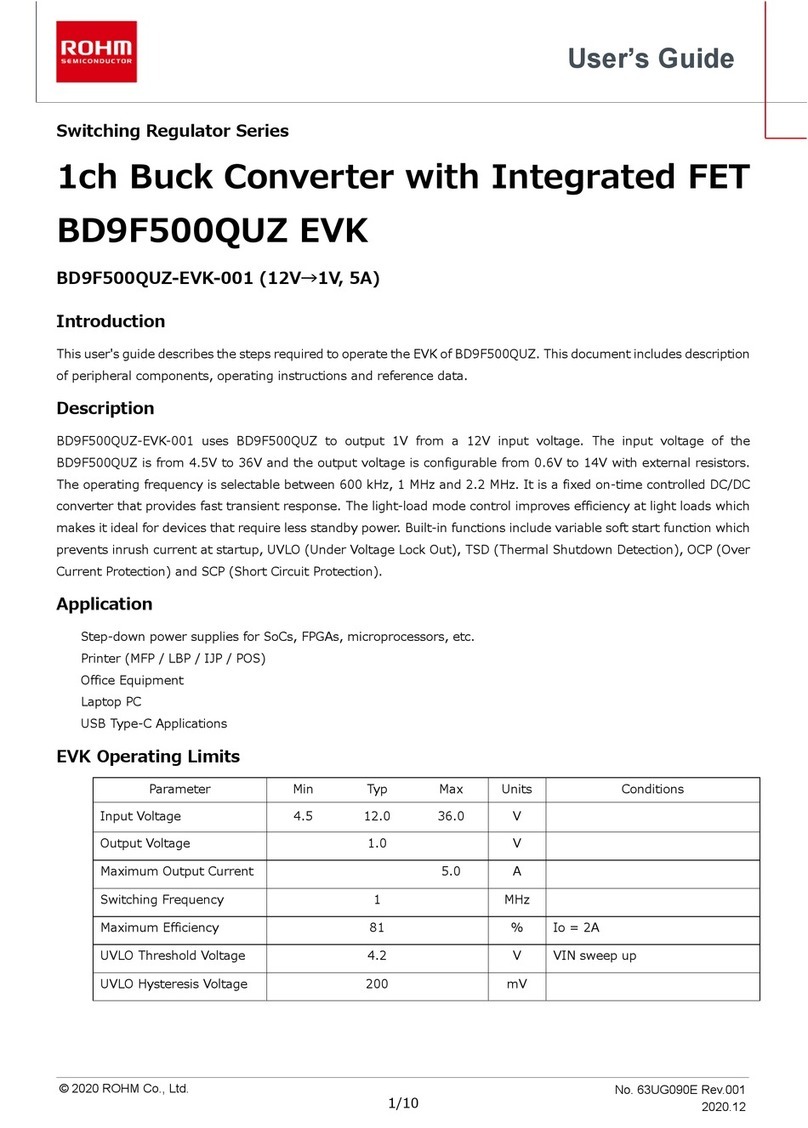

Parameter Symbol Min Typ Max Unit Condition

MCLKI Frequency fMCLK 4.096 -18.432 MHz

MCLKI Duty Ratio dMCLK 45 -55 %

LRCLK Frequency fs 16 -48 kHz

LRCLK Duty Ratio dLR 45 -55 %

BCLK Frequency fBCK 0.512 -3.072 MHz

BCLK Duty Ratio dBCK 45 -55 %

LRCLK edge to BCLK↑Time tLRS 50 --ns

BCLK↑to LRCLK Edge Time tSLR 50 --ns

Data Hold Time tSDH 50 --ns

Data Set-up Time tSDS 50 --ns

【BU7893GU】

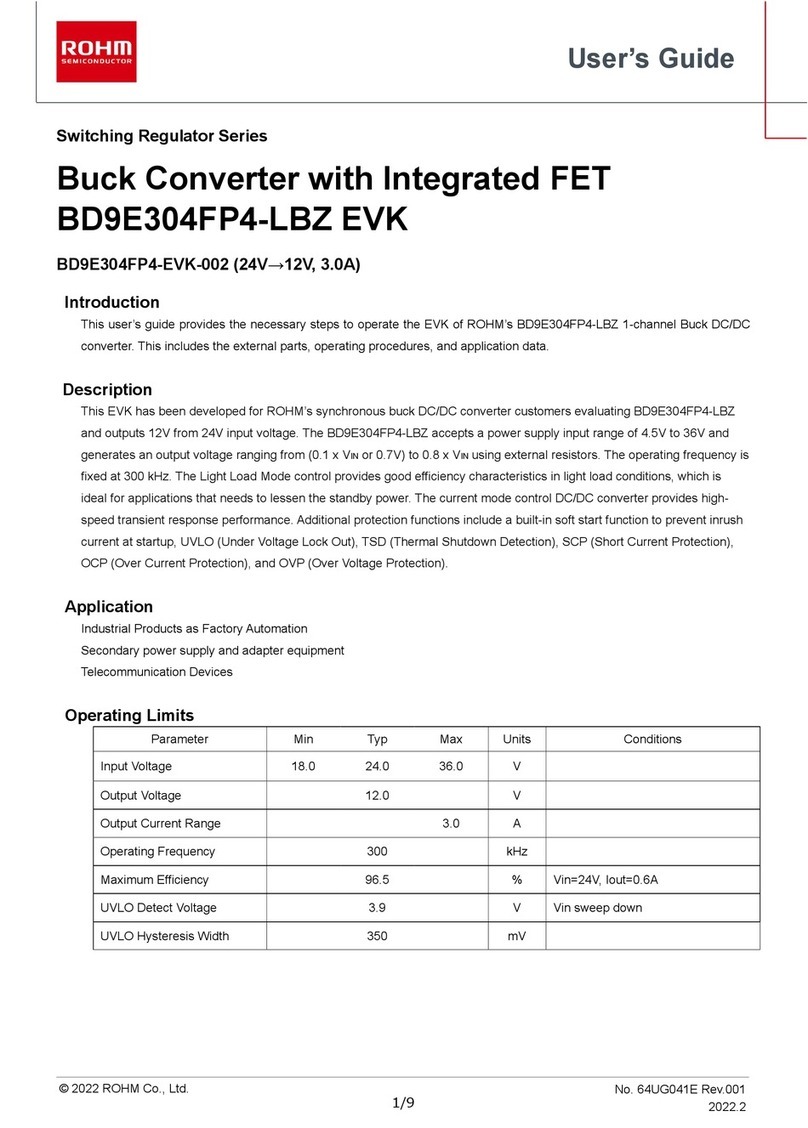

・Whole Block

Unless otherwise specified、Ta= 25℃、DVDD_CORE=1.8V、DVDD_IO=1.8V、AVDD=2.8V、Digital input terminal is fixed with

DVDD_IO ”L” or ”H” level、The gain settings of the audio paths are all 0dB, and no signal

Parameter Symbol Min Typ Max Unit Condition

DVDD_CORE Stand-by Current

(Core logic block) ISTCO --10 μA standby,CLKI = DVSS

DVDD_IO Stand-by Current ISTIO --5 μA standby,CLKI = DVSS

AVDD Stand-by Current ISTA --5 μA standby

DVDD_CORE Operation Current IDDCO -5 10 mA

DVDD_IO Operation Current IDDIO -0.1 1 mA

BCLK,LRCLK = Input mode

MCLK = L output

AVDD Operation Current 1

(Analog melody) IDDA1 -1.6 2.8 mA

ANAINL→MIX1→SPOL

ANAINR→MIX2→SPOR

AVDD Operation Current 2

(Digital melody) IDDA2 -6.0 10.0 mA

SDI→MIX1→SPOL

SDI→MIX2→SPOR

TCXOI = 19.8MHz,fs = 44.1kHz

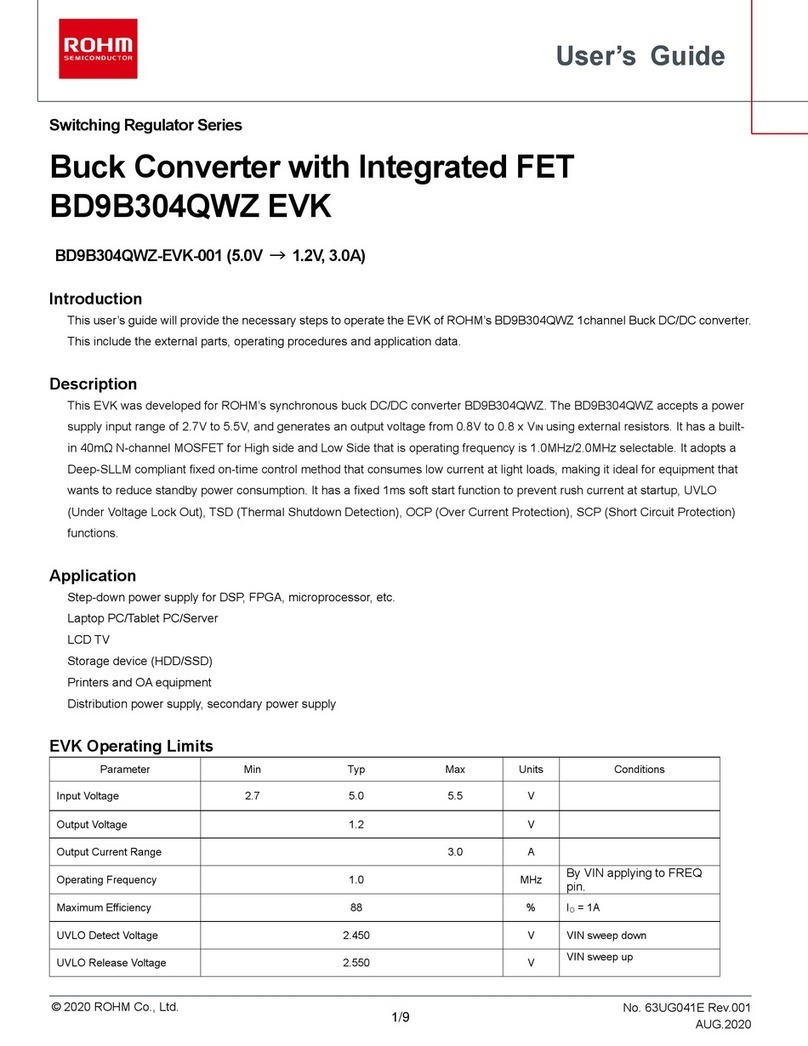

・DC Characteristic

Parameter Termin

-al

Symbol Min Typ Max Unit Condition

L Output Voltage Vold All output

terminal※10 -0.30 V Iol=+0.8mA

H Output Voltage Vohd All output

terminal※1

DVDD_IO

-0.30 -DVDD_IO V Ioh=-0.8mA

L Level Input Voltage1 Vild1 All input

terminal※2-0.3 -DVSS+0.5 V

L Level Input Voltage 2 Vild2 CLKI※3-0.3 -※3 V

H Level Input Voltage 1 Vihd1 All input

terminal※2

DVDD_IO

-0.5 -DVDD_IO

+0.3 V

H Level Input Voltage 2 Vihd2 CLKI※3※3 -DVDD_CORE

+0.3 V

L Level Input Current Iild All input

terminal※2-1 -1 μA Input terminal voltage

is DVSS

H Level Input Current 1 Iihd1 All input

terminal※2-1 -1 μA Input terminal voltage

is DVDD_IO

H Level Input Current 2 Iihd2 CLKI※3-1 -1 μA Input terminal voltage

is DVDD_CORE

Output OFF Current Iozd Hi-Z

terminal※4-10 -10 μA

※ 1 : They also contain interactive terminals that are set output state.

※ 2 : They also contain interactive terminals that are set input state.

※ 3 : Please connect 100pF coupling capacitor and input 0.5VP-P or more when you input through coupling capacitor.

※ (In address 15h CLKSEL1=0、CLKSEL0=1)

※ 4 : At interactive terminals of input state or three-state terminals of output-disable state