2

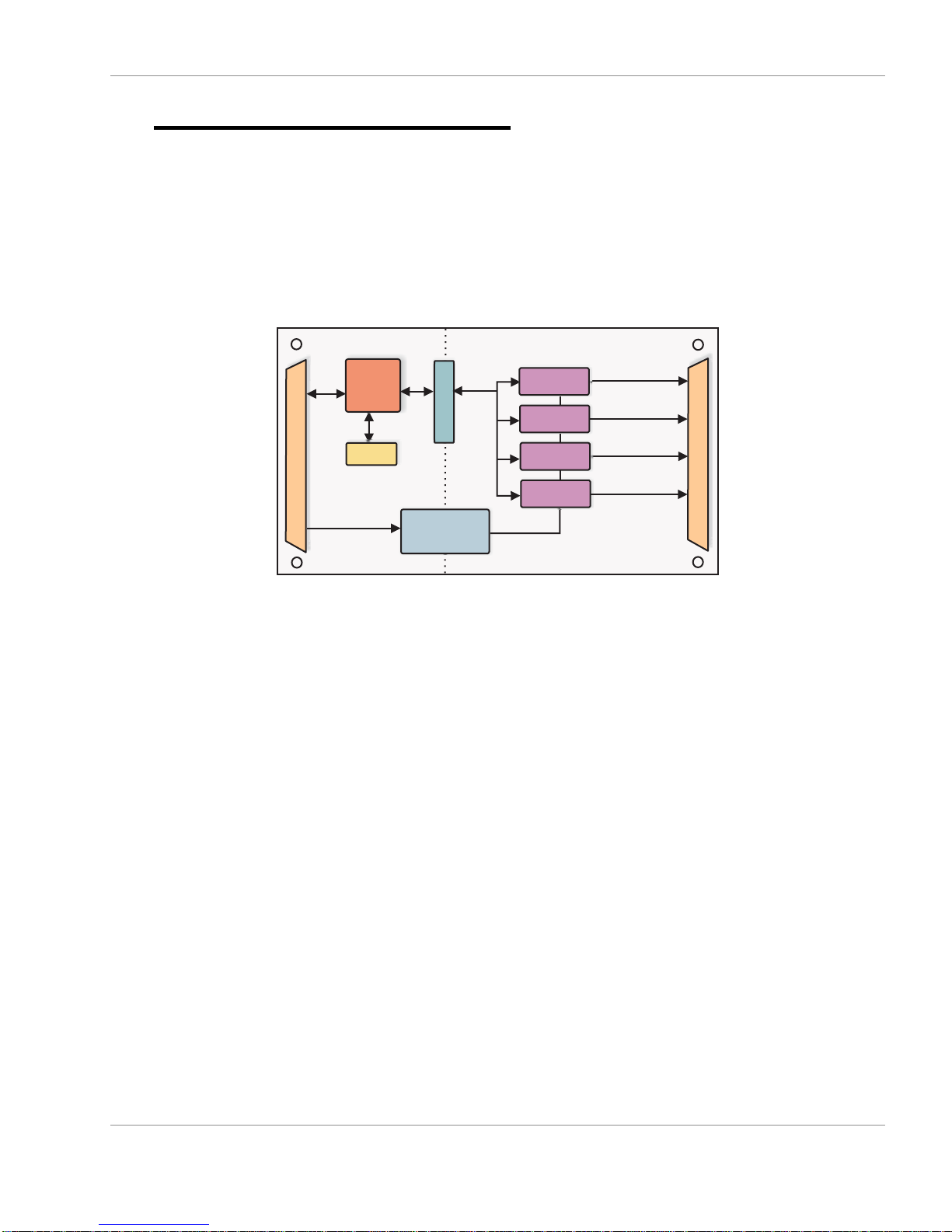

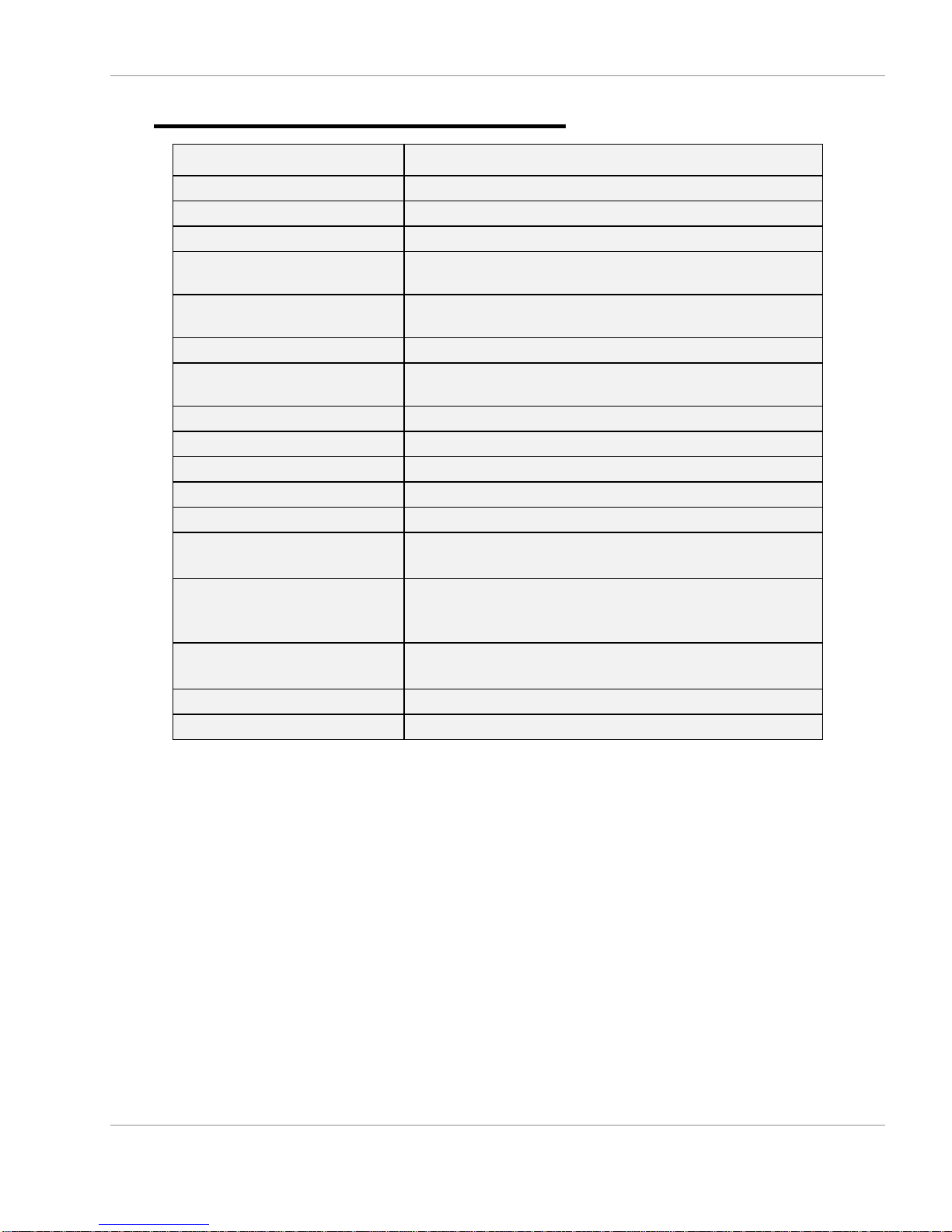

IP-OPTODA16CH4

4 channels of optically isolated

16-bit D/Aconversion

SBS Technologies, Inc.

1284 Corporate Center Drive

St. Paul, MN 55121-1245

Tel: (651) 905-4700

FAX: (651) 905-4701

http://www.sbs.com

©2003 SBS Technologies, Inc.

IndustryPack is a registered trademark of SBS

Technologies, Inc. QuickPack, SDpacK and Unilin are

trademarks SBS Technologies, Inc. PC•MIP is a

trademark of SBS Technologies, Inc. and MEN Mikro

GmbH.

SBS Technologies, Inc acknowledges the trademarks of

other organizations for their respective products

mentioned in this document.

All rights are reserved: No one is permitted to reproduce

or duplicate, in any form, the whole or part of this

document without the express consent of SBS

Technologies, Inc. This document is meant solely for the

purpose in which it was delivered.

SBS Technologies, Inc. reserves the right to make any

changes in the devices or device specifications contained

herein at any time and without notice. Customers are

advised to verify all information contained in this

document.

The electronic equipment described herein generates,

uses and may radiate radio frequency energy, which can

cause radio interference. SBS Technologies, Inc.

assumes no liability for any damages caused by such

interference.

SBS Technologies, Inc.’s products are not authorized for

use as critical components in medical applications such

as life support equipment, without the express consent of

the president of SBS Technologies, Inc., Commercial

Group.

This product has been designed to operate with

IndustryPack, PC•MIP or PMC modules or carriers and

compatible user-provided equipment. Connection of

incompatible hardware is likely to cause serious damage.

SBS Technologies, Inc. assumes no liability for any

damages caused by such incompatibility.