-

3

-

Pin Signal

In

/

Out Function (standby

=

power

off)

No

.

Name

1

A01 Out Address bus line, high during standby

2

R/W Out Write clock

signal

,

normally high

3

</J

AL

Out Low order bit address

latch

,

normally high. The clock used to latch the low order 8 bits

of

the

16

-

bit

address signal

for

the data bus

I

ine, when

a

large capacity

R

O

M

is

used

.

4

TES

I

n

Test input, normally low

5

</Ji

In Oscillator input

6

</J

o

Out Oscillator

output

7

RES

I

n

Reset

i

nput, normally pulled down

to

low level.

Res

e

t

when high.

8 Xin

I

n

CE

-

125 microcassette

option

signal input (MTin)

9

ON In ON (BREAK) key input, normally pulled down

t

o low

l

e

v

el

10

Xout

Out CE-125 m

icro

c

assette

option

signal and

buzze

r

si

gna

l

output

(MTo

u

t1)

11

Dis Out LCD driver

con

t

rol signal

12

HA Out LCD driver

cl

o

ck. Low during standby, and

2

kHz pulse

is

issued during

dis

p

laying.

1

3 iA8

In

/

Out Key

input

/

key strobe

output

,

normally low, but pulse issued

with

a

key

oper

a

tion.

14

i

A7

In

/

Out Key

input

/

key strobe

output,

normally low, but pulse issued

with

a

key opera

t

ion

.

15

i

A6

In

/

Out Key

input

/

key strobe

output,

normally low,

bu

t

pulse

issue

d

with

a

key op

e

r

a

tion

.

1

6

iA5

In

/

Out Key

i

nput

/

key strobe

output,

normally low, but pulse issued

with

a

key

opera

t

ion.

1

7

iA4

In

/

Out Key

input

/

key strobe

output

,

normally low,

b

u

t

pulse issued

with

a

key

oper

a

tio

n

.

18 iA3

I

n

/

Out Key

in

p

ut

/

key

s

t

robe

output,

normally

low

,

bu

t

pulse

iss

u

ed

with

a

key operation.

1

9 iA2

In

/

Out Key

i

nput

/

key strobe

output

,

normally

low

,

bu

t

pulse issued

with

a

key operation.

20 iA1

In

/

Out Key

input

/

key strobe

output,

norma

l

ly

low

,

but pulse issued

with

a

key

operati

o

n.

21

iB8 In ACK signal which enables

th

e

1

/

0

(PCU)

to

read data from the

C

P

U.

22 iB7

I

n

Data in

s

i

gnal (Din)

wh

i

ch

is

a

serial data input from the PCU

(b

i

t unit,

se

r

ial

handsha

k

e).

·

-

23

i

B6 Out (SEL2) select

output,

P

-

type open drain

24 iB5 Out (SE

L

1

)

select

output,

P-type open drain

25 iB4 In Slide switch input

26 iB3 Out Key strobe

output,

low during standby,

bu

t

pulse issued

with

a

key

operati

o

n.

27 iB2 Out Key strobe

output,

low during standby, but

puls

e

issu

e

d

wit

h

a

key

opera

t

ion.

28

i

B1

Out Key strobe

output

,

low during

standby

,

but pulse issued

with

a

key

operation

.

29 VM In LCD power supply

30

VA

In

LC

D

power supply

31

GND In Power supply

32

H1

Out

L

CD backplate

signal

,

high impedance

duri

n

g

stand

b

y, but 4 level pulse issued

d

uring

displaying

.

33 H2 Out LCD backplate signal, high impedance during

standby

,

but 4 level pulse

i

s

sued

d

u

ring

displaying

.

34 H3 Out LCD backplate signal, high impedance during standby, but 4 level pulse issued during

displaying

.

35 H4

O

ut LCD backplate signal, high impedance during standby, but 4 level pulse

is

s

ued

dur

i

ng

display

i

ng

.

36 H5 Out LCD backplate

signal

,

high

i

mpedance

dur

i

ng

standby

,

but 4 level pulse issued

dur

i

ng

display

i

ng.

37 H6 Out LCD Backplate signal, high impedance during standby, but 4 level pulse issued during

displaying

.

38 H7 Out LCD backplate signal, high impedance during

standby

,

but 4 level pulse issued

d

ur

i

ng

displaying

.

3

9

HS

Out LCD backplate

si

g

n

a

l, high

impedan

c

e

during

st

a

ndby, but 4 level pulse

iss

u

ed during

displ

a

ying.

4

0 H9

O

ut LCD

b

ac

k

p

l

at

e

s

i

g

n

a

l

,

hig

h

i

mp

eda

n

ce

during

s

t

a

n

dby,

b

ut 4

l

evel

p

u

lse

is

sued

d

ur

i

ng

dis

p

laying

.

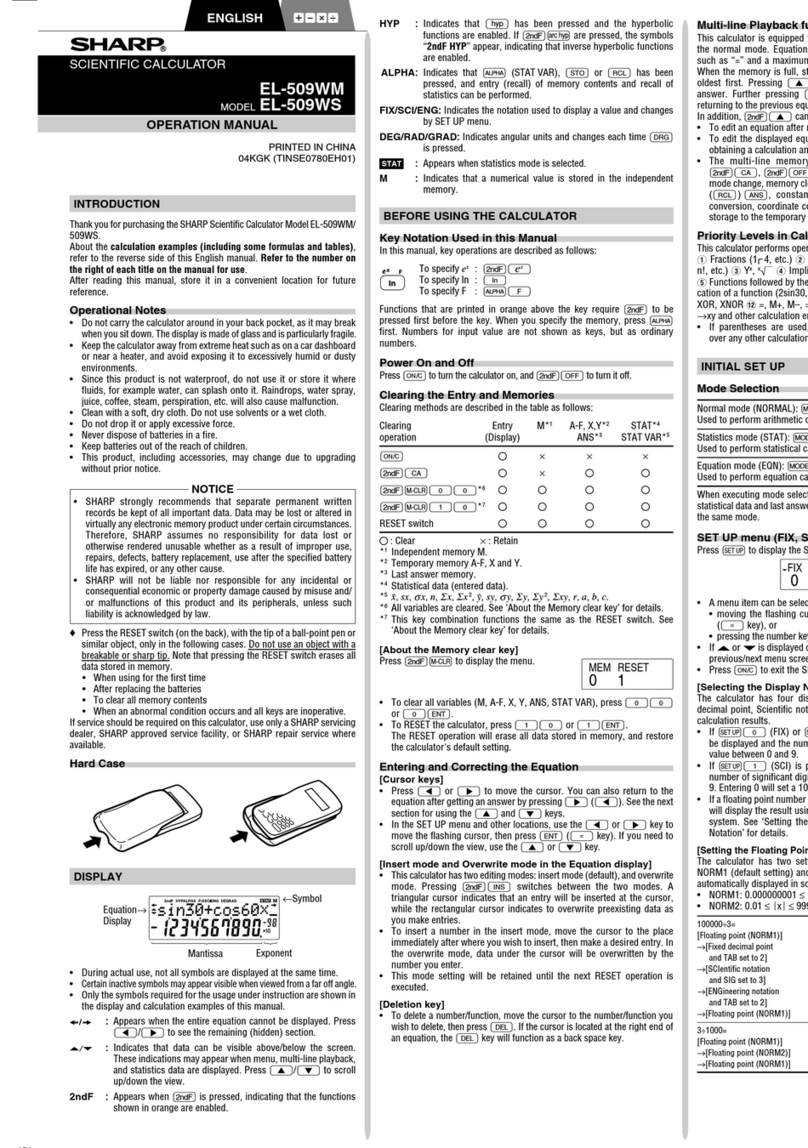

3~

CPU

SI

GNAL

DESCRIPT

I

ON

..

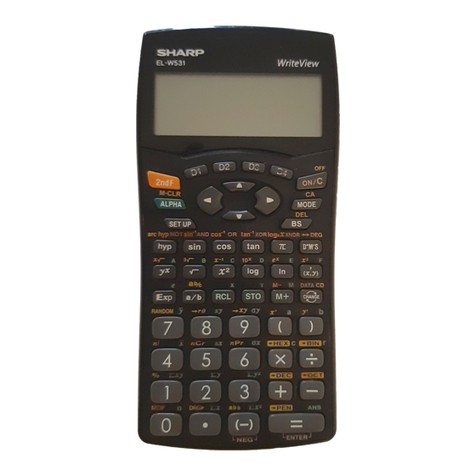

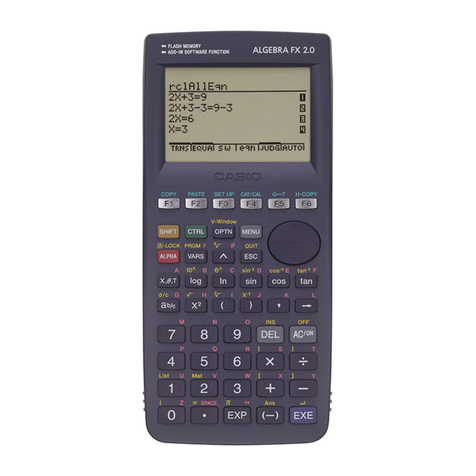

PC-1260

PC

-

1261