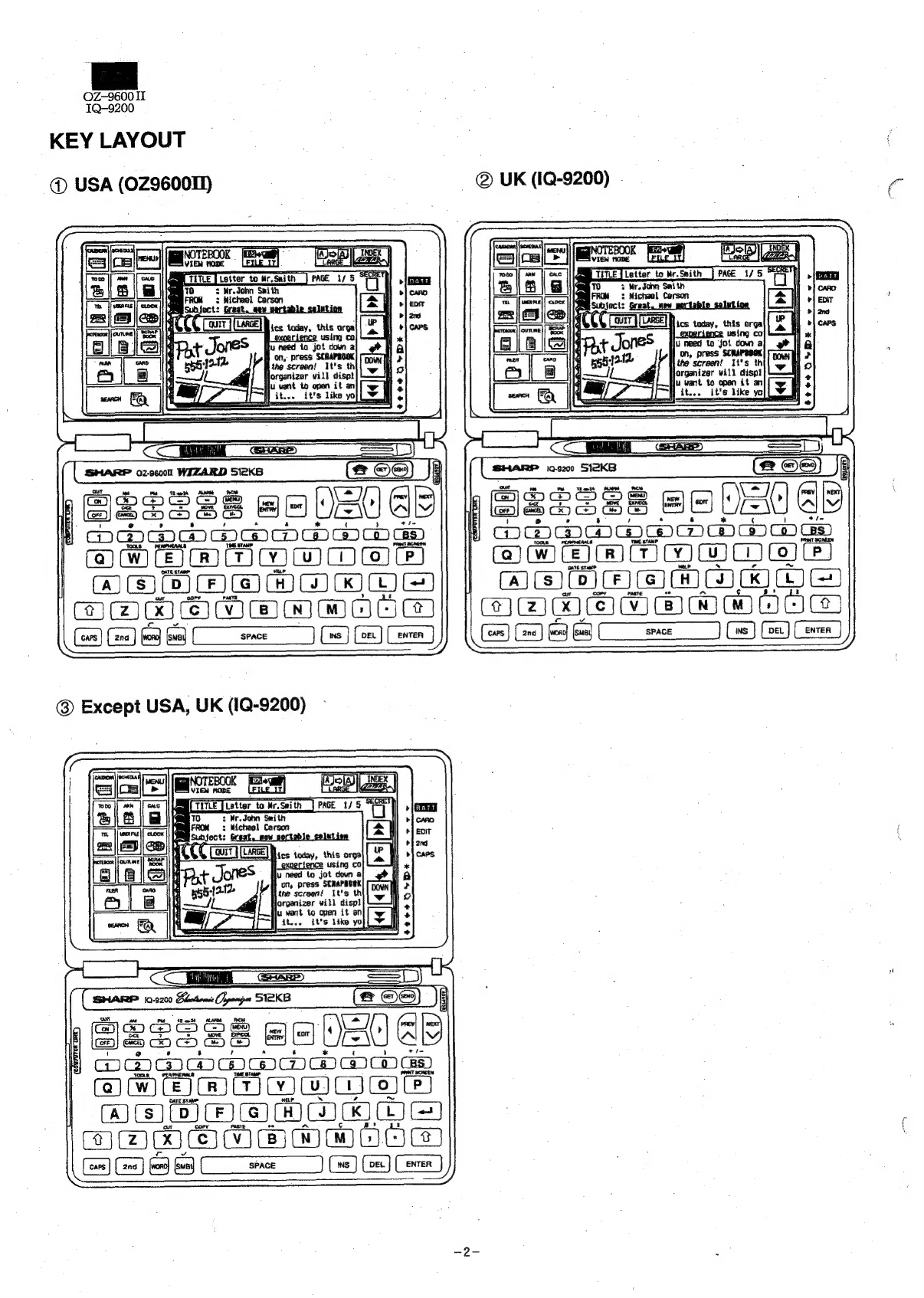

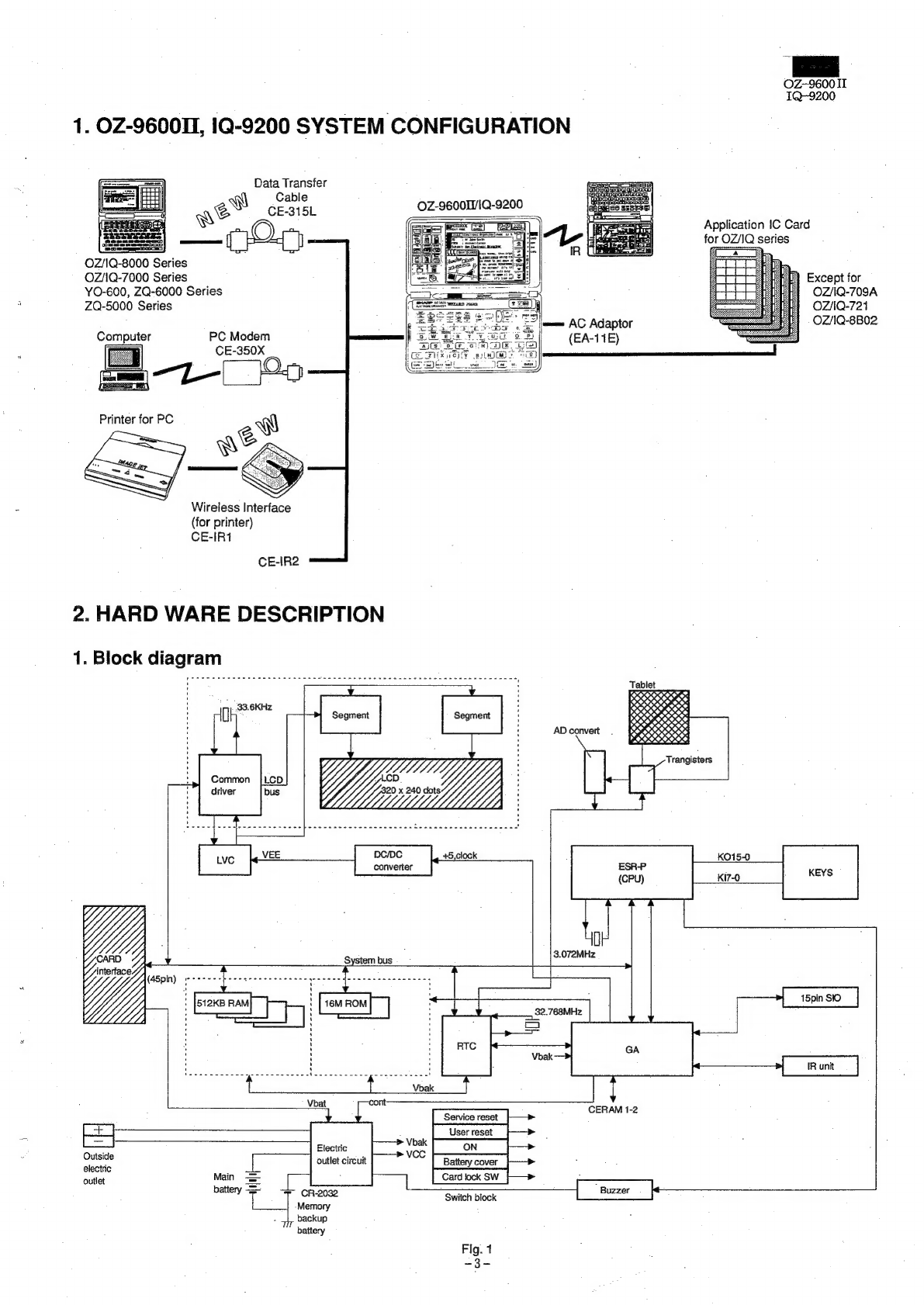

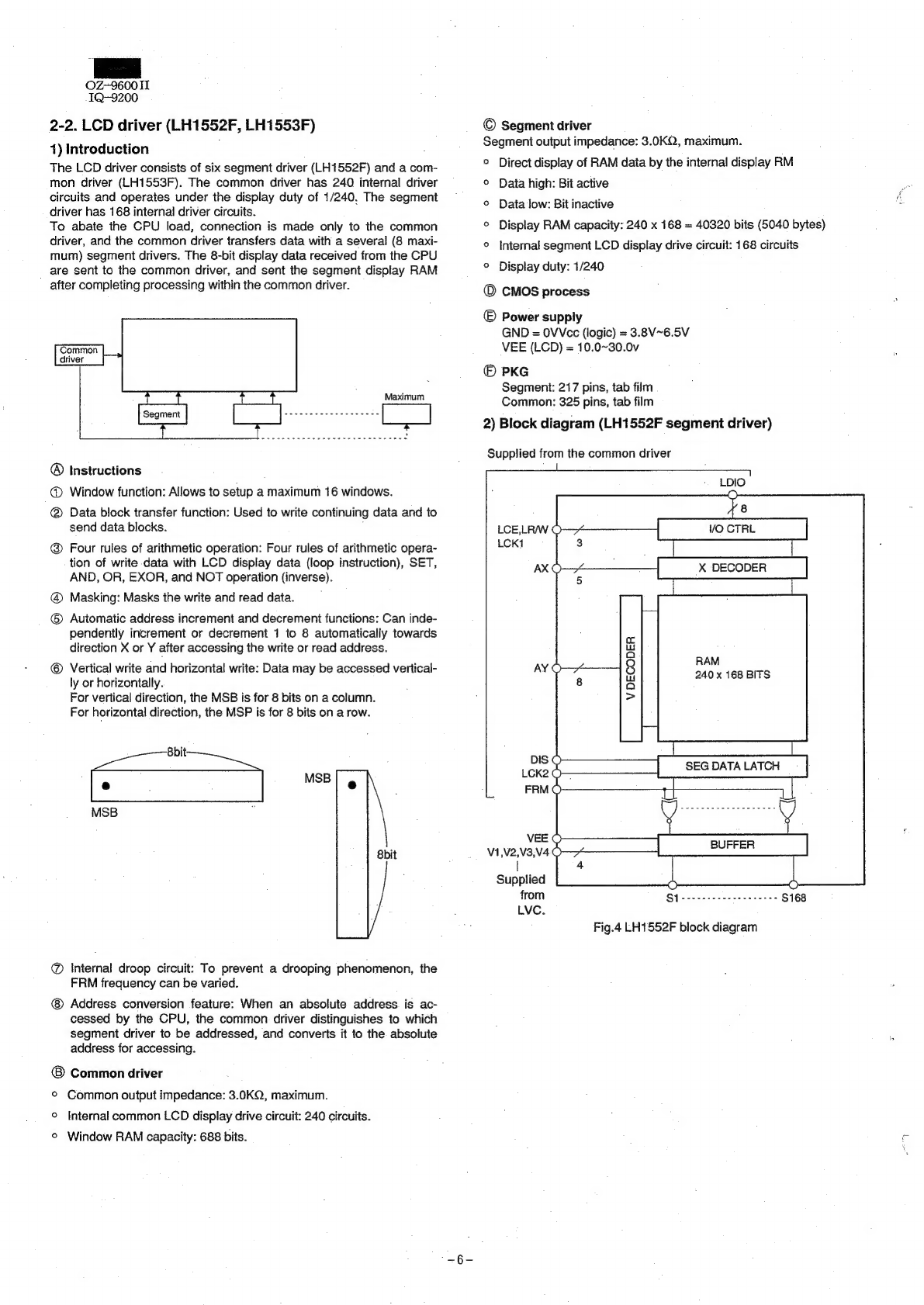

Sharp OZ-9600II User manual

Other Sharp Organizer manuals

Sharp

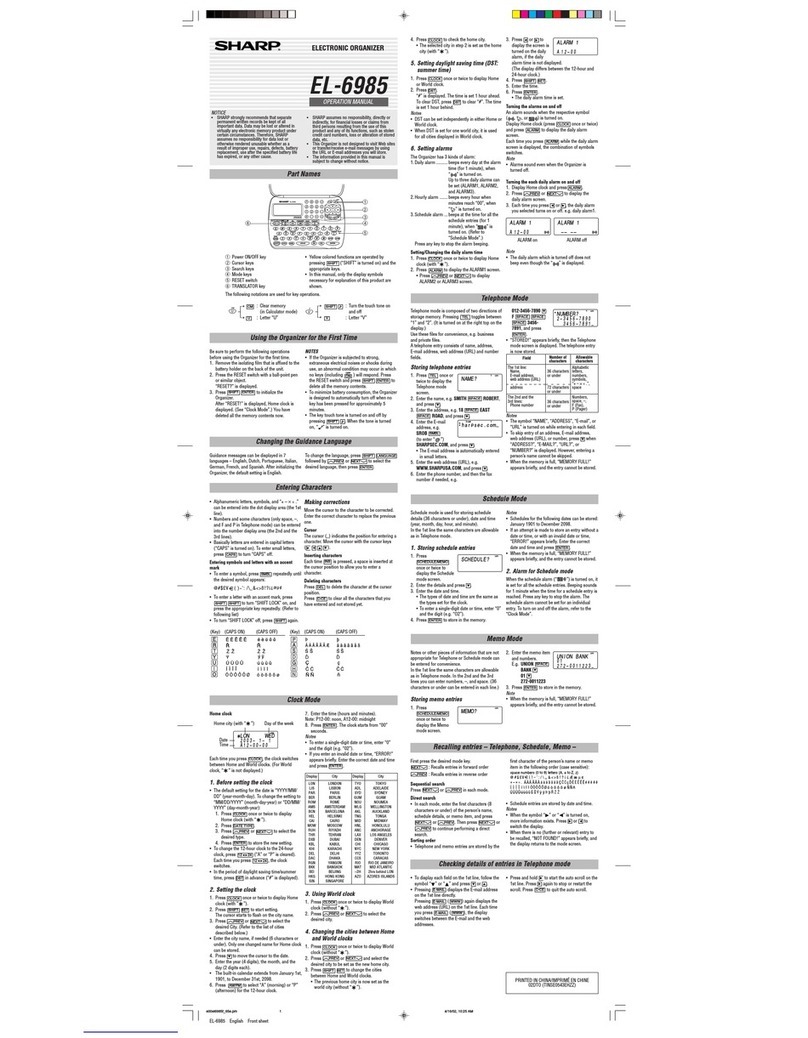

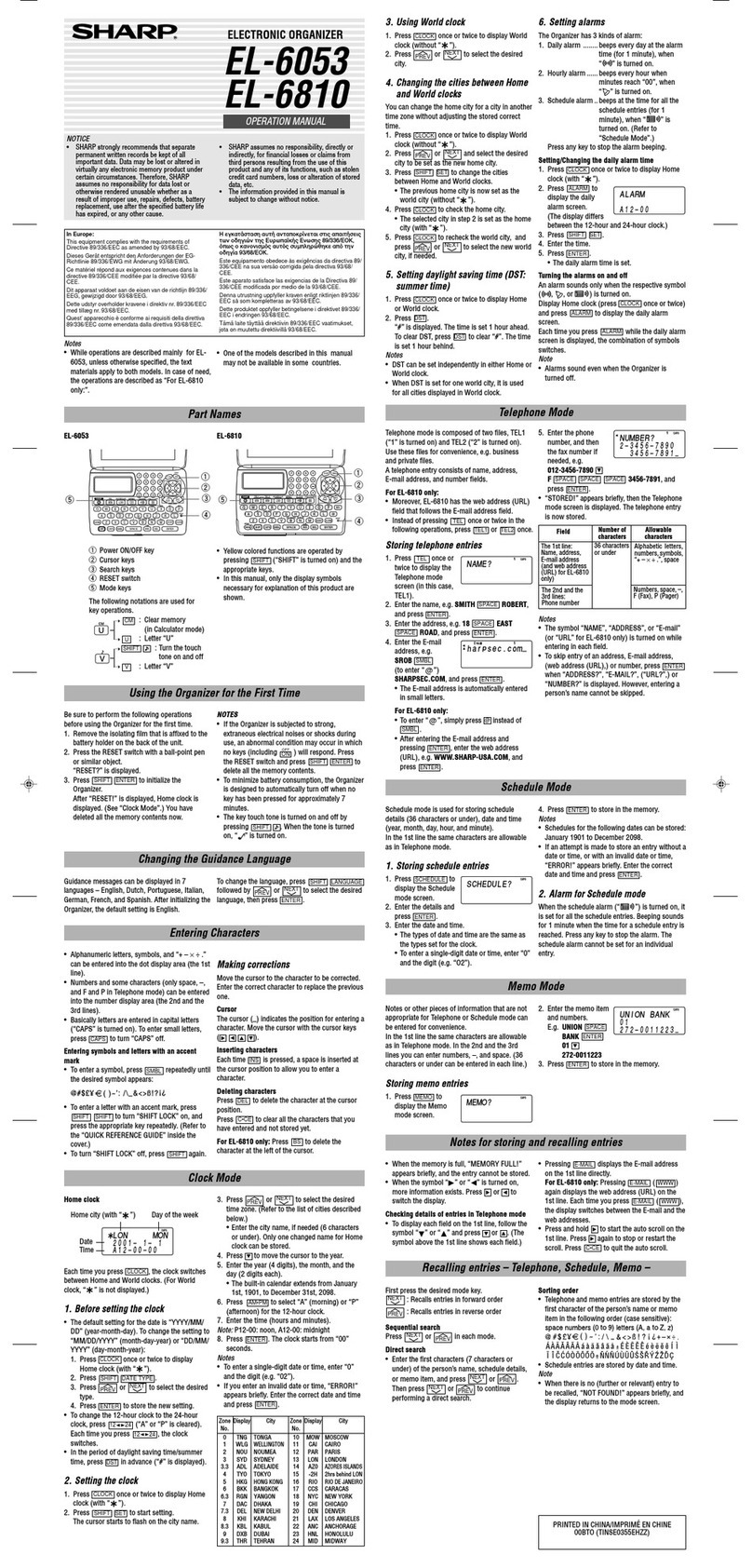

Sharp EL-6710S User manual

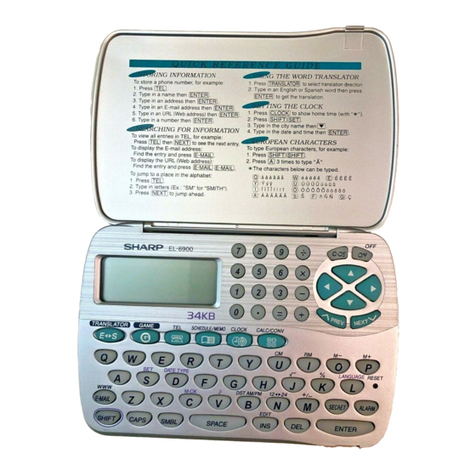

Sharp

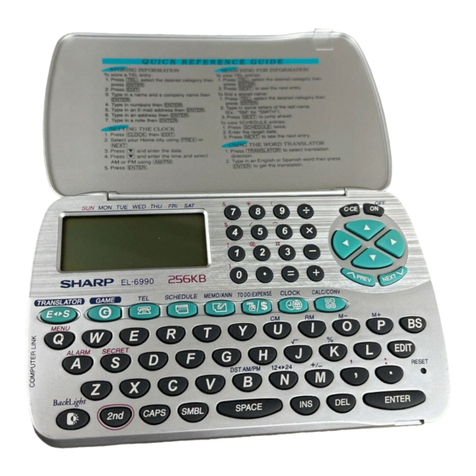

Sharp EL-6900 User manual

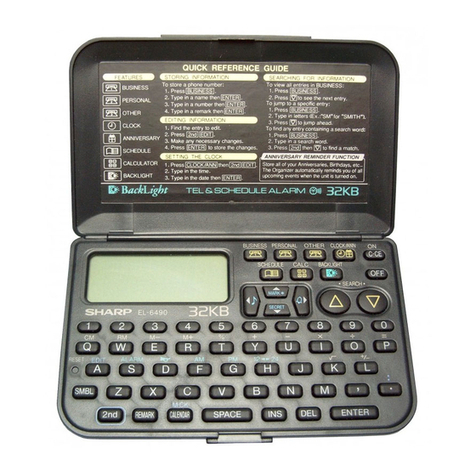

Sharp

Sharp EL-6490 User manual

Sharp

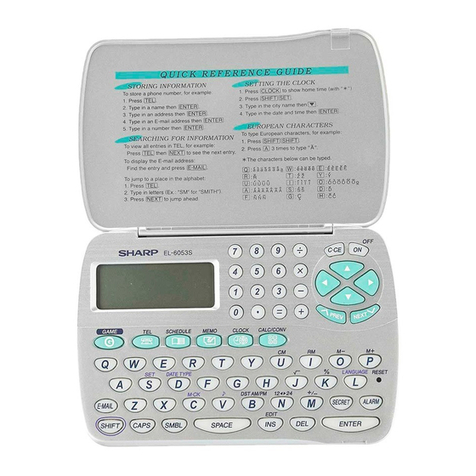

Sharp EL-6053S User manual

Sharp

Sharp YO-270 User manual

Sharp

Sharp EL-6420 User manual

Sharp

Sharp IQ-7600 User manual

Sharp

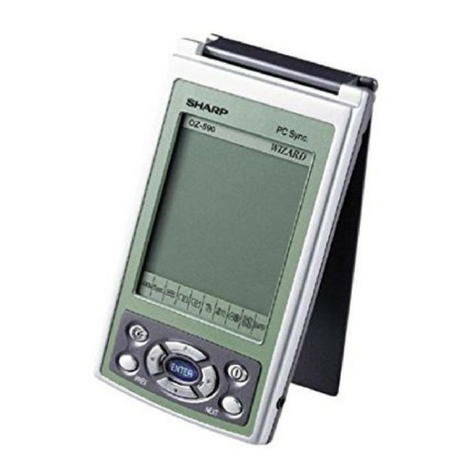

Sharp Wizard OZ-590A User manual

Sharp

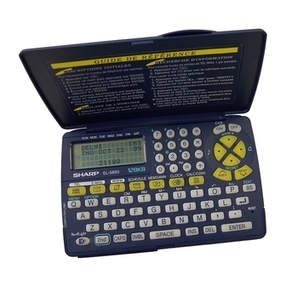

Sharp EL-6850 User manual

Sharp

Sharp ZQ-2400 User manual