Sony MDX-C7970 User manual

Other Sony Car Receiver manuals

Sony

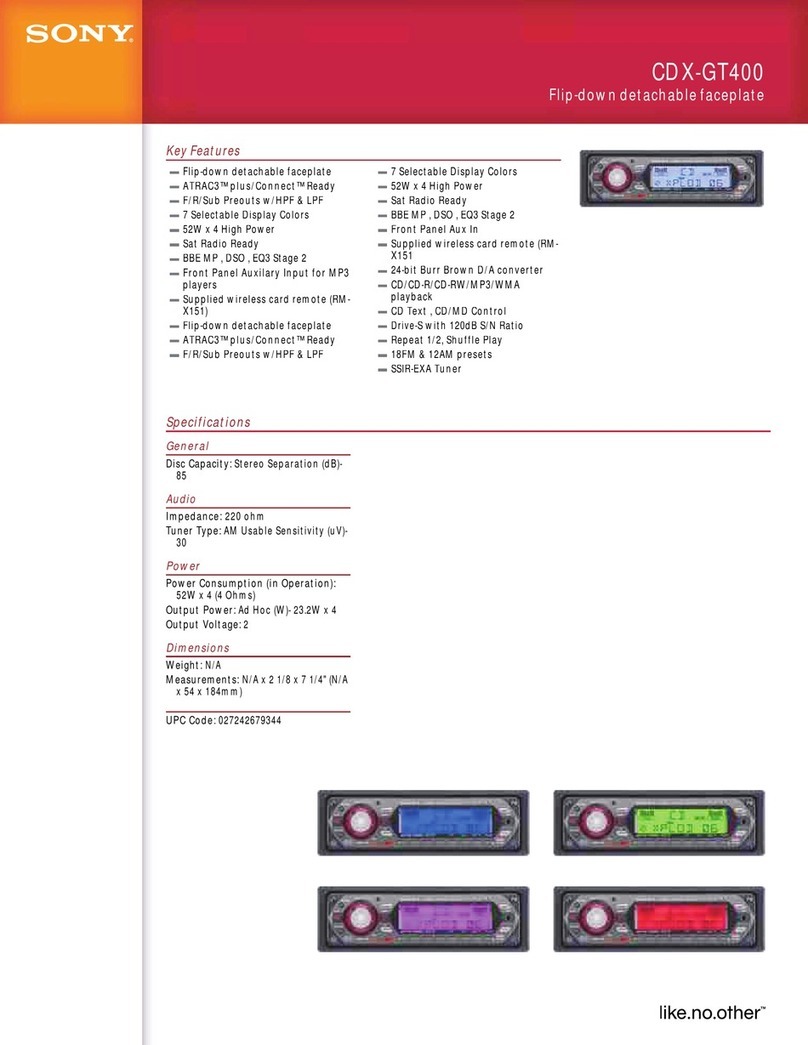

Sony CDX-GT400 - Fm/am Compact Disc Player User manual

Sony

Sony XAV-701BT Product guide

Sony

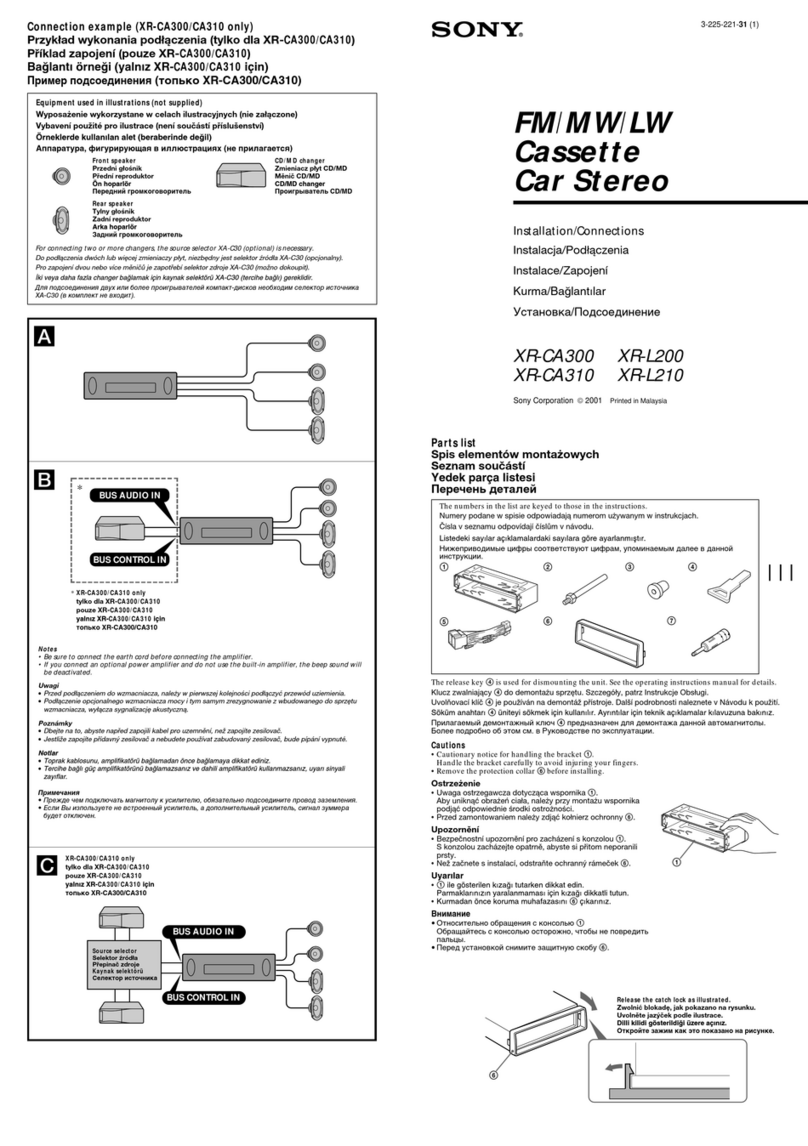

Sony XR-CA300 - Fm-am Cassette Car Stereo Product guide

Sony

Sony XR-2800 User manual

Sony

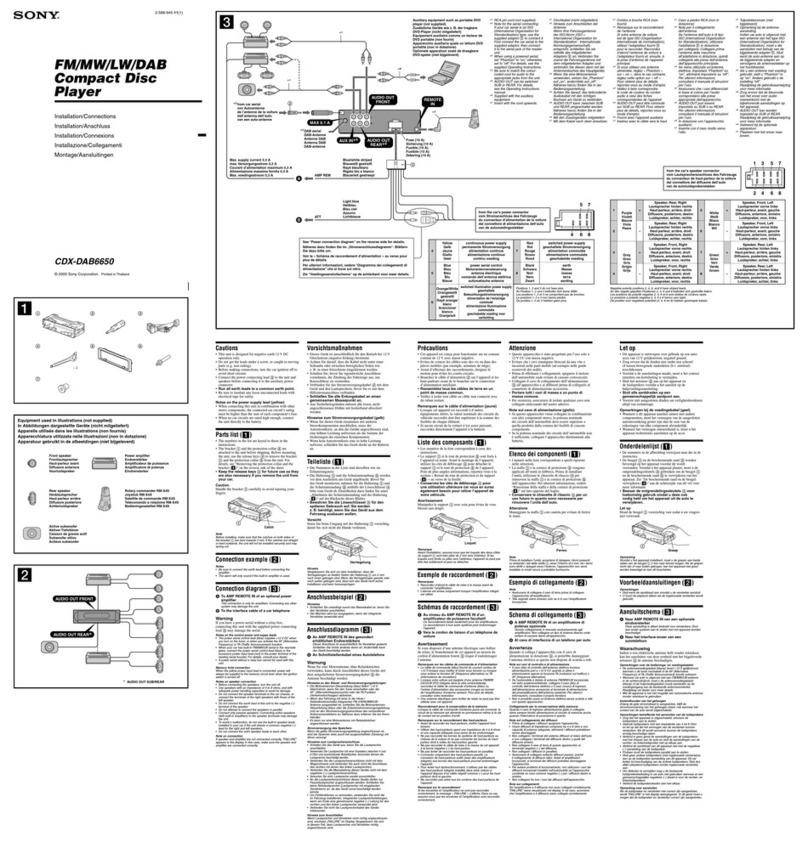

Sony CDX-DAB6650 Product guide

Sony

Sony CDX-CA860X Primary User Manual (English User manual

Sony

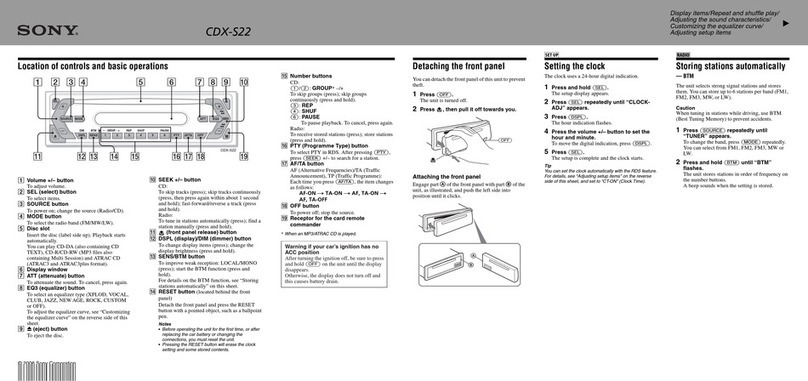

Sony CDX-S22 User manual

Sony

Sony HCD-RG66T User manual

Sony

Sony HCD-HX50BTR User manual

Sony

Sony XR-C102 Product guide

Sony

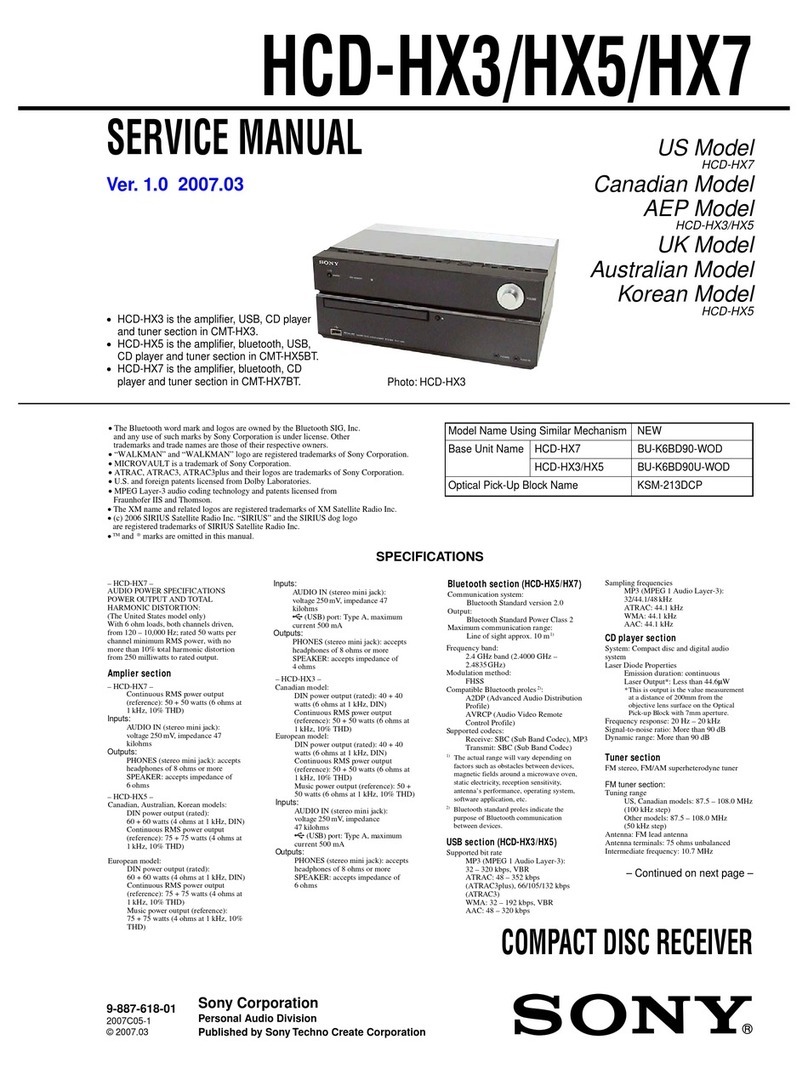

Sony HCD-HX7 - Compact Disc Receiver User manual

Sony

Sony XR-C6210R User manual

Sony

Sony CDX-CA580X Product guide

Sony

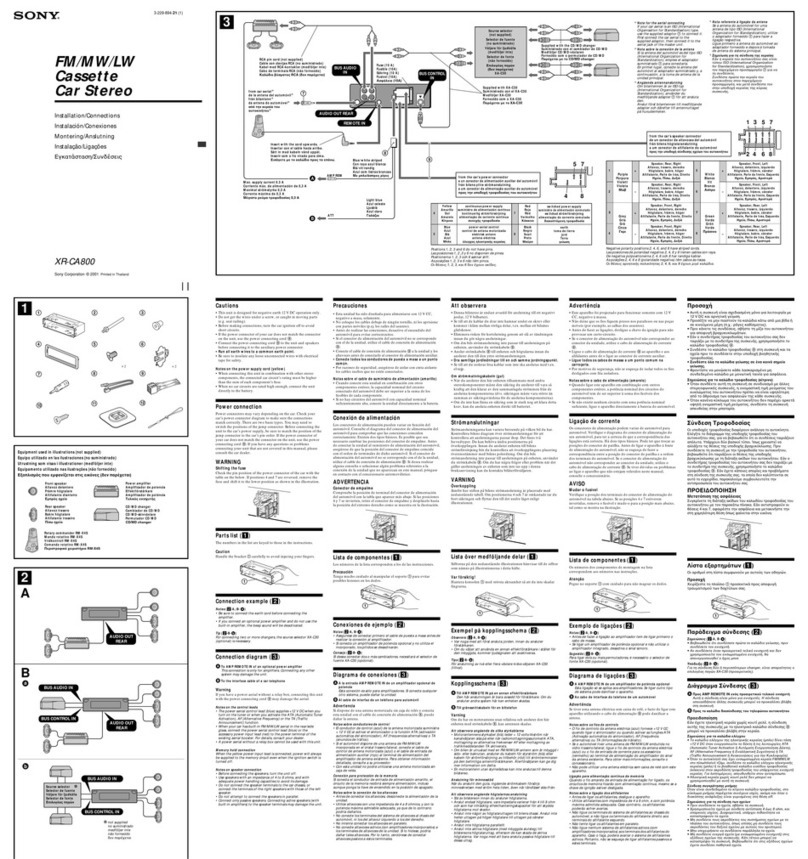

Sony XR-CA800 Product guide

Sony

Sony XR-C7500R User manual

Sony

Sony XR-CA660X User manual

Sony

Sony CDX-GT424U User manual

Sony

Sony MEX-R5 - Multi Disc Player User manual

Sony

Sony XR-C500 Primary User manual

Sony

Sony Xplod CDX-GT430IP User manual