HOW TO USE THIS MANUAL

4.1 Installation Procedures ........................................................................................................4-1

4.2 Unpack the Board................................................................................................................4-1

4.3 Visually Inspect the Board...................................................................................................4-1

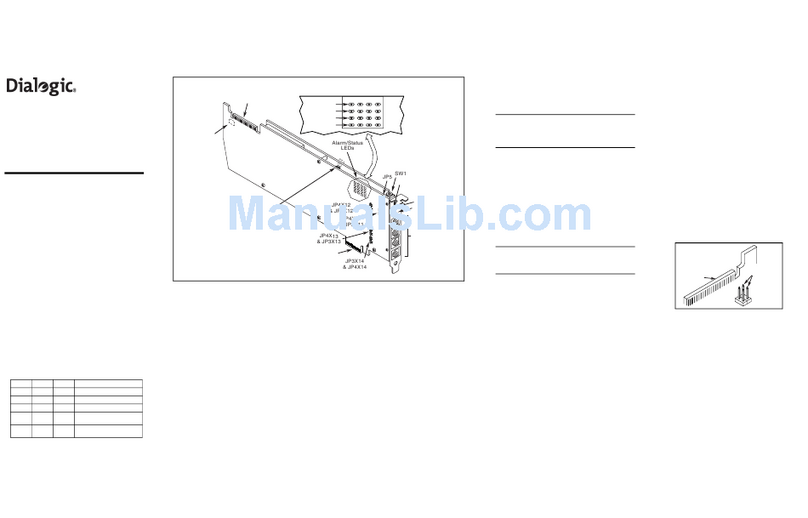

4.3.1 DEC-specific Board...........................................................................................4-3

4.3.2 Non-specific Board............................................................................................4-3

4.4 External Configuration ........................................................................................................4-3

4.4.1 Set/Verify EEPROM Jumpers............................................................................4-3

4.5 Install the Board..................................................................................................................4-4

4.6 Cabling...............................................................................................................................4-5

4.6.1 Fiber-optic configuration ...................................................................................4-5

4.6.2 Fiber-optic cables ..............................................................................................4-5

4.6.3 Fiber-optic connection .......................................................................................4-6

4.7 Auxiliary Connection ..........................................................................................................4-7

4.8 Internal Configuration .........................................................................................................4-7

4.8.1 SCRAMNet+ SC150 Control/Status Registers (CSR) .........................................4-7

4.8.2 EEPROM Initialization......................................................................................4-9

4.8.3 Node Identification............................................................................................4-9

4.8.4 Network Time-out ...........................................................................................4-10

4.8.5 Memory Addressing ........................................................................................4-10

4.8.6 Shared Memory...............................................................................................4-10

4.9 Byte Swapping..................................................................................................................4-10

4.10 Passive PMC Cabinet Kit.................................................................................................4-11

4.11 Maintenance....................................................................................................................4-11

4.12 Troubleshooting ..............................................................................................................4-11

4.12.1 Hardware ......................................................................................................4-11

4.12.2 Customer Support..........................................................................................4-11

5. OPERATION.......................................................................................................................................5-1

5.1 Introduction ........................................................................................................................5-1

5.2 Shared Memory...................................................................................................................5-1

5.2.1 Virtual Paging ...................................................................................................5-1

5.2.2 Memory Considerations.....................................................................................5-3

5.2.3 Control/Status Registers.....................................................................................5-3

5.3 Initialization........................................................................................................................5-3

5.4 Basic Send/Receive Configuration .......................................................................................5-4

5.5 Network Ring......................................................................................................................5-4

5.5.1 Message Contents..............................................................................................5-4

5.5.2 Protocol ............................................................................................................5-5

5.5.3 Performance......................................................................................................5-6

5.5.4 Throughput .......................................................................................................5-7

5.6 Auxiliary Control RAM.......................................................................................................5-8

5.7 Interrupt Controls................................................................................................................5-9

5.7.1 Interrupt Options ...............................................................................................5-9

5.8 Interrupt Conditions ..........................................................................................................5-10

5.8.1 Network Data write .........................................................................................5-10

5.8.2 Network Error .................................................................................................5-14

5.8.3 Interrupt Handling...........................................................................................5-15

5.9 External Triggers...............................................................................................................5-15

5.10 General Purpose Counter/Timer.......................................................................................5-15

5.10.1 Available Modes............................................................................................5-16

5.10.2 Rollover/Reset...............................................................................................5-16

5.10.3 Presetting Values...........................................................................................5-16

5.11 Modes of Operation.........................................................................................................5-17

5.11.1 Data Filter .....................................................................................................5-17

5.11.2 HIPRO Mode ................................................................................................5-17

5.11.3 Loopback Modes ...........................................................................................5-19

5.11.4 Holdoff Mode................................................................................................5-25

5.11.5 Write-Me-Last Mode.....................................................................................5-27

5.12 Quad Switch....................................................................................................................5-27

Copyright 2003 ii SC150 PMC H/W REFERENCE