Operating Instructions—DD 501

applied to atrigger circuit where they are converted to

pulses of uniform amplitude and shape. This makes it

possible to start the delay with apulse that has aconstant

size, eliminating variations of the delay circuit operation

caused by changing input signals. The trigger controls

provide ameans to select the START and EVENT pulses at

any voltage level on either slope of the waveform.

The trigger SLOPE and LEVEL controls determine the

slope and voltage of the input signal where the trigger

circuit responds. Generally, the best point on awaveform

for triggering is where the slope is steep, and therefore

usually free of noise. Assuming asine-wave input

waveform, the steepest slope occurs at the zero-crossing

point. This is the point selected for triggering with the

LEVEL control is set to 0(center). Amore positive or

negative point on the waveform is selected as the LEVEL

control is rotated clockwise or counterclockwise respec-

tively from 0(toward +or -symbols on panel).

Before setting the trigger level, the desired slope

should be selected. Adjust the START LEVEL control to

the desired start trigger point. Then adjust the EVENTS

LEVEL control to trigger the events pulse either

simultaneously or after the start trigger pulse. The

relationship between start and events triggering is

monitored at the START and EVENTS TRIG VIEW con-

nectors.

Either LEVEL control can be preset to afixed voltage

level by adjusting the front-panel PRESET adjustment.

Rotate either LEVEL control fully clockwise (into the

detent), and set the PRESET screwdriver adjustment to

the desired triggering voltage level.

Counted Burst

This application permits preselecting the number of

output pulses from the PG 508. The event is initiated by an

externally applied signal or pulse, 5ns or longer. The time

duration of this signal or pulse has no effect on the output

from the PG 508.

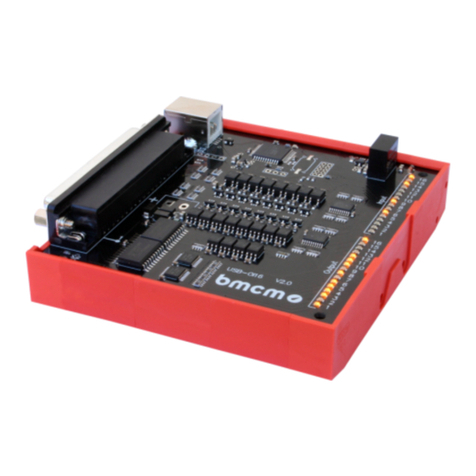

To use this feature, place the DD 501 in the delay

interval mode of operation by moving the wire strap as

shown in Fig. 1-2 or changing connections, depending on

the DD 501 available. Connect the PG 508 and the DD 501

as shown in Fig. 1-3. Use ten inch or shorter cables for

interconnecting the two units to reduce delays.

Make certain the PG 508 TRIG/GATE IN input

impedance is set for 50 fi. Set the controls of the PG 508

for the desired output waveform with the PG 508 in FREE

RUN. Do not use the SQ WAVE mode. Place the PG 508 in

the +SLOPE, SYNC GATE mode and set the TRIG/GATE

LEVEL control at the 2o’clock position. Select EVENTS +

SLOPE, START -f SLOPE and place the EVENTS and

START LEVEL controls at the 2o’clock position on the

DD 501. The three TRIG’D lights on the DD 501 and the

TRIG’D/GATED light on the PG 508 will be off until the

DD 501 istriggered. Upon receipt ofatrigger, all lights will

illuminate. If not, check the setup and slightly adjust the

LEVEL controls as necessary.

Set the EVENTS DELAY COUNT on the DD 501 for one

less than the desired number of counts up to PG 508

repetition rates of about 20 MHz. See below for further

information. If necessary, asingletriggermay beobtained

by rotating the DD 501 START LEVEL control throughthe

0position, with no external trigger applied. Asingle trigger

may also be obtained by using the TEKTRONIX manual

(One Shot) Trigger Generator, Tektronix Part Number

016-0597-00. All other DD 501 and PG 508 operating

controls function normally.

"S’

2

^

I

WE

ifl

|gi

aQaEHui

00HQS0B.

Connect pins 1and 3for delay interval out for counted burst. Pins 1and 2provide normal delayed trigger out.

2044-29

Fig. 1-2. Location of trigger jumpers in DD 501 for selecting trigger or delay interval output.

1-2 REV BAUG 1979