User’s Guide

Using the UCC14141EVM-068 for Biasing Traction Inverter

Gate Driver ICs Requiring Single, Positive or Dual,

Positive/Negative Bias Power

ABSTRACT

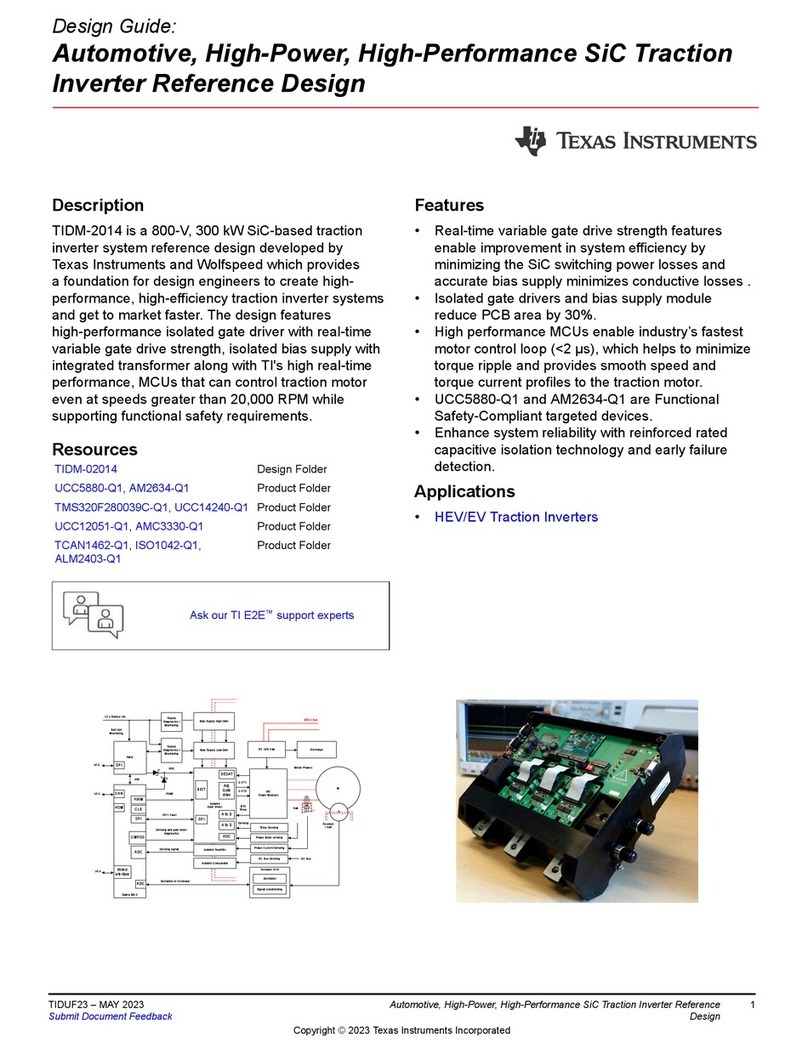

This user’s guide provides a description as well as directions for use of the UCC14141EVM-068 to evaluate the

UCC14141-Q1, high frequency, integrated transformer, DC-DC converter module from Texas Instruments. This

EVM allows designers to quickly and efficiently evaluate the UCC14141-Q1 for use in automotive or industrial

applications requiring gate driver IC bias power as high as 1.5 W, meeting up to 5-kVRMS isolation.

Table of Contents

1 Introduction.............................................................................................................................................................................2

1.1 Pin Configuration and Functions........................................................................................................................................ 2

2 Description.............................................................................................................................................................................. 4

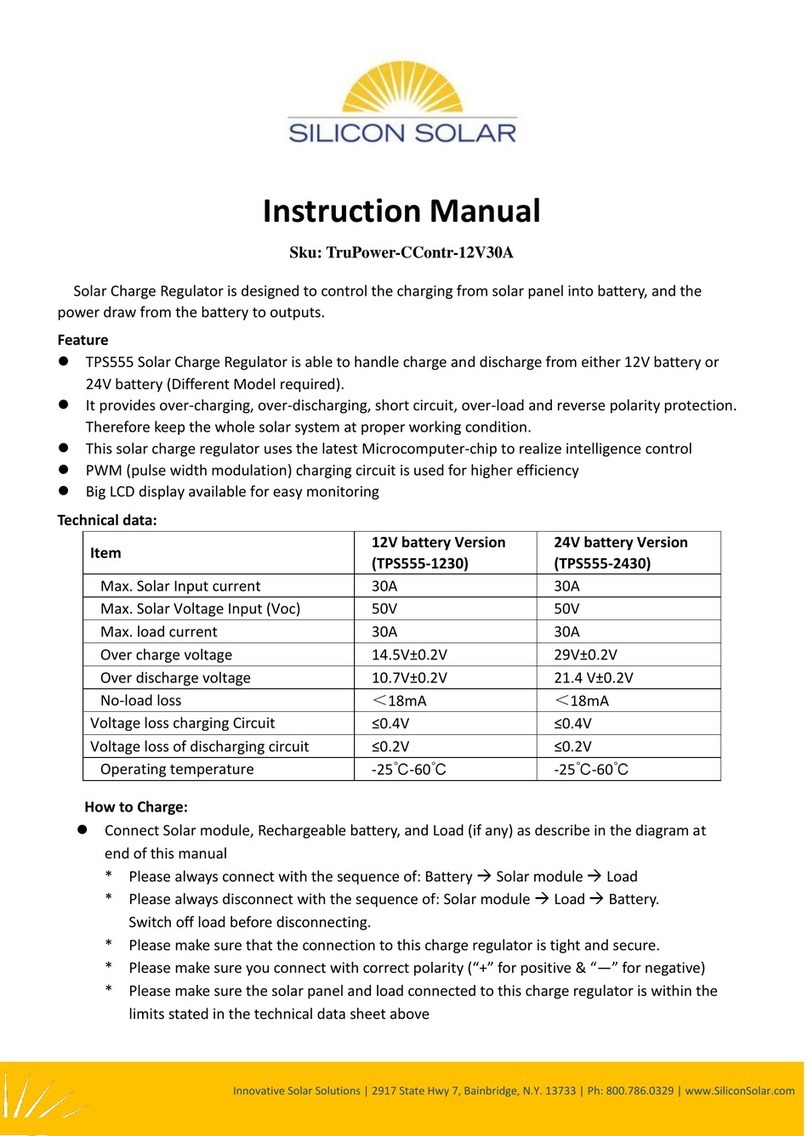

2.1 EVM Electrical Performance Specifications....................................................................................................................... 5

3 Schematic................................................................................................................................................................................6

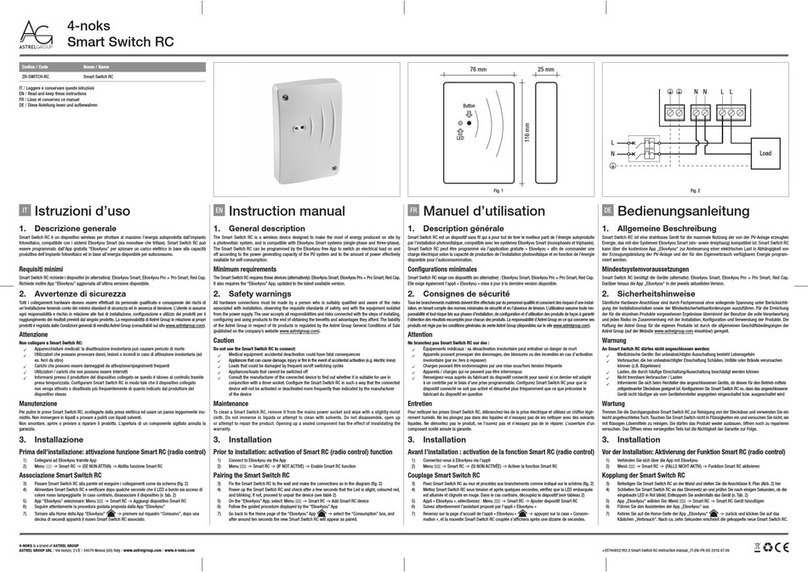

4 EVM Setup and Operation......................................................................................................................................................7

4.1 Recommended Test Equipment......................................................................................................................................... 7

4.2 External Connections for Easy Evaluation......................................................................................................................... 7

4.3 Powering the EVM............................................................................................................................................................. 8

4.4 EVM Test Points.................................................................................................................................................................9

4.5 Probing the EVM.............................................................................................................................................................. 10

5 Performance Data ................................................................................................................................................................ 11

5.1 Efficiency Data..................................................................................................................................................................11

5.2 Regulation Data............................................................................................................................................................... 13

5.3 Steady State Input Current...............................................................................................................................................14

5.4 Start-up Waveforms......................................................................................................................................................... 14

5.5 Inrush Current.................................................................................................................................................................. 16

5.6 AC Ripple Voltage............................................................................................................................................................ 18

5.7 EN-to-/PG Timing.............................................................................................................................................................21

5.8 RLIM.................................................................................................................................................................................21

5.9 Fault Protection .............................................................................................................................................................23

5.10 Shutdown....................................................................................................................................................................... 25

5.11 Thermal Performance.....................................................................................................................................................26

6 Assembly and Printed Circuit Board (PCB) Layers...........................................................................................................27

7 Bill of Materials (BOM)..........................................................................................................................................................30

8 Revision History................................................................................................................................................................... 30

Trademarks

All trademarks are the property of their respective owners.

www.ti.com Table of Contents

SLUUCS5 – FEBRUARY 2023

Submit Document Feedback

Using the UCC14141EVM-068 for Biasing Traction Inverter Gate Driver ICs

Requiring Single, Positive or Dual, Positive/Negative Bias Power

1

Copyright © 2023 Texas Instruments Incorporated