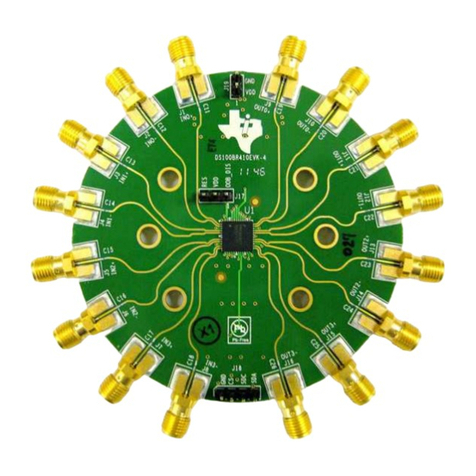

3.2.3 Programming Interfaces (J18, J17)

3.2.4 Flexible Crystal, Differential or LVCMOS Input (J3, J6)

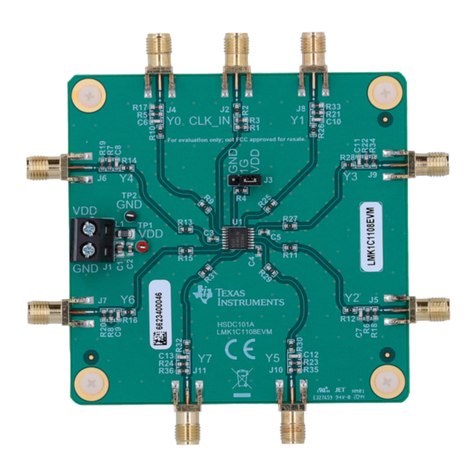

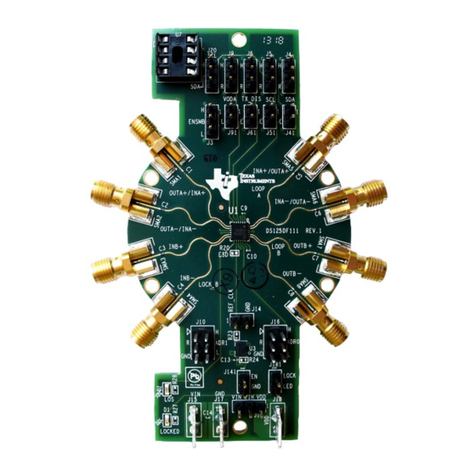

3.2.5 LVCMOS Outputs (Y0 –Y5)

EVM Hardware

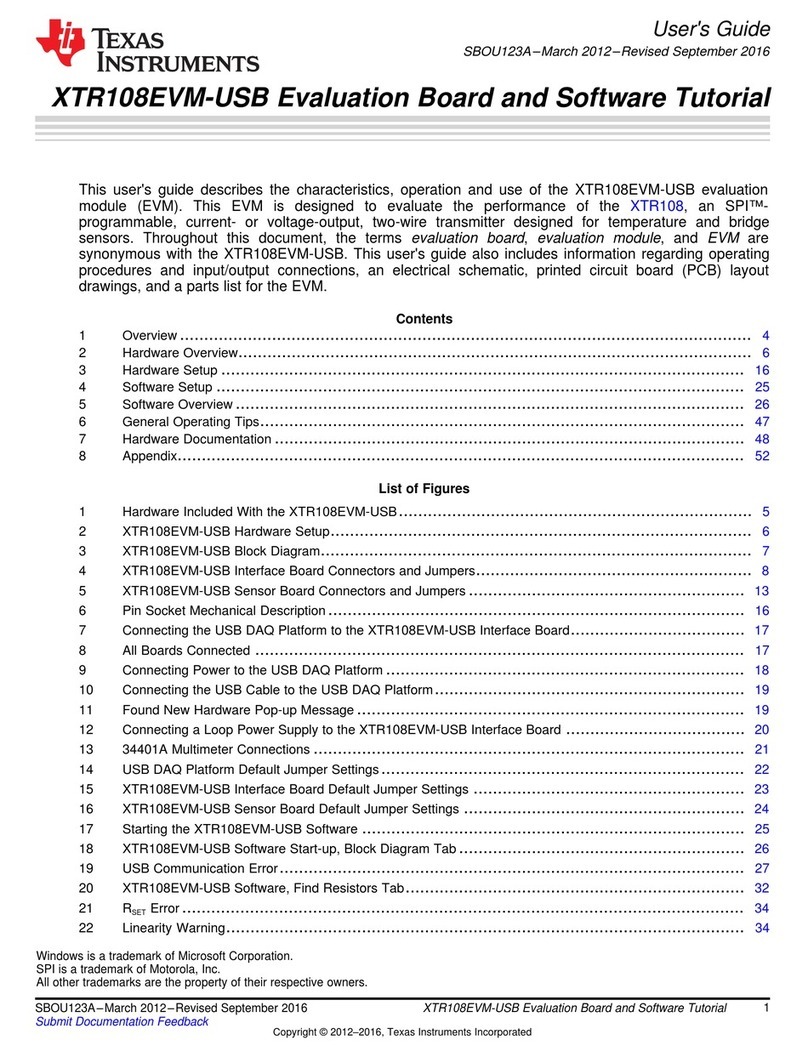

To enhance the flexibility and function of the clock synthesizer, a two-signal serial interface is provided. Itfollows the SMBus specification Version 2.0, which is based upon the principals of operation of I

2

C. Moredetails of the SMBus specification can be found at http://www.smbus.org .

Through the SMBus, various device functions, such as individual clock output buffers, can be individuallyenabled or disabled. The registers associated with the SMBus data interface initialize to their defaultsetting, written in the EEPROM, upon power-up and therefore using this interface is optional. Clock deviceregister changes are normally made upon system initialization, if any are required. There are two ways toprogram the device externally.•Connect the parallel port cable to PC and EVM parallel port. This needs the TI Pro Clock™ Software(see section 4).•By external pattern generator connected to J17 (it is not possible to detect an acknowledge at J17)

Note: The shield of the parallel cable should be connected to both cable plugs.

The CDCE906/CDCE706 can use a crystal, a differential clock, or a single-ended clock as reference. Thedefault setting is a 27MHz crystal.

For a differential or a single-ended clock R2, R4, R5, and R6 must be assembled with 100 Ω, pin 2 and 3of J4 and pin 1 and pin 2 of J5 must be shorted. This will assure correct biasing and results in a 50 Ωparallel termination at the CDCE906/CDCE706 input. The assembly of R3 and R7 is not necessary. Asingle-ended clock can then be applied to J3 or J6. A differential-ended clock must be applied to J3 andJ6.

Default settings: 27-MHz Crystal

The CDCE906/CDCE706 drives up to six LVCMOS outputs. All outputs are ac-coupled and have a 0- Ωseries termination resistor. The device output’s trace impedance is 50 Ωand all traces are matched inlength. The output has additional resistor and capacitor footprints to provide high flexibility for differentuser defined terminations. All traces have option for pull-up, pull-down resistors and on board dc-biasing.

There is no additional load on the EVM Default Setting. This provides the maximum possible swing to ascope, a spectrum analyzer, or another EVM with high impedance input, that is connected to theCDCE906/E706 performance EVM. However, the output load is too low if Y0–Y5 is connected directly to a50 Ωparallel termination. This results in a violation of the ac-parameters mentioned in the data sheet.

To maintain the ac-parameters by connecting 50 Ωto Y0–Y5 a voltage divider is needed to provide asufficient output load for the LVCMOS outputs. The following steps are necessary to create the voltagedivider:

•Replace R10, R15, R25, R30, R40, and R43 with 0 Ω.•Assemble R8, R12, R23, R26, R38, and R42 with 1 k Ω.•Assemble C7, C8, C9, C10, C11, and C12 with 950 Ω.•Assemble R17, R19, R34, R35, R46, and R47 with 10 pF.

The output voltage of Y0-Y5 will be divided by 20 in this configuration. The overall ac load to GND will be500 Ω//10 pF if the input impedance of the measurement equipment is 50 Ω.

Alternative R10, R15, R25, R30, R40, and R43 can be replaced with 450 Ωto provide 500 Ωto GND. Theoutput voltage of Y0–Y5 will be divided by 10, if the input impedance of the measurement equipment is 50Ω.

CDCE906/CDCE706 Performance Evaluation Module10 SCAU016B – August 2006 – Revised August 2007Submit Documentation Feedback