Texas Instruments TPS7H4002EVM-CVAL User manual

Other Texas Instruments Motherboard manuals

Texas Instruments

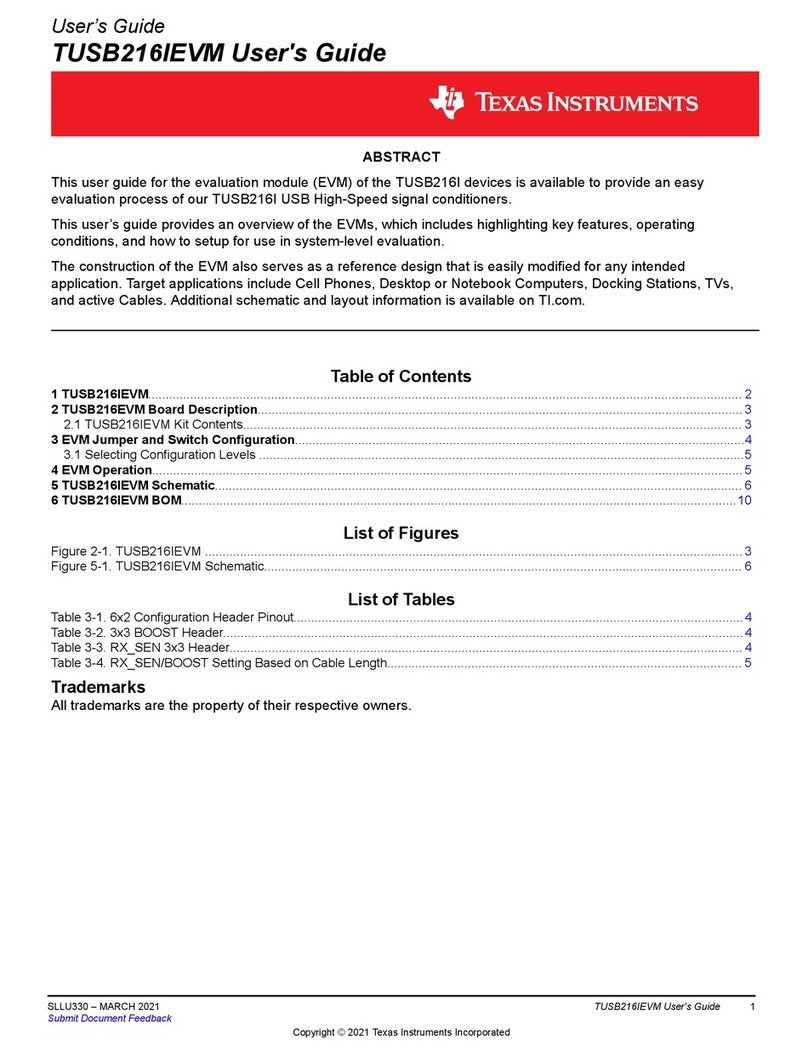

Texas Instruments TUSB216IEVM User manual

Texas Instruments

Texas Instruments DEM-PCM2900 EVM User manual

Texas Instruments

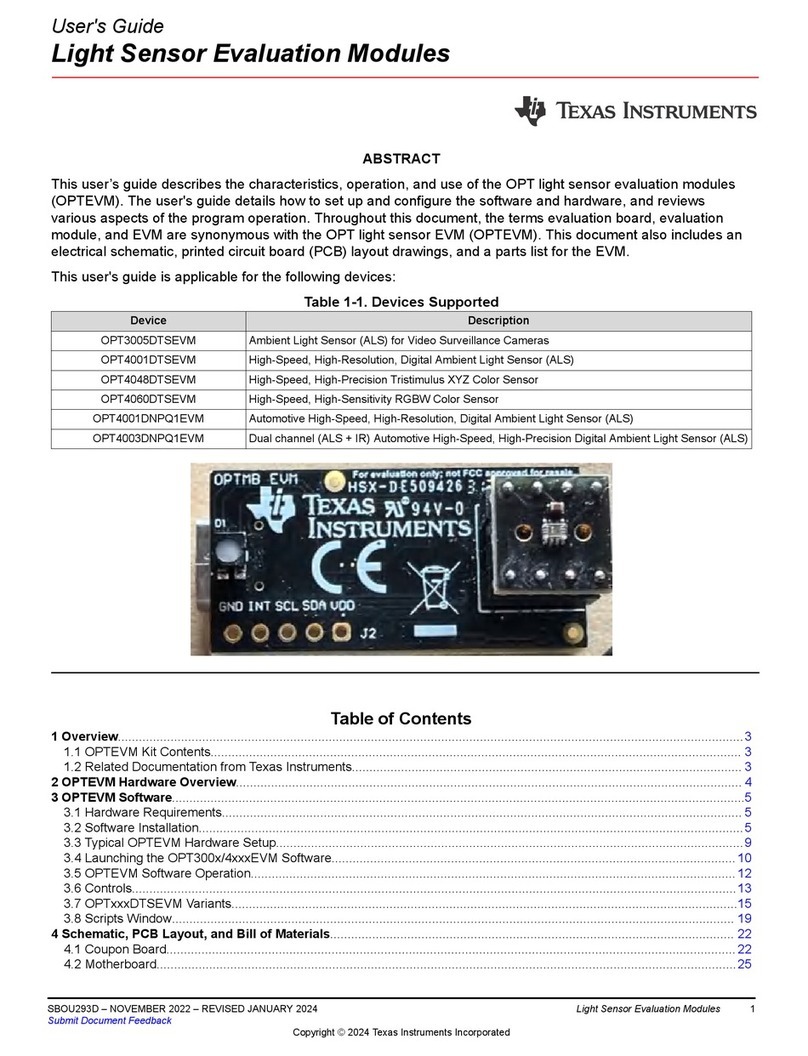

Texas Instruments OPT4060DTSEVM User manual

Texas Instruments

Texas Instruments ADCx140EVM-PDK Series User manual

Texas Instruments

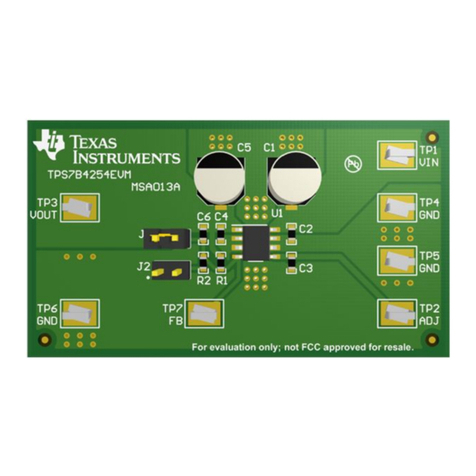

Texas Instruments TPS7B4254-Q1 User manual

Texas Instruments

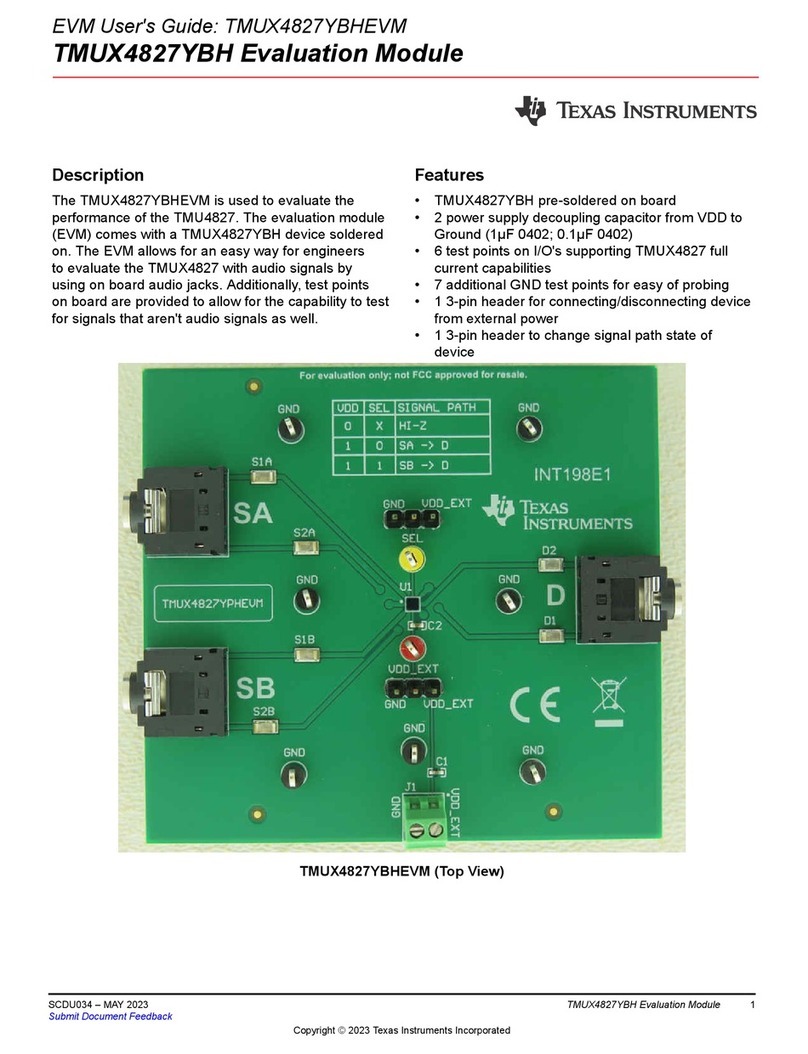

Texas Instruments TMUX4827YBHEVM User manual

Texas Instruments

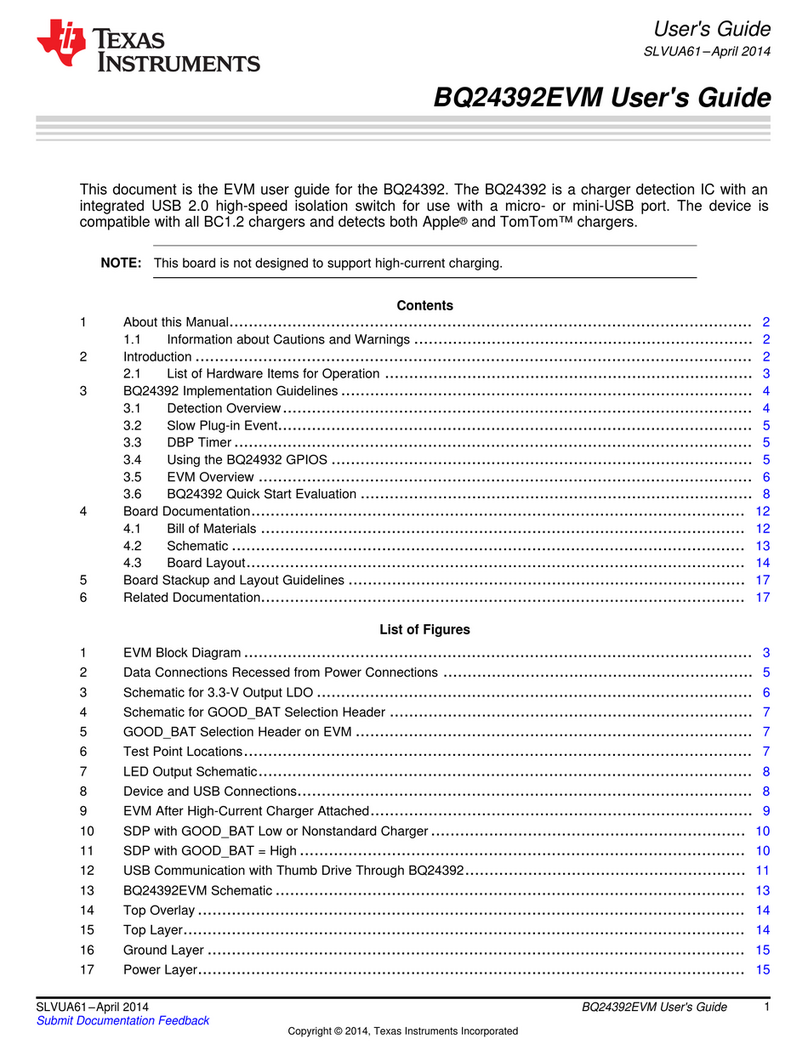

Texas Instruments BQ24392EVM User manual

Texas Instruments

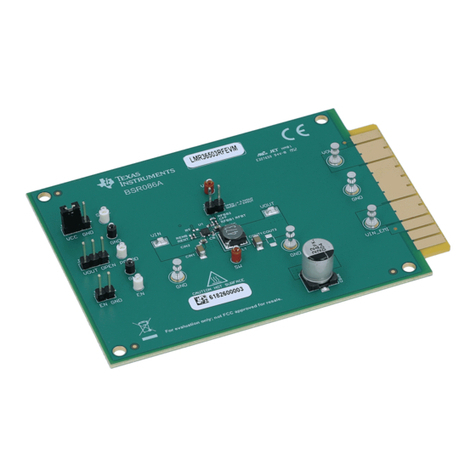

Texas Instruments LMR36503RFEVM User manual

Texas Instruments

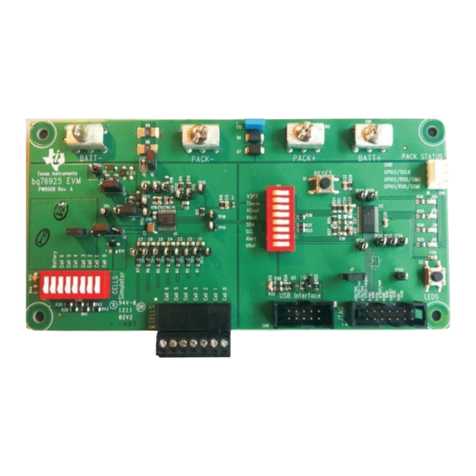

Texas Instruments bq76925EVM User manual

Texas Instruments

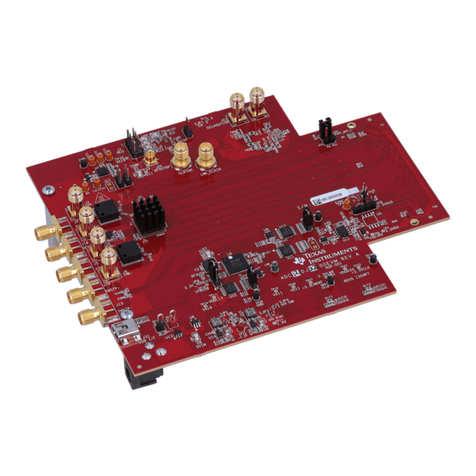

Texas Instruments ADC DJ Series User manual

Texas Instruments

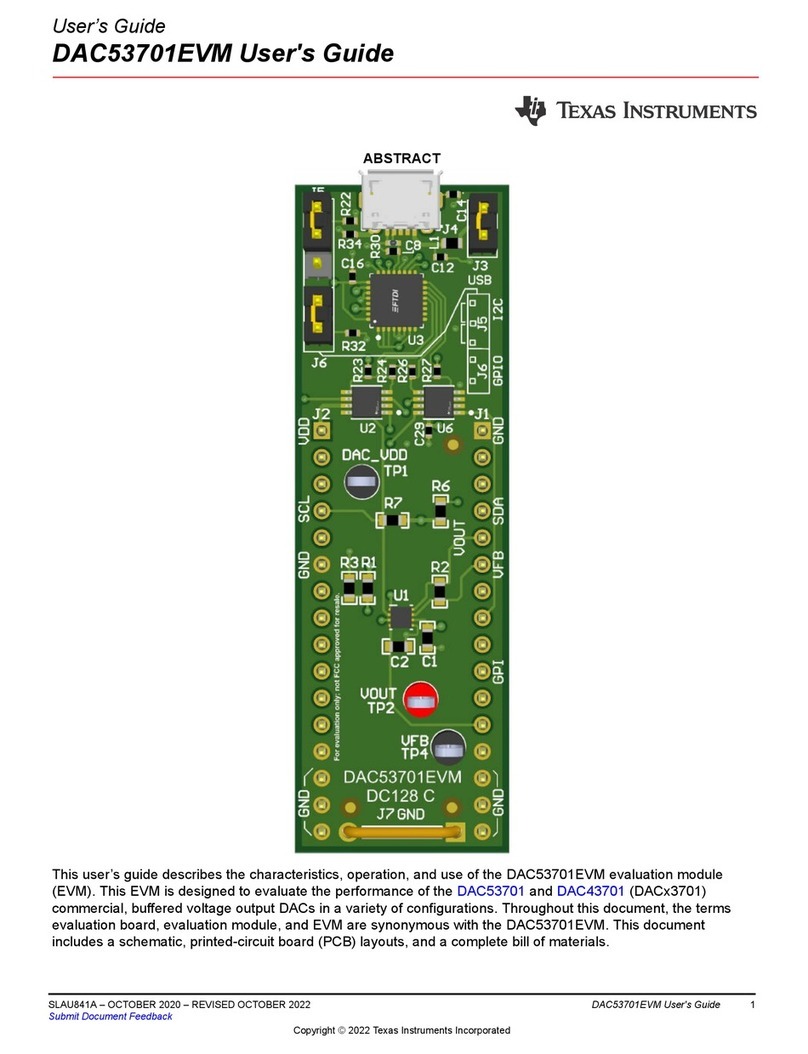

Texas Instruments DAC53701EVM User manual

Texas Instruments

Texas Instruments ADS5560EVM User manual

Texas Instruments

Texas Instruments BQ25616 User manual

Texas Instruments

Texas Instruments ADS7809 User manual

Texas Instruments

Texas Instruments LP87561Q1 User manual

Texas Instruments

Texas Instruments LMX2485E-EVM User manual

Texas Instruments

Texas Instruments PGA309EVM-USB User manual

Texas Instruments

Texas Instruments TPA3129D2EVM User manual

Texas Instruments

Texas Instruments bq76200 User manual

Texas Instruments

Texas Instruments TPS40400EVM-351 User manual